当前位置:网站首页>Chapter 7 behavior level modeling

Chapter 7 behavior level modeling

2022-07-08 01:37:00 【Jiangnan small workshop】

Chapter vii. Behavior level modeling

Preface

- Verilog Support designers from the perspective of Algorithm , That is, describe it from the perspective of the external behavior of the circuit . Behavior level modeling is to represent circuits from a high abstract point of view . At this level, it is similar C Language ,Verilog The grammatical structure of behavior level modeling and C The language is quite similar .

Structured procedure statements

- Two structured process statements :

initialandalways, Basic statements of behavior level modeling . - And C Different language ,Verilog In essence, it is concurrent and non sequential , Concurrent execution .

- Every

initialandalwaysStatement represents an independent execution process , Each execution process starts from simulation time 0 Start execution , Two statements cannot be nested .

initial

- All in

initialThe statements within the statement form ainitialblock .initialBlock slave simulation 0 Start at every moment , The whole simulation process is only executed once . - A module has more than one

initialblock , From simulation 0 Start , Concurrent execution , Each block is independent . - There are multiple behavior statements in the block , You need to group these statements , Use

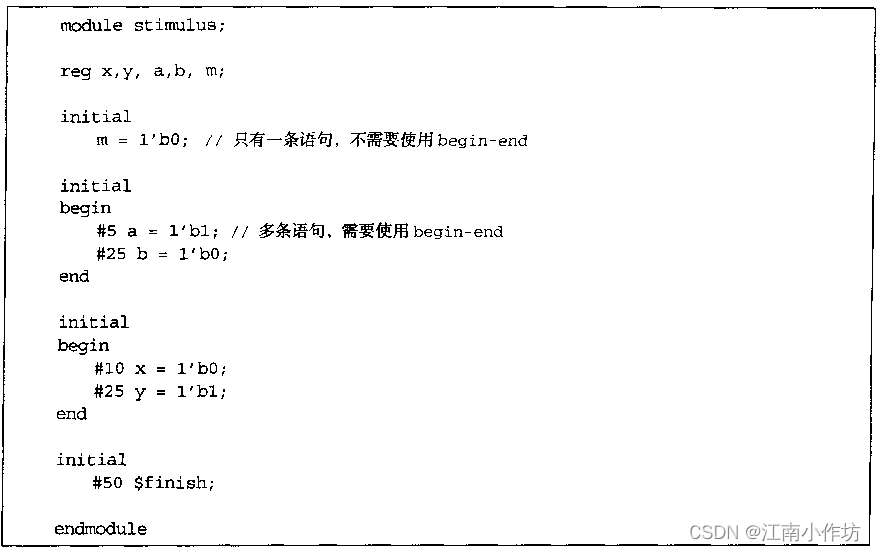

begin ... endCombine them into a block statement ; If there is only one statement in the block , You don't have to usebegin ... end. - Illustrate with examples

- Execution order

- initial Block statements can only be executed once during the entire simulation , Therefore, it is generally used to initialize 、 Signal monitoring 、 Generate simulation waveform, etc .

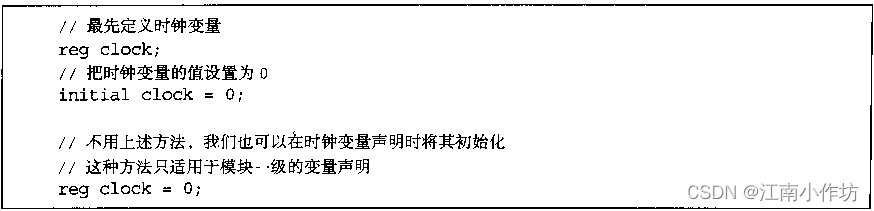

- Initialization method

Initialize while variables are declared

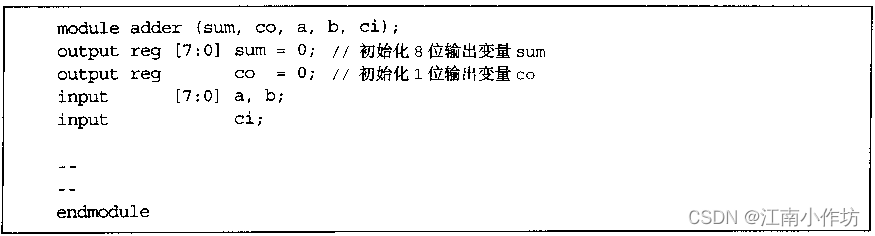

At the same time, port / Data declaration and initialization

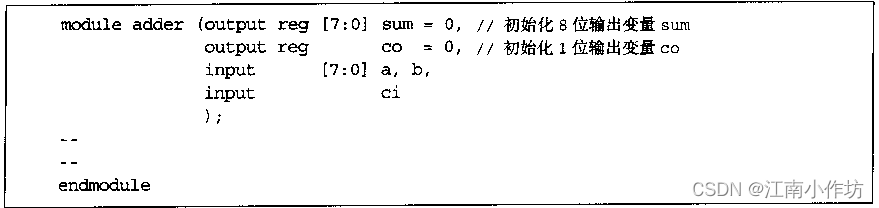

ANSI C Style Port declaration initialization

always

alwaysAll the behavior statements in the statement form aalwaysSentence block , The statement block is simulated 0 Execute the behavior statements in sequence from time to time , After the last execution is completed , Start executing the first statement again , And so on and so on , Until the end of the simulation .( Generally speaking, there are sequential statements , Very reasonable. .)alwaysStatements usually model a set of repeatedly executed activities in a circuit , Such as clock signal generator , Turn the clock signal every half a clock cycle . In real circuits, as long as the power is turned on , Clock signal generator from time 0 It works , Keep working .- Illustrate with examples

- explain :clock Signal placed on initial Statement , So only initialize once ; If you put it in always In the sentence , Every time always Statement will be initialized once , Then work endlessly . The way to stop is to cut off power (

$finish) And interrupt ($stop).

Procedure assignment statement

- The update object of procedure assignment statement is register 、 Integers 、 Real numbers or time variables . These types of variables are assigned , Its value remains unchanged , Until reassigned .

- Distinguish between continuous assignment statements : Consecutive assignment statements are always active , The change of any operand will lead to the re evaluation and re assignment of the expression , however , Procedure assignment statements only work when they are executed .

- Verilog There are two types of procedure assignment statements : Blocking and non-blocking .

Block assignment

- Assignor :

= - Blocking statements are executed sequentially , If in a begin end Block used blocking assignment , Then this block statement represents serial behavior .

- Direct example

- explain :

- Only in sentences x=0 After execution , Will execute y=1, sentence count=count+1 Execute in order at the end .

- x=0 To reg_b=reg_a The sentence between is 0 It starts at the moment ( But there is sequence ).

- 15 Time units , Start execution reg_a[2].

- 25 Time units , perform reg_b[15:13].

- sentence count=count+1 It's also 25 Time units .

- There is also register variable assignment , When the left and right seat widths are different , Left side width , Then the high position will be supplemented 0; The right width discards the high bit that exceeds the left width .

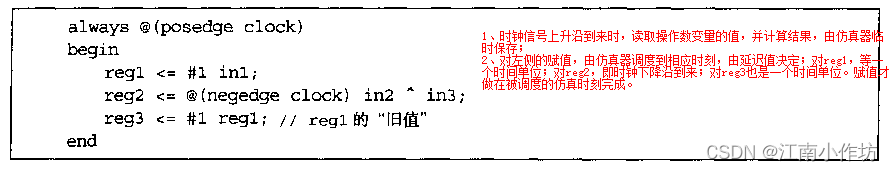

Nonblocking assignment

- Assignor :

<= - In the expression , As a relational operator ; In a non blocking environment , Assign as non blocking .

- The above example

- explain :

- The simulator schedules the blocking assignment to the corresponding time , Then continue to execute the following statements , Didn't stop to wait for the assignment to complete .

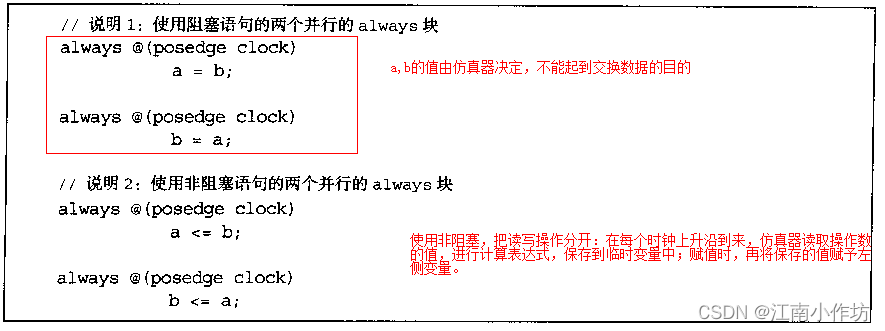

- Don't be in the same always Block mixed with blocking and non blocking assignment statements .

- application : It can be used to model common hardware circuit behavior , Such as after an event , The behavior of concurrent transmission of multiple data .

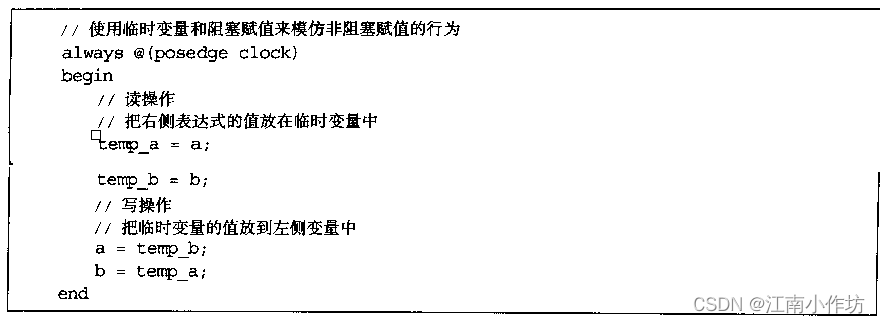

- Avoid competition

- Non blocking can be achieved by blocking

- summary

- If an event occurs, there will be concurrent transmission of multiple data , Non blocking description is recommended .

- Typical non blocking applications include : Pipeline modeling 、 Modeling of multiple mutually exclusive data transmission .

- Non blocking problem : The decrease of simulation speed 、 Memory usage increases .

Timing control

Based on the delay

Based on events

Level sensitive

Conditional statements

Multiple branch statement

Multiple branches

casex and casez

Loop statement

while loop

for loop

repeat loop

forever loop

Sequential block and parallel block

Block statement type

Block statement features

Generating block

Loop generation statement

Conditional generation statement

case Generating statement

give an example

Choose a multi-path selector

Four digit counter

Traffic light controller

Summary

边栏推荐

- 项目经理有必要考NPDP吗?我告诉你答案

- Smart agricultural technology framework

- Frequency probability and Bayesian probability

- Working principle of stm32gpio port

- break net

- QT build with built-in application framework -- Hello World -- use min GW 32bit

- Led serial communication

- 2022 operation certificate examination for main principals of hazardous chemical business units and main principals of hazardous chemical business units

- qt-使用自带的应用框架建立--hello world--使用min GW 32bit

- LeetCode 练习——剑指 Offer 36. 二叉搜索树与双向链表

猜你喜欢

5. Contrôle discret et contrôle continu

2022 safety officer-a certificate free examination questions and safety officer-a certificate mock examination

2022 high voltage electrician examination skills and high voltage electrician reexamination examination

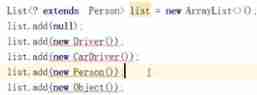

2021-03-14 - play with generics

The combination of relay and led small night light realizes the control of small night light cycle on and off

2022 tea master (intermediate) examination questions and tea master (intermediate) examination skills

nacos-微服务网关Gateway组件 +Swagger2接口生成

2022 operation certificate examination for main principals of hazardous chemical business units and main principals of hazardous chemical business units

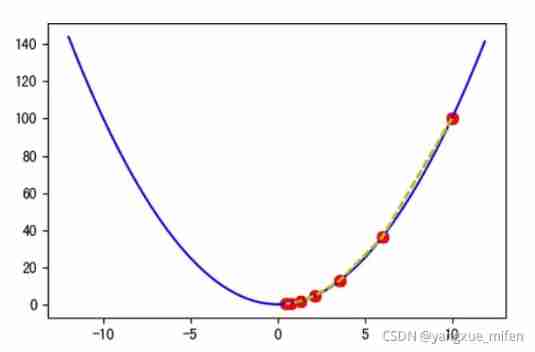

About snake equation (2)

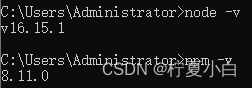

解决报错:npm WARN config global `--global`, `--local` are deprecated. Use `--location=global` instead.

随机推荐

Qt - - Packaging Programs - - Don't install Qt - can run directly

2021-03-06 - play with the application of reflection in the framework

2022 free test questions of fusion welding and thermal cutting and summary of fusion welding and thermal cutting examination

Coordinate conversion of one-dimensional array and two-dimensional matrix (storage of matrix)

QT -- package the program -- don't install qt- you can run it directly

Matlab method is good~

Matlab code about cosine similarity

2022 safety officer-c certificate examination paper and safety officer-c certificate simulated examination question bank

Continued from the previous design

Redux使用

Anaconda3 tutorial on installing and adding Tsinghua image files

Gnuradio 3.9 using OOT custom module problem record

Understanding of prior probability, posterior probability and Bayesian formula

跨模态语义关联对齐检索-图像文本匹配(Image-Text Matching)

Anaconda3 download address Tsinghua University open source software mirror station

php 获取音频时长等信息

The difference between distribution function and probability density function of random variables

Is it safe to open an account on your mobile phone for small amount of stock speculation?

How does Matplotlib generate multiple pictures in turn & only save these pictures without displaying them in the compiler

Running OFDM in gnuradio_ RX error: gr:: Log: info: packet_ headerparser_ b0 - Detected an invalid packet at item ××