当前位置:网站首页>cell delay and net delay

cell delay and net delay

2022-08-03 17:38:00 【luka cat】

1.delay analysis

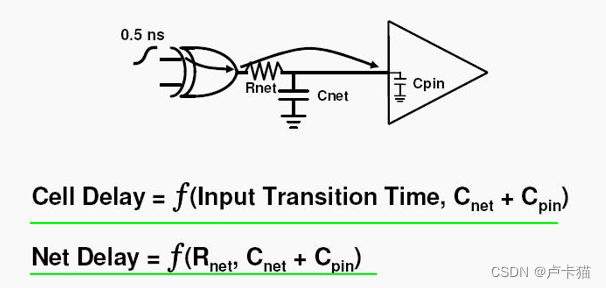

Static timing analysis (STA) must obtain cell delay and net delay.

- The backend tool calculates the delay per cell and the delay per line

- Unit delay information is provided by unit library files provided by foundary

- In order to calculate line delay, the tool must know the parasitic resistance and parasitic capacitance of each line

2. cell delay

The cell delay depends on:

input transition: The smaller the input transition, the smaller the cell delayoutput load: The smaller the output load, the smaller the cell delayPVT

The PVT angle refers to the conditions under which the STA executes.The most common PVT angles are:- WCS (Slow Process, Low Voltage, High Temperature)

- BCF(Fast Process, High Voltage, Low Temperature)

- Typical(Typical Process, Standard Voltage, Standard Temperature)

- WCL (worst case at low temperature: slow process, low voltage, low temperature)

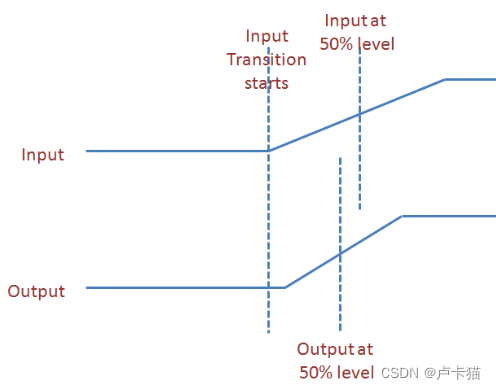

The generally seen cell delays are all positive values. Actually, the cell delay has negative delays. When the output transition is fast enough, it is entirely possible that the output 50% level is ahead of the input50.% level, that is, a negative delay occurs.

A negative cell delay occurs as follows:

- Driver is powerful enough

- Input transition is small enough

- Output load is small

3.net delay

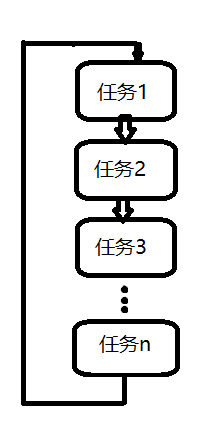

The calculation of the net delay is often carried out by dividing the net in the entire design into several segments, and at the same time, each segment of the net is represented by a certain RC model.

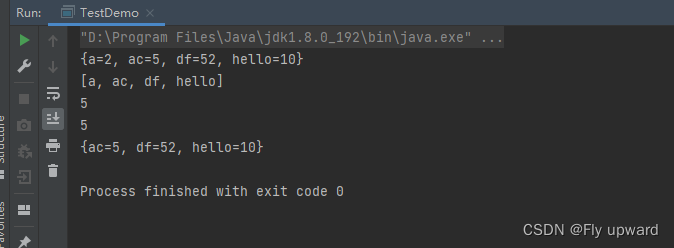

The database after PR tool wiring needs to use Start-RC to extract RC and output it as an RC file in SPEF format.Finally, read the RC file in the Timing signoff tool PT to calculate the delay.

In simple terms: net delay =~ 3*R*C

So the larger the R*C, the larger the net delay.

Can net delay be negative?

The answer is Yes, in the absence of crosstalk, the net delay must be positive.

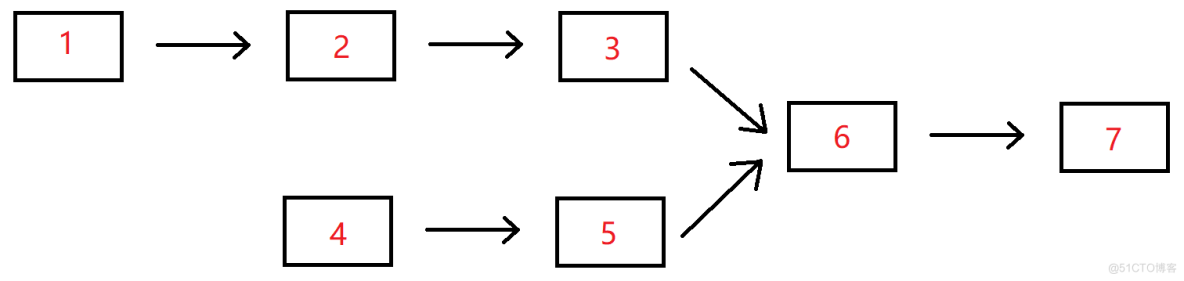

If exists crosstalk, when Net1 has a rising edge transition, Net2 also transitions from 0 to 1, and when the transition changes faster than Net1, there will be a negativecrosstalk.It is precisely because of this negative crosstalk that the transition of NET1 is better, resulting in a negative net delay value.

边栏推荐

- 论文解读(JKnet)《Representation Learning on Graphs with Jumping Knowledge Networks》

- 【保姆级示例向】观察者模式

- “vite”和“vite预览”有什么区别?

- 【LeetCode】899. 有序队列

- DataWorks 标准版怎样实现SQL代码的复用?

- leetcode-每日一题899. 有序队列(思维题)

- 341. Flatten Nested List Iterator

- PMP试题 | 每日一练,快速提分

- 微信小程序 - 数组 push / unshift 追加后数组返回内容为数字(数组添加后打印结果为 Number 数值类型)

- 云图说丨初识华为云微服务引擎CSE

猜你喜欢

Adobe是什么?

Cool open technology x StarRocks: unified OLAP analysis engine, comprehensive building digital model of OTT

数据万象内容审核 — 共建安全互联网,专项开展“清朗”直播整治行动

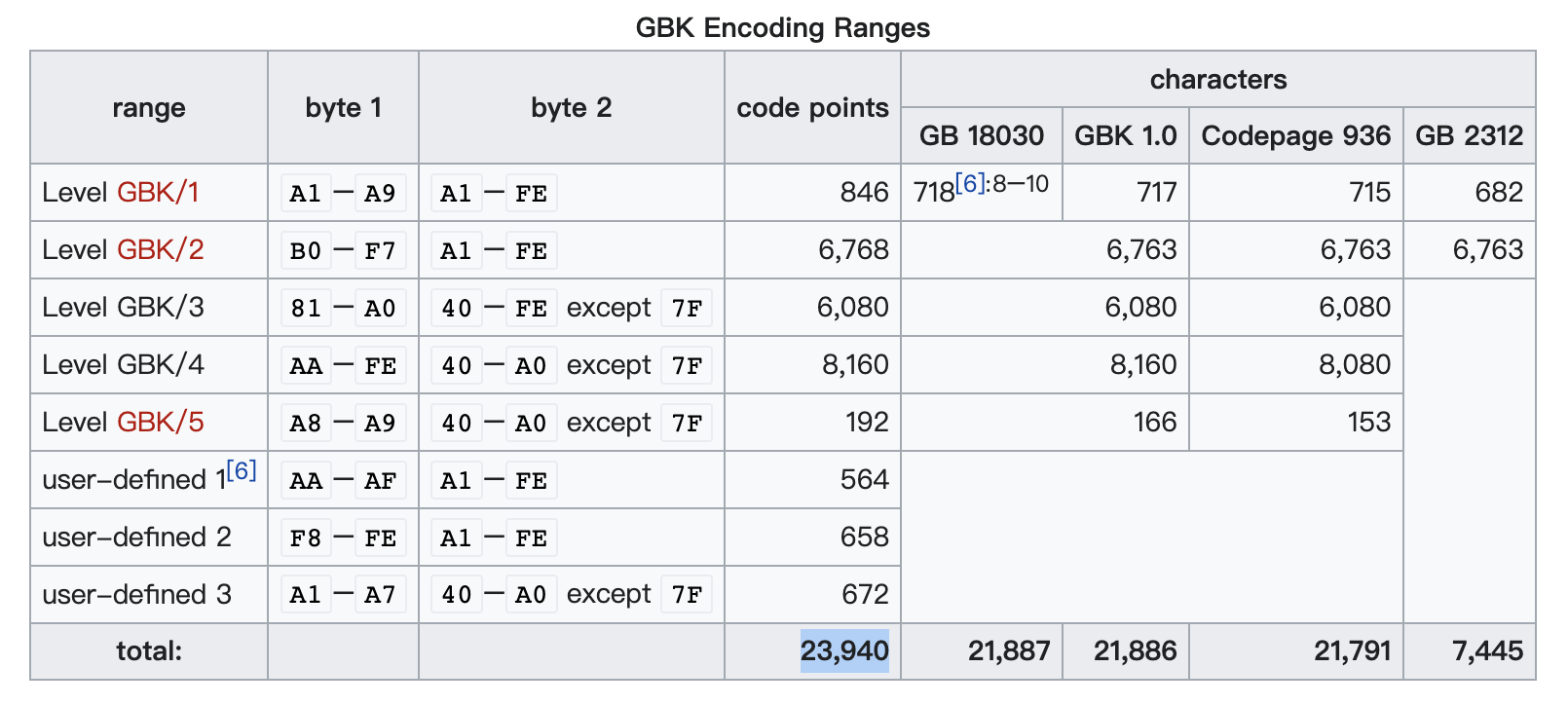

JS string to GBK encoding ultra-reduced implementation

一些嵌入式软件设计经验

#yyds干货盘点# 面试必刷TOP101:两个链表的第一个公共结点

Map和Set

【技术白皮书】第一章:OCR智能文字识别新发展——深度学习的文本信息抽取

LeetCode·72.编辑距离·动态规划

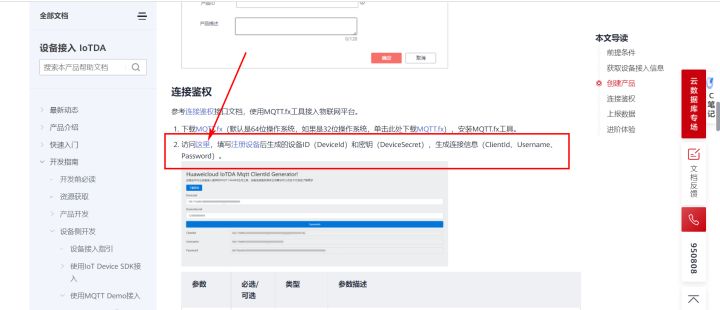

CC2530_ZigBee+华为云IOT:设计一套属于自己的冷链采集系统

随机推荐

使用o.execute_sql 查询很很很小的表, 要7/8秒钟, 这个怎么解决

sibling component communication context

新“妖股”13个交易日暴涨320倍,市值3100亿美元超阿里

出海,是泡泡玛特的“解药”吗?

计网知识点

J9数字虚拟论:元宇宙的潜力:一股推动社会进步的力量

JVS低代码-多数据模型与数据联动配置举例

mysql之的执行计划

ICDAR比赛技术分享

DataWorks 标准版怎样实现SQL代码的复用?

“vite”和“vite预览”有什么区别?

大型企业数据治理的现状和解决方案有哪些参考?_光点科技

yaml数据格式

【Metaverse系列一】元宇宙的奥秘

数字IC笔迹-MCMM、WNS和TNS

并发高的情况下,试试用ThreadLocalRandom来生成随机数

11. Container With Most Water

LeetCode·72.编辑距离·动态规划

酷开科技 × StarRocks:统一 OLAP 分析引擎,全面打造数字化的 OTT 模式

vant自动上传图片/文件