当前位置:网站首页>[quick start of Digital IC Verification] 26. Ahb-sramc of SystemVerilog project practice (6) (basic points of APB protocol)

[quick start of Digital IC Verification] 26. Ahb-sramc of SystemVerilog project practice (6) (basic points of APB protocol)

2022-07-07 15:20:00 【luoganttcc】

Reading guide : The author has the honor to be a pioneer in the field of electronic information in China “ University of electronic technology ” During postgraduate study , Touch the cutting edge Numbers IC Verification knowledge , I heard something like Huawei Hisilicon 、 Tsinghua purple light 、 MediaTek technology And other top IC related enterprises in the industry , Pairs of numbers IC Verify some knowledge accumulation and learning experience . Want to get started for help IC Verified friends , After one or two thoughts , This column is specially opened , In order to spend the shortest time , Take the least detours , Most learned IC Verify technical knowledge .

List of articles

- One 、 Description of content

- Two 、APB Bus Overview

- 2.1、APB And AHB contrast

- 2.2、APB Signal Introduction

- 2.3、APB Signal interpretation

- 2.4、APB Slave Address decoding

- 2.5、APB Interconnection diagram

- 2.6、APB sequential ( important )

- 2.7、APB Bridge

- 2.8、APB Bridge FSM( State machine )

- 2.9、APB Slave block diagram ( Interface signal , Need to be able to draw )

- 2.10、APB To AHB Timing conversion - read

- 3、 ... and 、 Different IP The interconnection between

- Four 、AMBA Review

- 5、 ... and 、 summary

One 、 Description of content

- APB Signal Introduction

- APB Transmission timing

- AHB And APB The difference between timing conversion

- Different IP The interconnection between

Two 、APB Bus Overview

2.1、APB And AHB contrast

AHB It is mainly used in high-speed and high-performance peripherals , and APB It is mainly used to mount low-speed peripherals .

stay APB Most of the peripherals mounted on the are Slave, No, Master, That is, peripherals that passively receive data .

Understand AHB After the bus , Study APB Naturally . Okay , I don't say much nonsense , Enter the text quickly .

2.2、APB Signal Introduction

| Signal name | Signal description |

|---|---|

| PCLK | APB Bus clock |

| PRESETn | APB Reset |

| PADDR[31:0] | APB Address bus |

| PSELx | APB Slave Select signal |

| PENABLE | APB Enable signal |

| PWRITE | APB Bus transmission direction |

| PRDATA | APB Read the data bus |

| PWDATA | APB Write data bus |

notes :APB Signals can be combined AHB Signal understanding memory .

2.3、APB Signal interpretation

- PADDR[31:0]

- Address bus , By the device bus bridge Unit drive

- PSELx

- The signal from the decoder , To a bus slave x

- PENABLE

- It is used to carry out all accesses in time stages on the device bus

- PWRITE

- High level : Write

- Low level : read

- PRDATA and PWDATA

- most 32 A wide

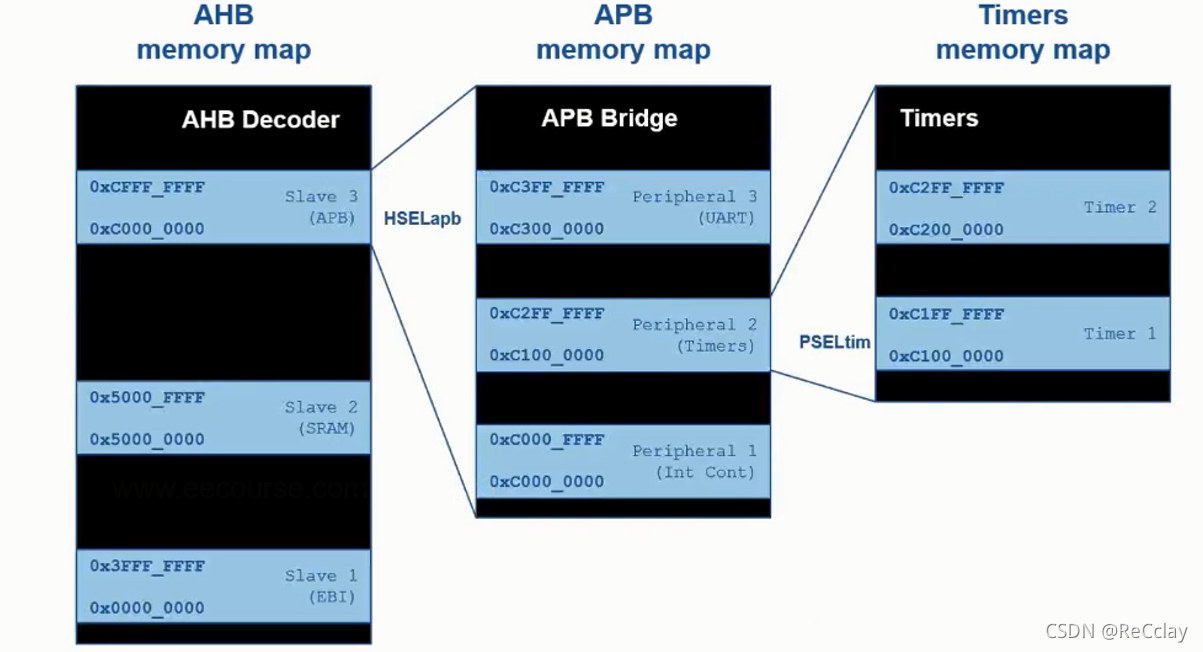

2.4、APB Slave Address decoding

- AHB-APB Bridge We can understand it as AHB Slave

- The black part in the above figure is Default Slave

- Address decoding is level by level

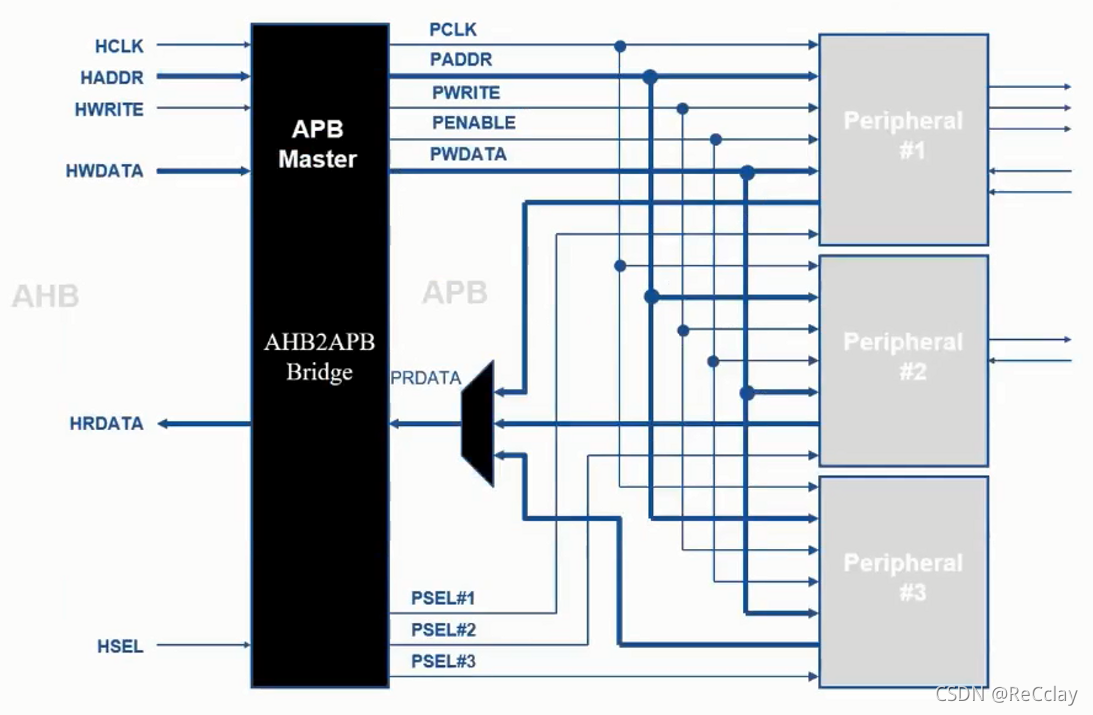

2.5、APB Interconnection diagram

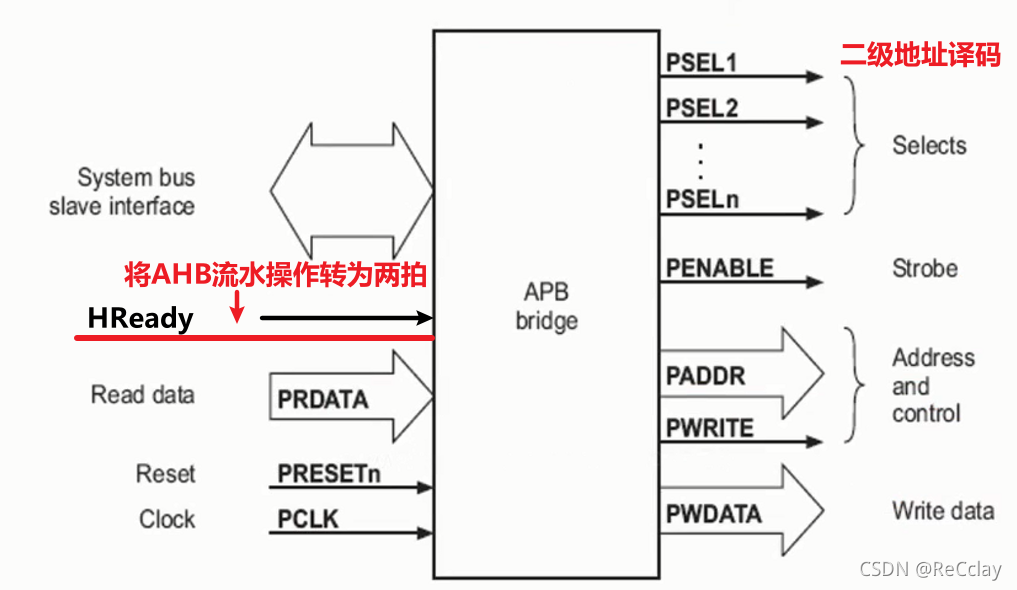

- Bridge Role is AHB To APB Timing conversion

2.6、APB sequential ( important )

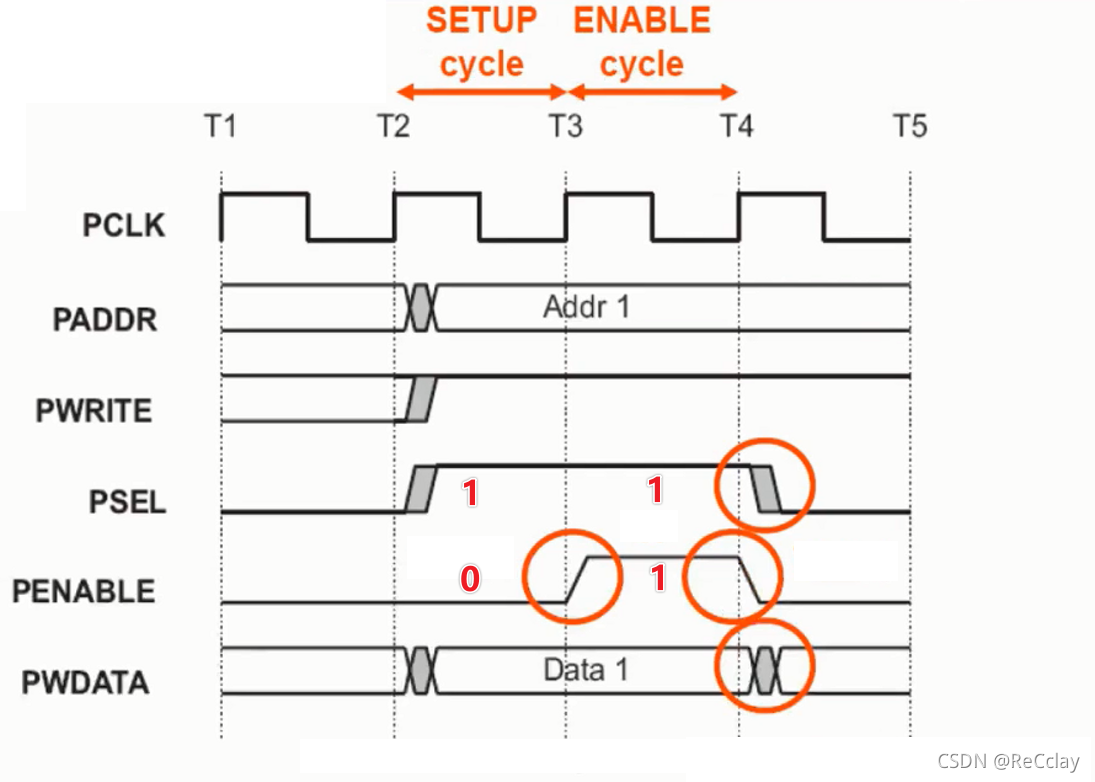

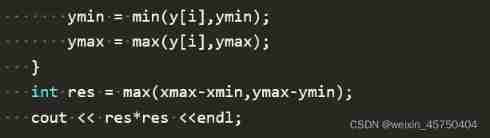

2.6.1、 Write transfer

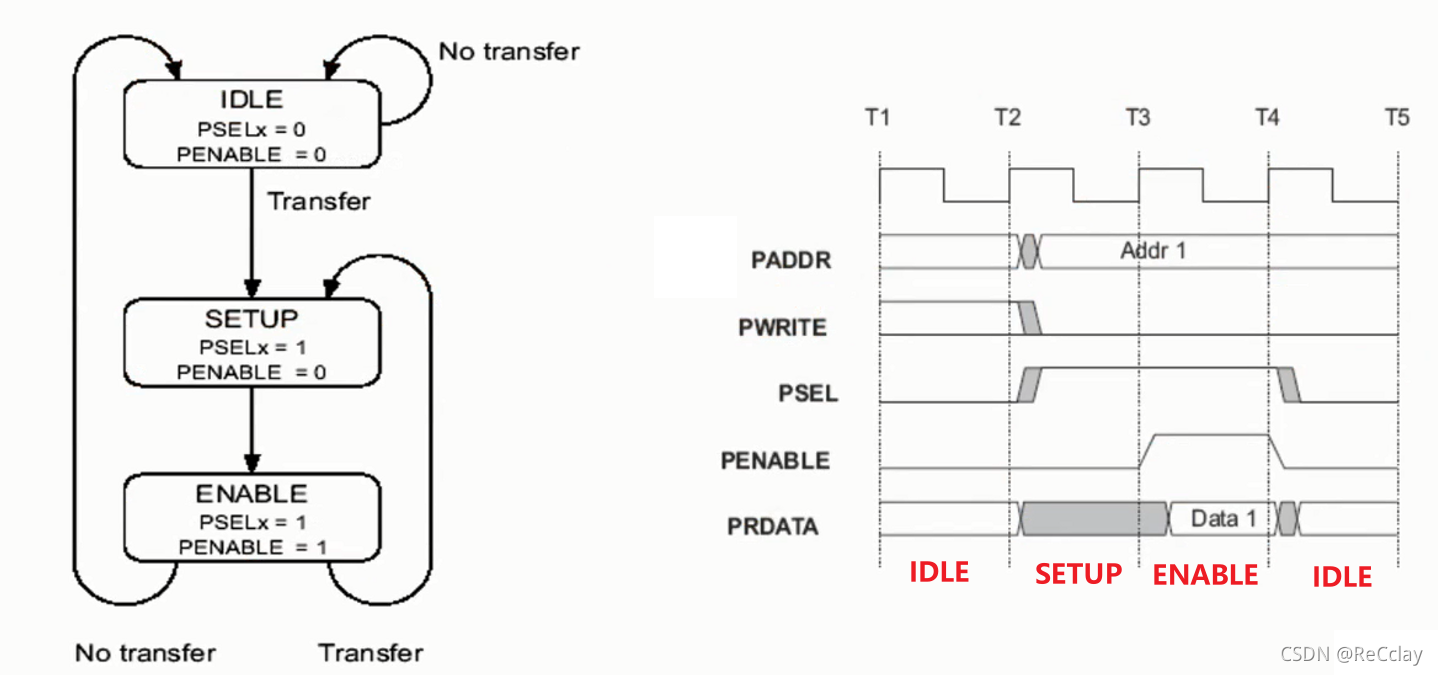

APB relative AHB Speaking of There is no running water , Each command is fixed At least 2 Clock cycles complete !

- APB There are two stages , First stage yes

SETUPStage , There is only one clock cycle . herePSELThe signal is high ,PENABLEThe signal is low . Analogical AHB Address transmission phase in ! - The second stage is

ENBALEStage . herePSELThe signal is high ,PENABLEThe signal is high . read / The write data signal is valid , Analogical AHB Data transmission phase in !

- APB There are two stages , First stage yes

The above sequence is only AMBA 1.0/2.0 The temporal , Fixed only two beats . Upgrade to AMBA 3.0 Can be used later HREADY Expand

ENABLEStage , andSETUPOr a clock cycle .

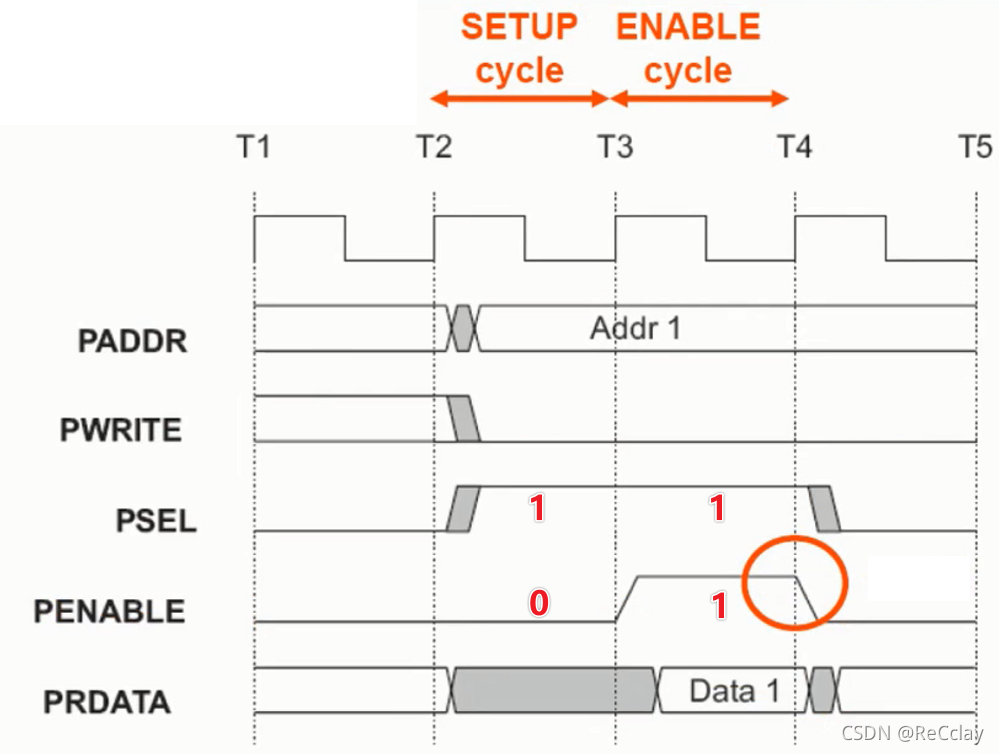

2.6.2、 Read transfer

- The biggest difference between reading and writing is

PWRITEThe signal , At this time, the signal is low . - The above sequence is only AMBA 1.0/2.0 The temporal , Fixed only two beats . Upgrade to AMBA 3.0 Can be used later HREADY Expand

ENABLEStage , andSETUPOr a clock cycle .

2.7、APB Bridge

- AHB It's running water , about Bridge Speaking of , The main function is to interrupt the running water , Namely the AHB The sequence of turns into APB, If AHB If it's running water , It'll go through this Bridge To interrupt !

- Mainly through

HREADYSignal to beat the flowing water into two beats .

- Mainly through

- APB Bridge Another function is to do a two-level decoding

2.8、APB Bridge FSM( State machine )

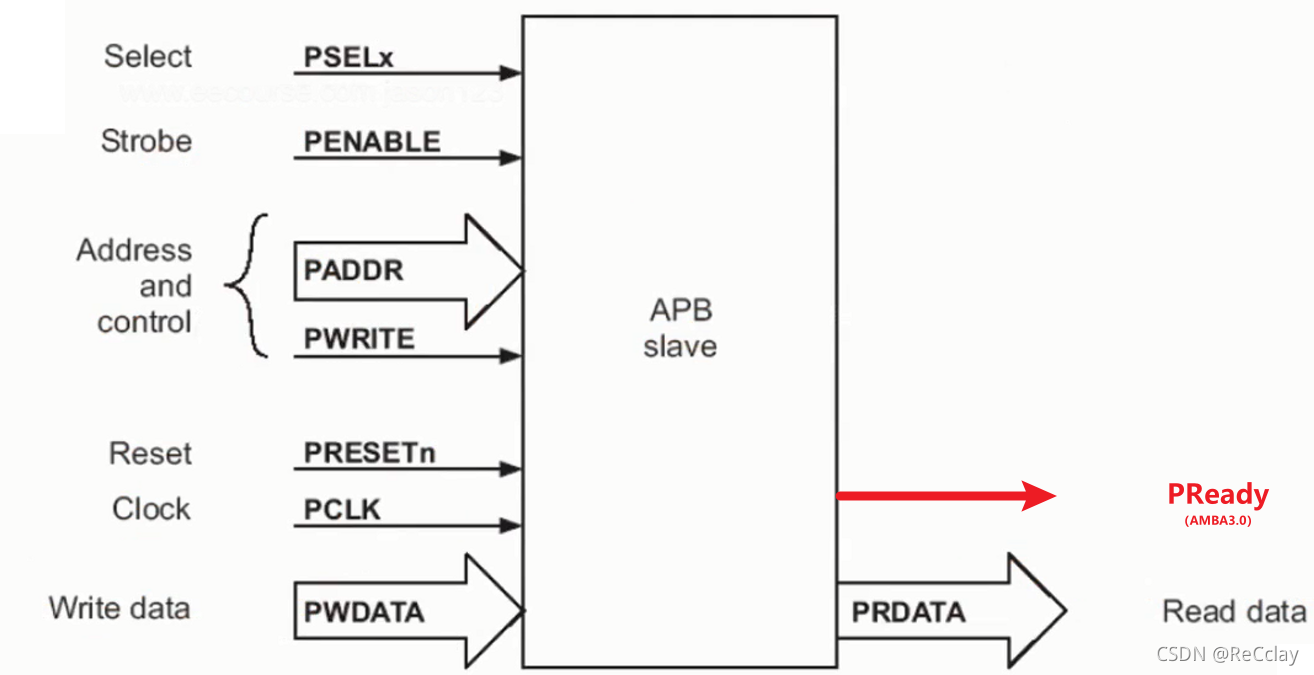

2.9、APB Slave block diagram ( Interface signal , Need to be able to draw )

- Control Signal comparison AHB Much less !

- ABMA 3.0 Support

PReadySignal oh ~!

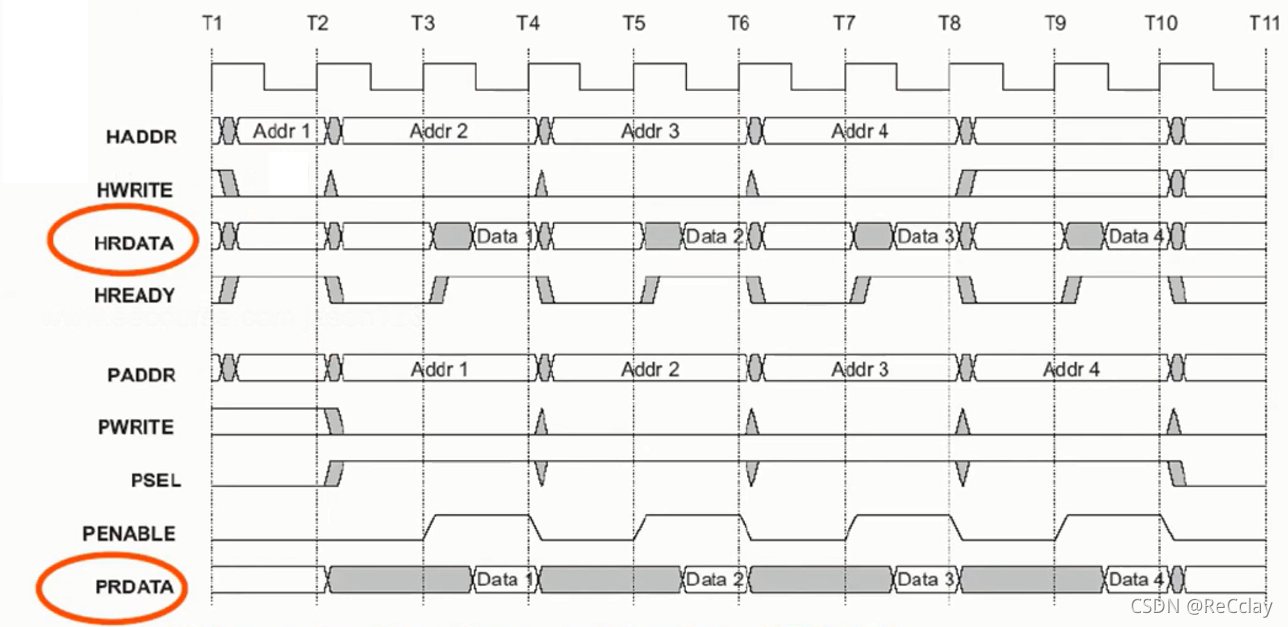

2.10、APB To AHB Timing conversion - read

- Above, AHB Read APB Slave Sequential operation of , You can see through

HReadyThe signal interrupts the flow operationT1-T2BetweenHREADYFor the high , adoptHADDRTransmit address signal , adoptHWRITEFor low , Transmit read control signal .T2-T3BetweenHREADYFor low , interrupt AHB Read operation of pipelining . meanwhile ,APB OfPSELFor the high ,PENABLEFor low ,APB Get intoSETUPStage , Read address and read control signal .T3-T4Between ,APB OfPSELFor the high ,PENABLEFor the high ,APB Get intoENABLEStage , adoptPRDATARead APB Slave The data of . meanwhileHREADYFor the high , Will read to APB Slave data , Back toHRDATA.- So far, a read operation is completed .

PRDATAYes, it can be sent directly toHRDATA( In the same shot ), If you want toHRDATATake a picture , Can be in APBENABLEStage will alsoHREADYPull it down , suchHRDATAIt will be later thanPRADTAOne shot .

3、 ... and 、 Different IP The interconnection between

3.1、 communication mode

- CPU (Master) < – > IP (Slave)

- IP(Master) < – > IP (Slave)

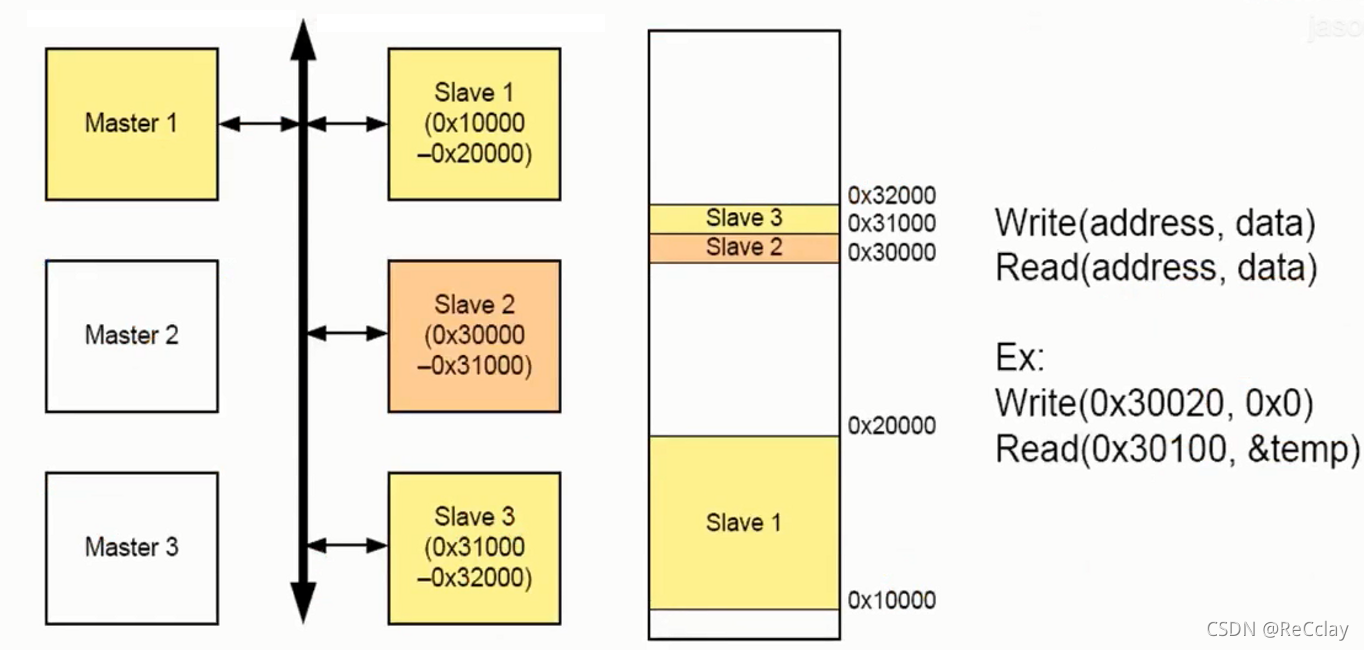

3.2、Memory Mapped IO

- Each slave device occupies a section of address space in the system

- All slaves are addressable

- register / Memory is accessed by memory mapping

- CPU/IP Read and write other IP The data of is similar to read-write memory

3.3、IP Communication interconnection between

- The main device is arbiter grant after , You can access all slave devices on the bus

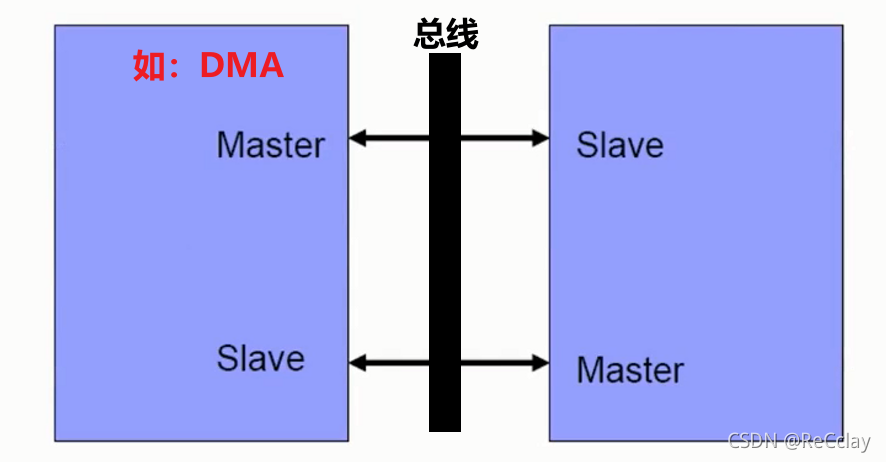

3.4、 One IP You can have both master device interface and slave device interface

- Master Go outside to read and write data

- Slave Configure as a register

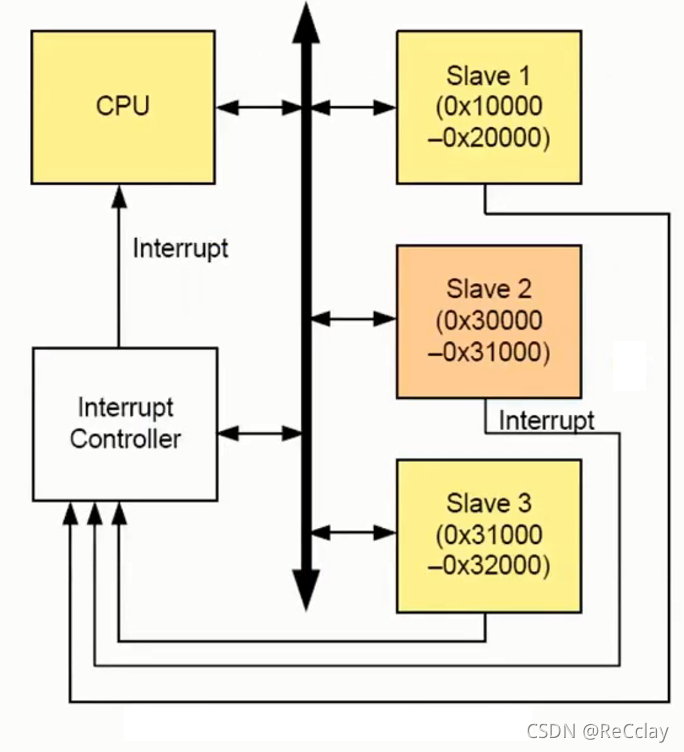

3.5、CPU And IP Communication between

- CPU Always be the main device

- IP Always act as a slave

- IP You can send an interrupt request

- Only Slave Interface IP, If you want to take the initiative to inform CPU You can interrupt

- There should not be too much information in the interrupt

- CPU Enter interrupt mode , from interrupt service routine(ISR) To handle interrupts

Four 、AMBA Review

- AMBA brief introduction

- AMBA2.0:AHB、ASB、APB

4.1、AHB

AHB Component part

- AHB Master、AHB Slave、AHB Aribiter、AHB Decoder

AHB The signal

- HCLK、HRESETn、HADDR、HTRANS、HWRITE、HSIZE、HBURST、HWDATA、HSELx、HRDATA、HREADY、HRESP

AHB Two stages of transmission

- Address cycle 、 Data cycle

Current transmission status HTRANS

- IDLE、BUST、NOSEQ、SEQ

Burst transmission type HBURST( understand )

- SINGLE、INCR( How to start a new INCR transmission ?)

- Burst Transmission cannot be crossed 1K The border

HSEL: from AHB Decoder Given by address mapping

AHB Slave response signal

- HREADY Transmission complete 、HRESP Transmit response (OK、ERROR、RETRY)

- AHB Slave Unable to respond in a short time (HREADY)? Unable to respond for a long time (HRESP)【 In practice, it is impossible to define what short time is , What is long time , So it is not used much !】

32 Valid bytes of the data bus at the bit size end

AHB Arbitration signal ( understand )

- HBUSREQ、HGRANT、HMASTER

- Main equipment x Can control the conditions of the bus

AHB Master、AHB Slave、AHB Arbiter、AHB Decoder Interface signal of

AHB-Lite

4.2、APB

APB Component part

- AHB2APB Bridge、APB Slave

APB The signal

- PCLK、PRESETn、PADDR、PSEL、PENABLE、PWRITE、PRDATA、PWDATA

APB Slave Address mapping for

APB transmission (AMBA 1.0/2.0)

- Always two cycle transfer:Setup cycle、Enable Cycle

- No wait cycle and response signal(AMBA 3.0 There is )

APB Bridge and APB Slave Interface signal of

5、 ... and 、 summary

thus AMBA In the agreement APB The theoretical knowledge of bus is introduced ,APB a AHB The biggest feature is that there is no flow operation , And APB stay AMBA 2.0 in , The execution of the command is fixed for two clock cycles . Through the introduction of this article, it is not difficult to find ,APB and AHB Many signals are similar , And APB a AHB A lot of control signals are missing , So just understand AHB,APB Naturally . Later we will pass AHB-SRAMC Actual project , Continue to understand AHB and APB.

Postscript : Because my level is limited , Shortcomings are inevitable , Please comment and make corrections . About bloggers 《 Numbers IC Verify the quick start 》 Series articles , Currently in CSDN Serial update , Welcome to subscribe to !

边栏推荐

- Stm32f103c8t6 PWM drive steering gear (sg90)

- There is a cow, which gives birth to a heifer at the beginning of each year. Each heifer has a heifer at the beginning of each year since the fourth year. Please program how many cows are there in the

- 【数字IC验证快速入门】29、SystemVerilog项目实践之AHB-SRAMC(9)(AHB-SRAMC SVTB Overview)

- [target detection] yolov5 Runtong voc2007 data set

- Deformable convolutional dense network for enhancing compressed video quality

- Spatiotemporal deformable convolution for compressed video quality enhancement (STDF)

- Oracle control file loss recovery archive mode method

- Ctfshow, information collection: web5

- 【OBS】RTMPSockBuf_Fill, remote host closed connection.

- 最安全的证券交易app都有哪些

猜你喜欢

Notes HCIA

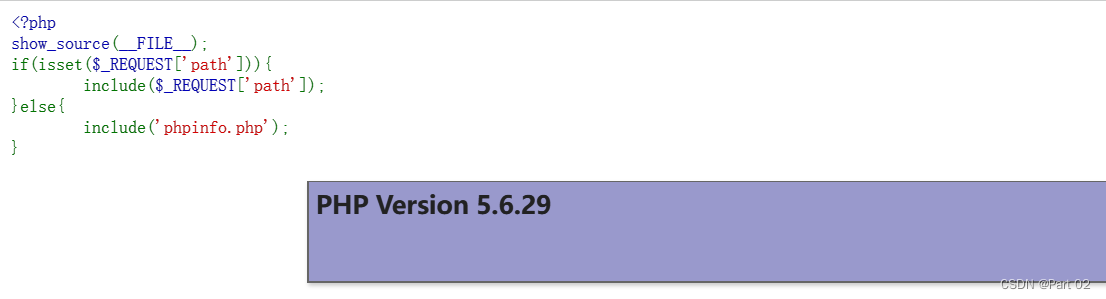

“百度杯”CTF比赛 2017 二月场,Web:include

![[data mining] visual pattern mining: hog feature + cosine similarity /k-means clustering](/img/a4/7320f5d266308f6003cc27964e49f3.png)

[data mining] visual pattern mining: hog feature + cosine similarity /k-means clustering

全日制研究生和非全日制研究生的区别!

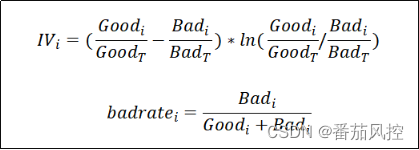

Do you know the relationship between the most important indicators of two strong wind control and the quality of the customer base

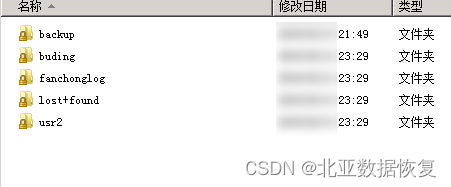

【服务器数据恢复】某品牌StorageWorks服务器raid数据恢复案例

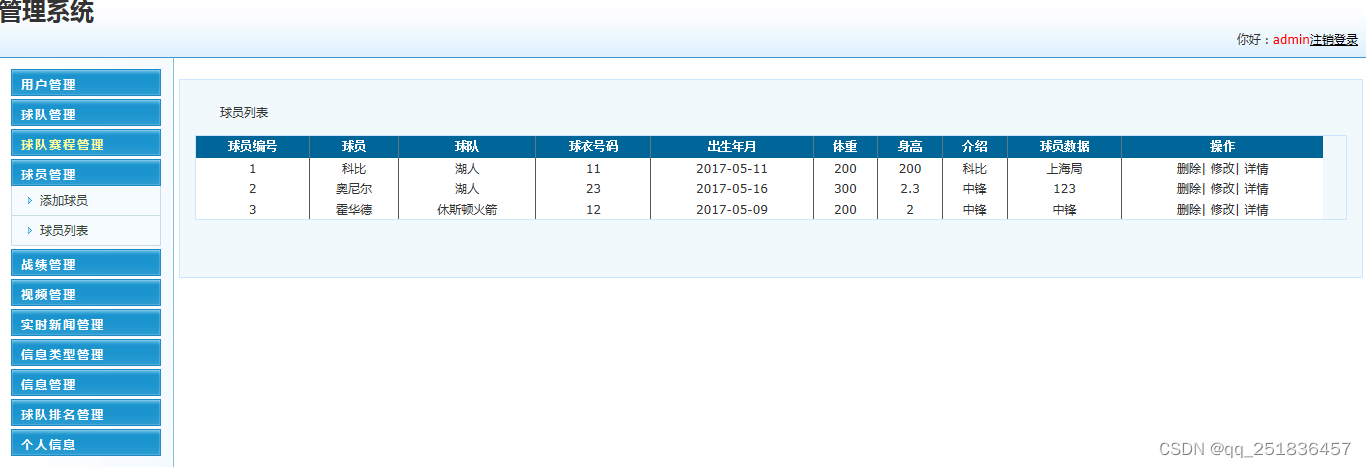

asp. Netnba information management system VS development SQLSERVER database web structure c programming computer web page source code project detailed design

有一头母牛,它每年年初生一头小母牛。每头小母牛从第四个年头开始,每年年初也生一头小母牛。请编程实现在第n年的时候,共有多少头母牛?

Niuke real problem programming - Day11

CTFshow,信息搜集:web4

随机推荐

2022年5月互联网医疗领域月度观察

【OBS】RTMPSockBuf_ Fill, remote host closed connection.

CTFshow,信息搜集:web7

What is data leakage

Promoted to P8 successfully in the first half of the year, and bought a villa!

Stm32f103c8t6 PWM drive steering gear (sg90)

Oracle control file loss recovery archive mode method

Concurrency Control & NoSQL and new database

HW初级流量监控,到底该怎么做

@ComponentScan

【兰州大学】考研初试复试资料分享

连接ftp服务器教程

摘抄的只言片语

Niuke real problem programming - Day11

JSON parsing instance (QT including source code)

[server data recovery] a case of RAID data recovery of a brand StorageWorks server

避坑:Sql中 in 和not in中有null值的情况说明

Unity之ASE实现卡通火焰

【服务器数据恢复】戴尔某型号服务器raid故障的数据恢复案例

Briefly describe the working principle of kept