当前位置:网站首页>Introduction to SDC

Introduction to SDC

2022-08-05 02:18:00 【work makes me happy】

Foreword

The related concepts are organized and summarized based on online data, and some of the content is quoted from the article after the text.

When writing the .sdc constraints file, the first thing to do is to use create_clock to constrain the clock entering the FPGA.Its syntax is as follows:

create_clock[-add] [-name

Parameter explanation:

-name indicates the name of the generated clock

-period represents the clock period in ns

-waveform can describe the clock duty cycle and its up and down position in detail

-add is used to add multiple clock constraints to a port

Example:

create_clock-period 10 -name clk_100 [get_ports clk]

A clock with a period of 10ns and a duty cycle of 50% is generated, its name is clk_100, and its port name is clk

create_clock-period 10 -waveform {8 12} -name clk [get_ports clk]

Generate a clock with a period of 10ns rising edge 8ns, falling edge 2ns

create_clock-period 10 -name clk_100 [get_ports clk]

create_clock-perioid 6.6 -name clk_150 -add [get_ports clk]

Generate two clocks on one port of clk with periods of 10ns and 6.6ns, respectively.If the same port in a system has multiple clock inputs at different times, the -add parameter can be used.Otherwise, if the -add parameter is not added, the clock defined later is invalid.

Note 1:

In Tcl syntax [] means command substitution, so [get_portsfpga_clk] will execute a command to find the port in the design that matches the name of fpga_clk.

Note 2:

Tcl and SDC are case sensitive, so make sure fpga_clk is exactly the same as the port name in the design

Reference

| 1. Author | Blog Post |

| SDC timing constraints (1)-create_clock | |

| SDC files commonly used timing constraint statements | |

| SDC and TimeQuest API Reference Manual | |

Tcl/Tk Beginner Classic | |

| TimeQuest User Guide |

边栏推荐

- How to simply implement the quantization and compression of the model based on the OpenVINO POT tool

- Oracle encapsulates restful interfaces into views

- leetcode-另一棵树的子树

- C language diary 9 3 kinds of statements of if

- iNFTnews | 对体育行业和球迷来说,NFT可以带来什么?

- 【MySQL series】- Does LIKE query start with % will make the index invalid?

- Intel XDC 2022 Wonderful Review: Build an Open Ecosystem and Unleash the Potential of "Infrastructure"

- 【C语言】详解栈和队列(定义、销毁、数据的操作)

- How to deal with your own shame

- 02 【开发服务器 资源模块】

猜你喜欢

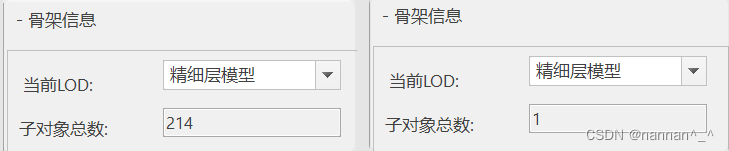

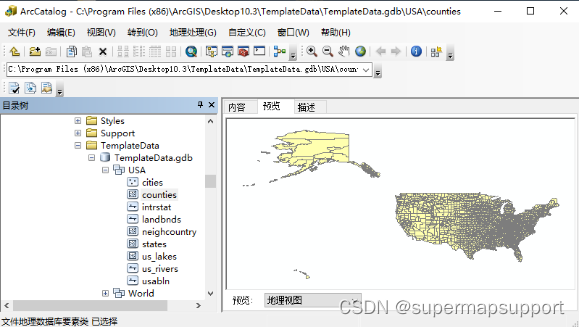

SuperMap iDesktop.Net之布尔运算求交——修复含拓扑错误复杂模型

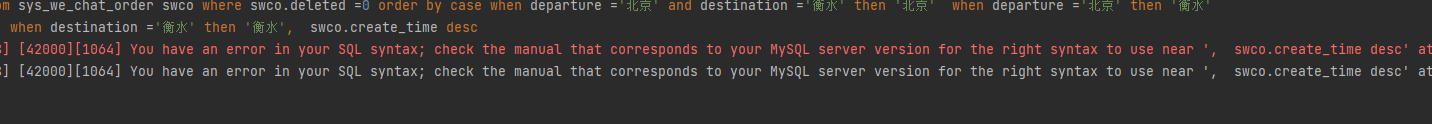

sql语句多字段多个值如何进行排序

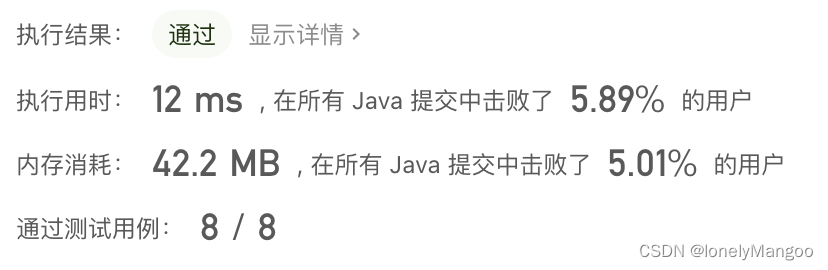

Leetcode刷题——22. 括号生成

C语言日记 9 if的3种语句

![[Unity Entry Plan] Handling of Occlusion Problems in 2D Games & Pseudo Perspective](/img/de/944b31c68cc5b9ffa6a585530e7be9.png)

[Unity Entry Plan] Handling of Occlusion Problems in 2D Games & Pseudo Perspective

Live playback including PPT download | Build Online Deep Learning based on Flink & DeepRec

使用SuperMap iDesktopX数据迁移工具迁移ArcGIS数据

![Chapter 09 Use of Performance Analysis Tools [2. Index and Tuning] [MySQL Advanced]](/img/e7/61863c356e4c7bb03ba27865ee7be0.png)

Chapter 09 Use of Performance Analysis Tools [2. Index and Tuning] [MySQL Advanced]

![[Endnote] Word inserts a custom form of Endnote document format](/img/70/e8a6f15b80e9c53db369fd715e51df.png)

[Endnote] Word inserts a custom form of Endnote document format

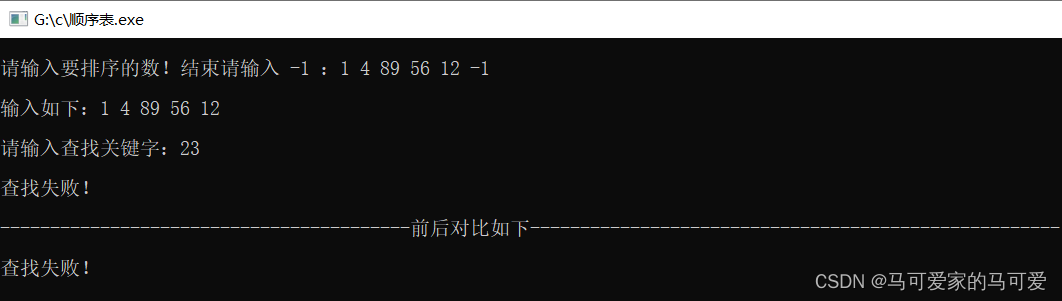

线性表的查找

随机推荐

the mechanism of ideology

汇编语言之源程序

如何模拟后台API调用场景,很细!

力扣-相同的树

行业案例|世界 500 强险企如何建设指标驱动的经营分析系统

J9数字货币论:web3的创作者经济是什么?

2022 EdgeX中国挑战赛8月3日即将盛大开幕

Simple implementation of YOLOv7 pre-training model deployment based on OpenVINO toolkit

散列表的查找(哈希表)

C语言日记 9 if的3种语句

继承关系下构造方法的访问特点

Chapter 09 Use of Performance Analysis Tools [2. Index and Tuning] [MySQL Advanced]

刷爆朋友圈,Alibaba出品亿级并发设计速成笔记太香了

【解密】OpenSea免费创造的NFT都没上链竟能出现在我的钱包里?

迁移学习——Distant Domain Transfer Learning

学习笔记-----左偏树

优化Feed流遭遇拦路虎,是谁帮百度打破了“内存墙”?

蚁剑高级模块开发

nodeJs--封装路由

“配置”是把双刃剑,带你了解各种配置方法