当前位置:网站首页>Dspic33ep clock initialization program

Dspic33ep clock initialization program

2022-07-05 11:09:00 【Full stack programmer webmaster】

// file name p33clk.h

#ifndef _P33CLK_H_

#define _P33CLK_H_

//#include "p33clk.h"

#define WDT_ENB _SWDTEN = 1

#define WDT_DIS _SWDTEN = 0

// Clock source selection

#define OSCLK0 0 //FRC

#define OSCLK1 1 // belt PLL+N Frequency division FRC

#define OSCLK2 2 //HS MS LS The external clock

#define OSCLK3 3 // belt PLL Of HS MS LS The external clock

#define OSCLK4 4 // Retain

#define OSCLK5 5 //LPRC

#define OSCLK6 6 //FRC/16

#define OSCLK7 7 // belt N Frequency division FRC

// Processor and CPU Clock division ratio

#define DOZEDIV1 (0<<12)

#define DOZEDIV2 (1<<12)

#define DOZEDIV4 (2<<12)

#define DOZEDIV8 (3<<12)

#define DOZEDIV16 (4<<12)

#define DOZEDIV32 (5<<12)

#define DOZEDIV64 (6<<12)

#define DOZEDIV128 (7<<12)

//------------------------------

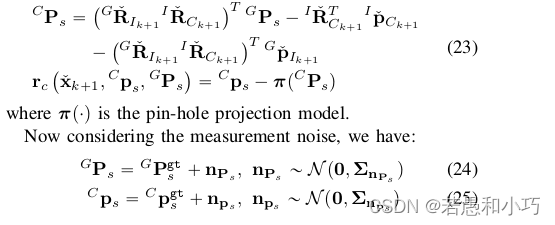

//Fosc = (Fin/V_FRCDIV/N1/N2)*M

#define V_FRCDIV V_FRCDIV1 //FRC Oscillation frequency division coefficient

#define V_N1 V_N1DIV(2) //x = 2--33 N1 Division coefficient

#define V_N2 V_N2DIV2 //N2 Division coefficient

#define V_PLLFBD PLLMF(50) //(x=2--513)PLL Octave ratio

//FRC Division coefficient

#define V_FRCDIV1 0

#define V_FRCDIV2 1

#define V_FRCDIV4 2

#define V_FRCDIV8 3

#define V_FRCDIV16 4

#define V_FRCDIV32 5

#define V_FRCDIV64 6

#define V_FRCDIV256 7

//N1

#define V_N1DIV(x) (x-2)

//N2

#define V_N2DIV2 0

#define V_N2DIV4 1

#define V_N2DIV8 3

//PLL Octave number M

#define PLLMF(x) (x-2)

//================================

extern void Init_Clk(uint16 OsClk) ;

#endif

// file name p33clk.c

#include "global.h"

#include "p33clk.h"

//***************************************

// The name of the function :InitClk

// The functionality : Initialize the clock

// Entrance parameters : Clock source selection FRC frequency division pll Octave ratio

// Export parameters : nothing

// Return value : nothing

// Fosc = (Fin/V_FRCDIV/N1/N2)*M

//***************************************

void Init_Clk(uint16 OsClk)

{

CLKDIV = 0X0000 ; // The clock ratio between processor and peripheral is 1:1

_FRCDIV = V_FRCDIV ; //FRC Division coefficient

_PLLPOST = V_N2 ;//N2

_PLLPRE = V_N1 ;//N1

PLLFBD = V_PLLFBD ;// PLL frequency doubling

OSCTUN = 0X0000 ; // Oscillator adjustment register Default 7.37M

REFOCON = 0X0000 ; // Reference clock = The system clock

OSCCON = 0X0000 ;

_OSWEN = 1 ; // The request for switching is made by NOSC Specified clock

_NOSC = OsClk ; // Switch New oscillator

while(_OSWEN) ;// Wait for the clock switch to complete

if((_NOSC == OSCLK1) ||(_NOSC == OSCLK3))// belt PLL

{

while(!_LOCK) ;// wait for PLL lock

}

REFOCON |= 0X8000 ; // Reference clock output enable

}

// Application example -- Clock initialization

//FRC The system clock 1 Frequency division to CPU PLL frequency doubling 50

//Fin = 7.37M Fcpu = Fosc/2 = 46.0625M

Init_Clk(OSCLK1) ;Publisher : Full stack programmer stack length , Reprint please indicate the source :https://javaforall.cn/109983.html Link to the original text :https://javaforall.cn

边栏推荐

- Node の MongoDB Driver

- websocket

- SQL Server monitoring statistics blocking script information

- Four departments: from now on to the end of October, carry out the "100 day action" on gas safety

- 关于 “原型” 的那些事你真的理解了吗?【上篇】

- 基础篇——REST风格开发

- 数据库三大范式

- BOM//

- C language current savings account management system

- MFC pet store information management system

猜你喜欢

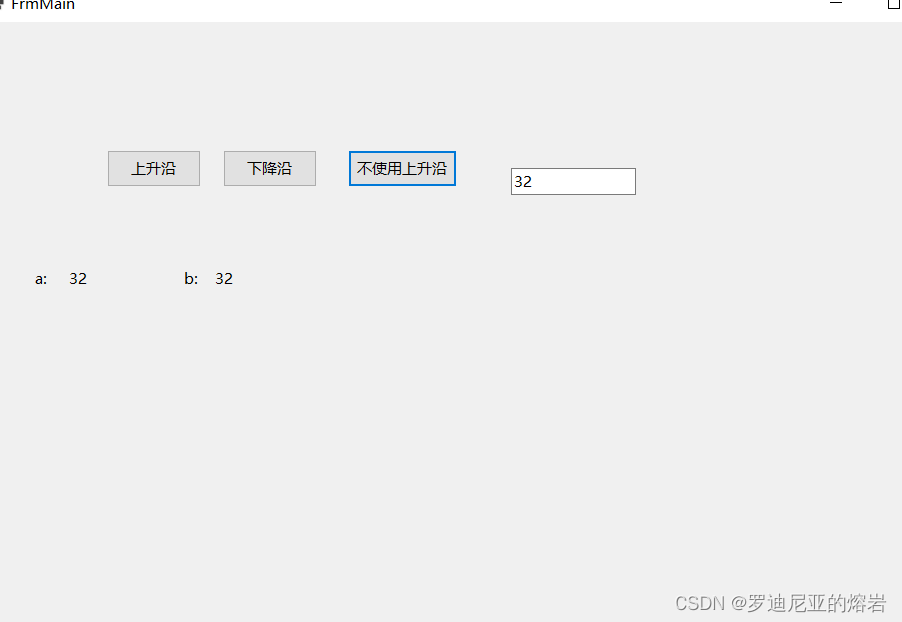

在C# 中实现上升沿,并模仿PLC环境验证 If 语句使用上升沿和不使用上升沿的不同

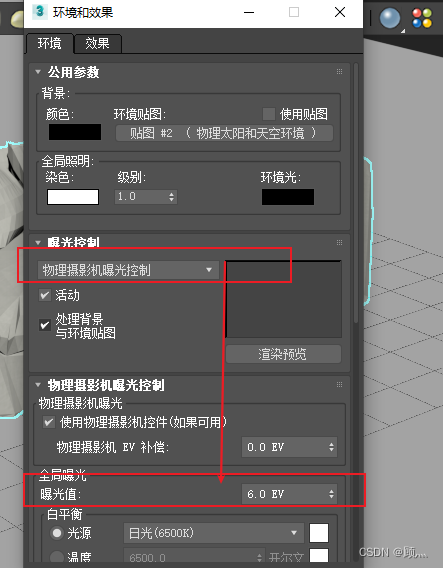

关于vray 5.2的使用(自研笔记)

![[Oracle] use DataGrid to connect to Oracle Database](/img/4f/886378667889f730eaed39b97f0a39.png)

[Oracle] use DataGrid to connect to Oracle Database

How to make full-color LED display more energy-saving and environmental protection

Question bank and answers of special operation certificate examination for main principals of hazardous chemical business units in 2022

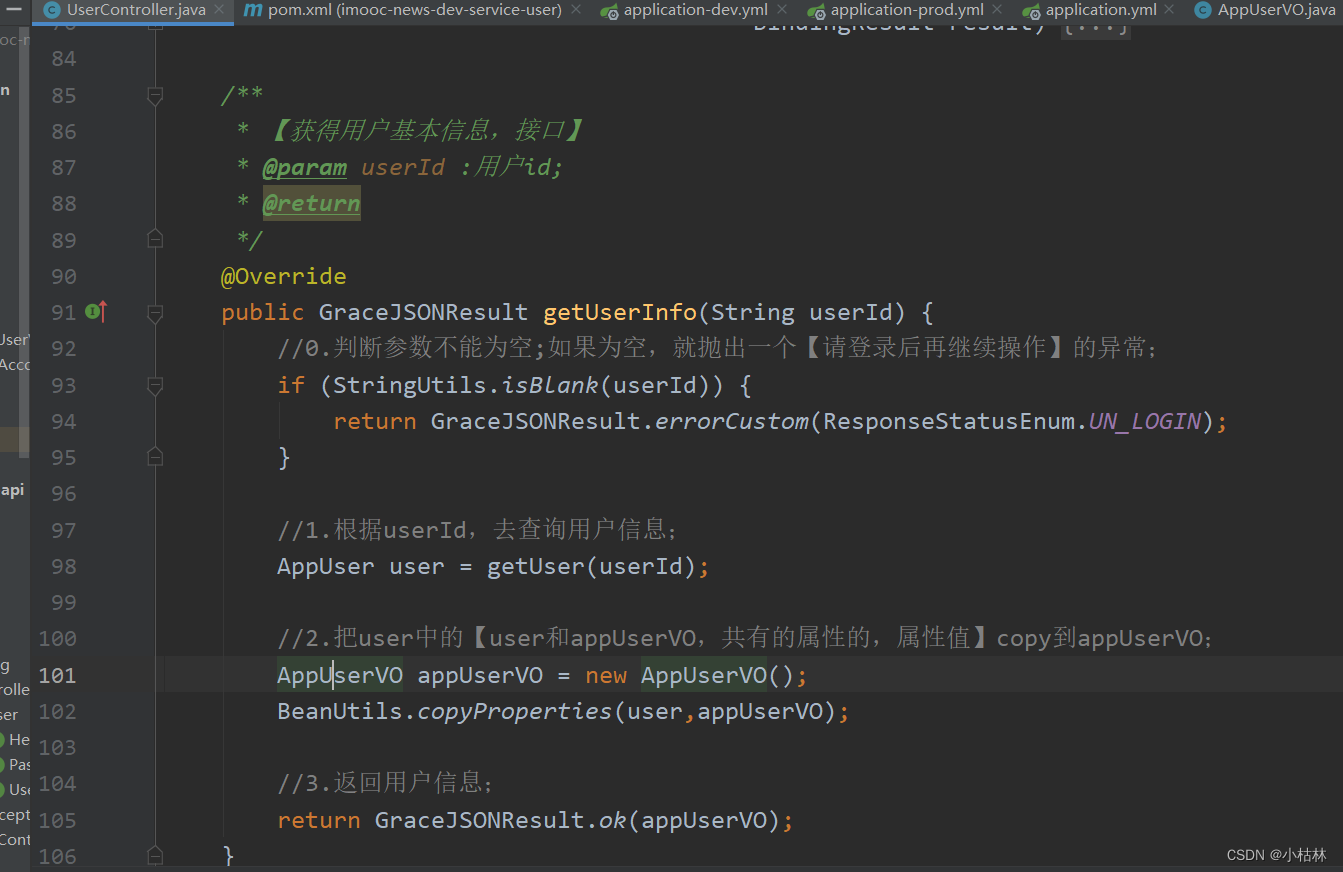

32:第三章:开发通行证服务:15:浏览器存储介质,简介;(cookie,Session Storage,Local Storage)

谈谈对Flink框架中容错机制及状态的一致性的理解

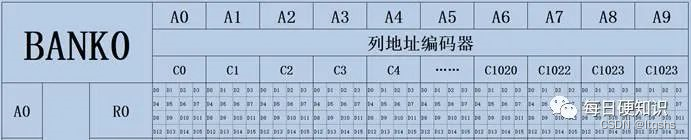

Ddrx addressing principle

R3Live系列学习(四)R2Live源码阅读(2)

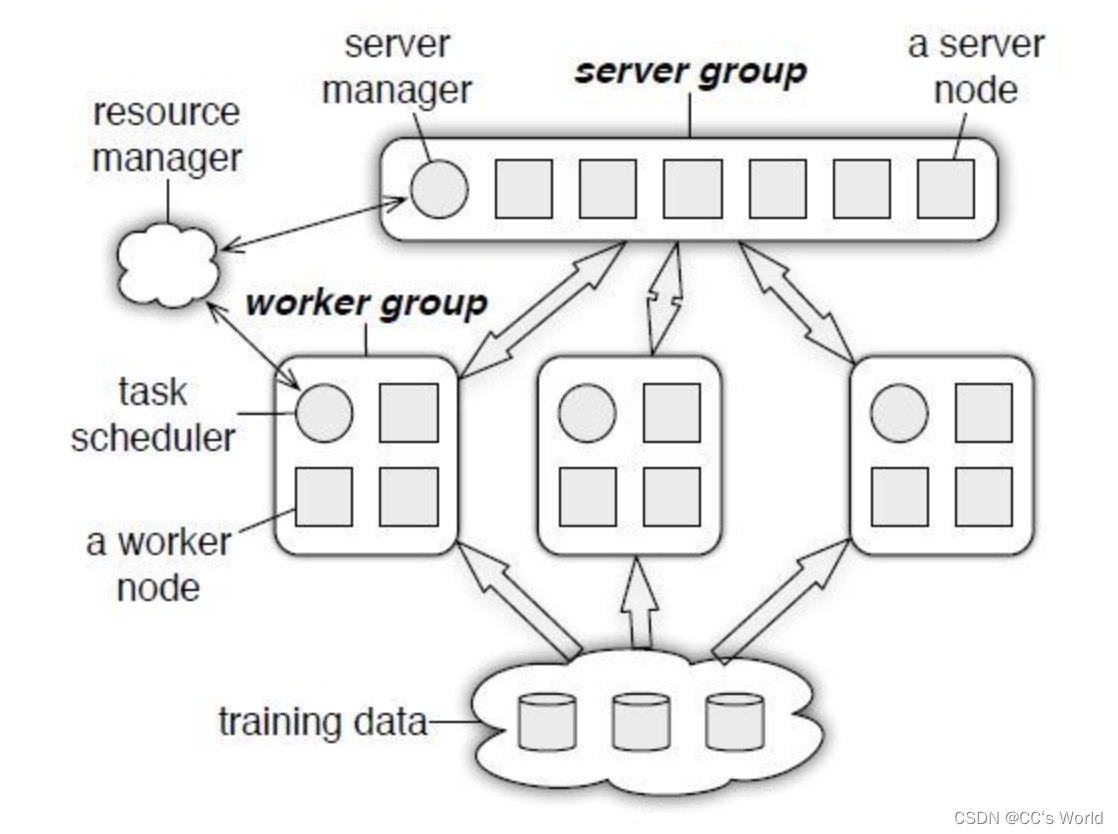

【广告系统】Parameter Server分布式训练

随机推荐

Ddrx addressing principle

Cross page communication

数据类型、

Array

Web3 Foundation grant program empowers developers to review four successful projects

[first release in the whole network] (tips for big tables) sometimes it takes only 1 minute for 2 hours of SQL operation

A usage example that can be compatible with various database transactions

第五届 Polkadot Hackathon 创业大赛全程回顾,获胜项目揭秘!

Go语言-1-开发环境配置

关于vray 5.2的使用(自研笔记)(二)

谈谈对Flink框架中容错机制及状态的一致性的理解

Broyage · fusion | savoir que le site officiel de chuangyu mobile end est en ligne et commencer le voyage de sécurité numérique!

不要再说微服务可以解决一切问题了!

Do you really understand the things about "prototype"? [part I]

DDRx寻址原理

【Oracle】使用DataGrip连接Oracle数据库

matlab cov函数详解

Wechat nucleic acid detection appointment applet system graduation design completion (8) graduation design thesis template

[advertising system] parameter server distributed training

[TCP] TCP connection status JSON output on the server