当前位置:网站首页>OneSpin 360 DV新版发布,刷新FPGA形式化验证功能体验

OneSpin 360 DV新版发布,刷新FPGA形式化验证功能体验

2022-07-07 18:21:00 【麦禾信通】

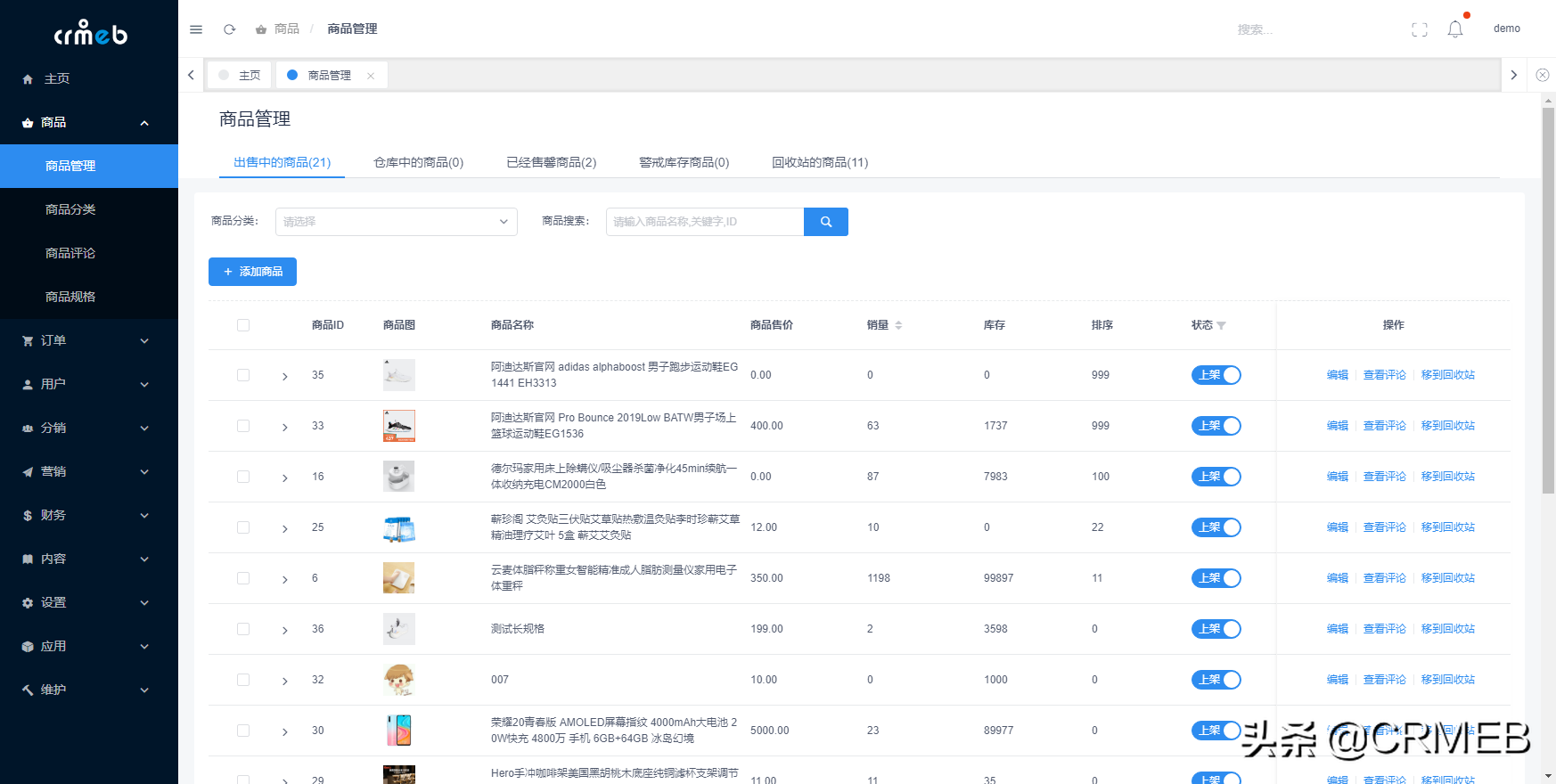

360 DV是针对FPGA设计进行功能验证的解决方案。它结合了功能齐全的高性能形式化分析和独特的断言覆盖率评估,消除质量断言生成过程中的猜测,有效提高现有设计和验证流程的生产率。本次更新将为设计团队带来哪些全新体验?

一、DV inspect 功能更新

● 读写竞争检查

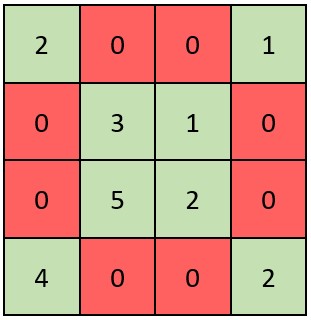

说明:如下图所示,仿真结果和上板结果不一致,这是在不同进程中读出和写入信号导致的综合和仿真不匹配问题,现在,OneSpin新增了检查这类问题的功能,确保仿真结果与综合后的实际情况一致。

● 负转换检查

说明:自动标记不被预期的设计行为

● 死锁/活锁检查

说明:如果DUT进入不再运行的状态(自动挂起),则在检查结果中标记

● 新增Lint检查项

* 混合极值复位

* 混合同步/异步复位

* 混合(非)阻塞赋值

* 无用的状态机位

* 无法综合的延迟

* 重复的case标签

* 多重驱动

* 非常量异步重置值

二、调试功能更新

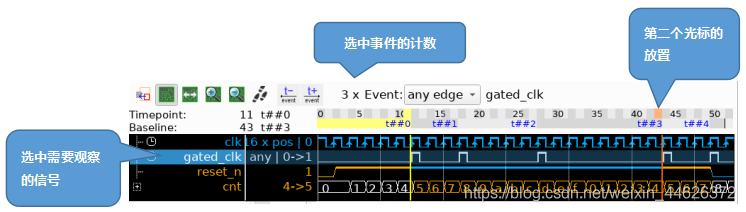

● 第二个波形光标的修改

说明:在波形界面计算事件次数很繁琐,而且容易出错。现第二个光标处会自动显示所选信号的事件计数,且可以放在下一个/前一个事件

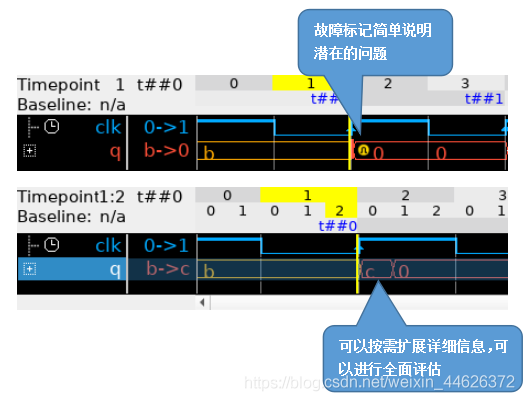

● 全新的故障视图

说明:在调试过程中,有害的故障数量较少,为了使故障在波形调试界面中,更明显,更易于分析,波形界面会高亮故障发生处,并提供简单的说明。

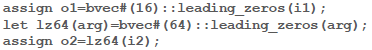

三、代码语言更新

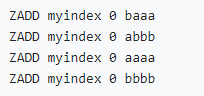

● 新增支持静态SystemVerilog类,在使用带有静态方法的类的共享函数/类型时更为灵活,如下图,可直接使用通用的前导零计数器

四、DV Apps更新

● IEEE-754 2019添加了新的最大/最小函数,而RISC-V标准中禁止了IEEE-754中的一些可选元素,现在,FPU app的RISC-V配置可无缝集成到RISC-V的FPU验证中

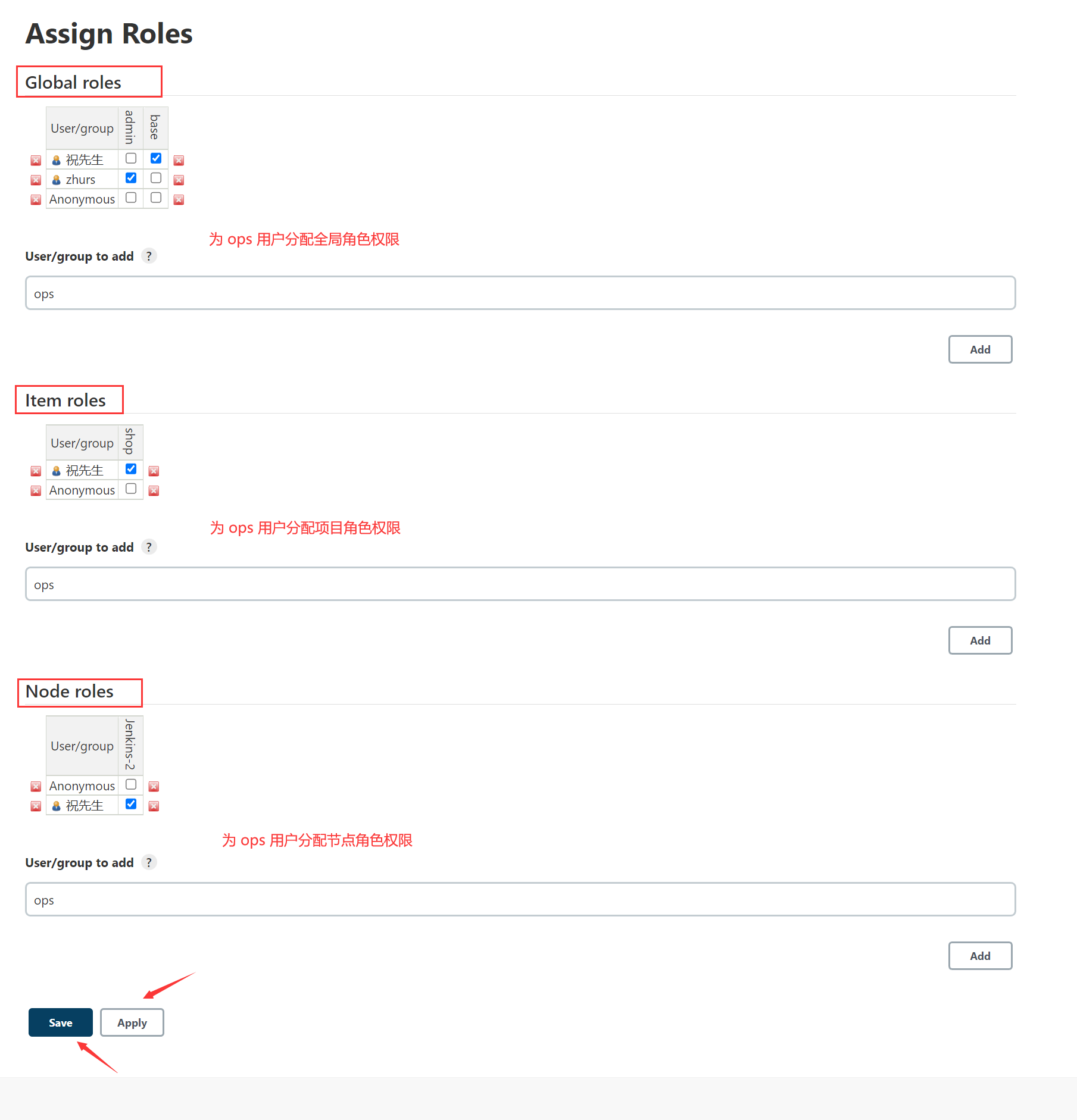

● 寄存器检查中支持检查信号名

说明:确保RTL信号名符合IP-XACT规范

● Connectivity APPs中支持自定义命名

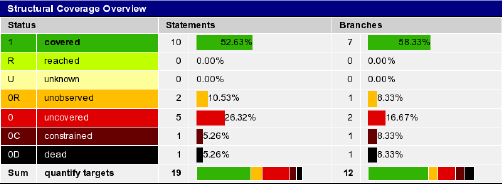

● 简化覆盖率检查的报告

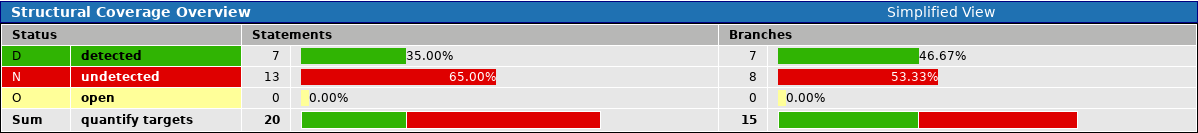

说明:覆盖状态简化为D(detected), N(undetected), O(open),使结果更为明确

原始覆盖率界面

新版覆盖率界面

新版覆盖率界面

边栏推荐

- Update iteration summary of target detection based on deep learning (continuous update ing)

- How to cooperate among multiple threads

- Solve the problem that the executable file of /bin/sh container is not found

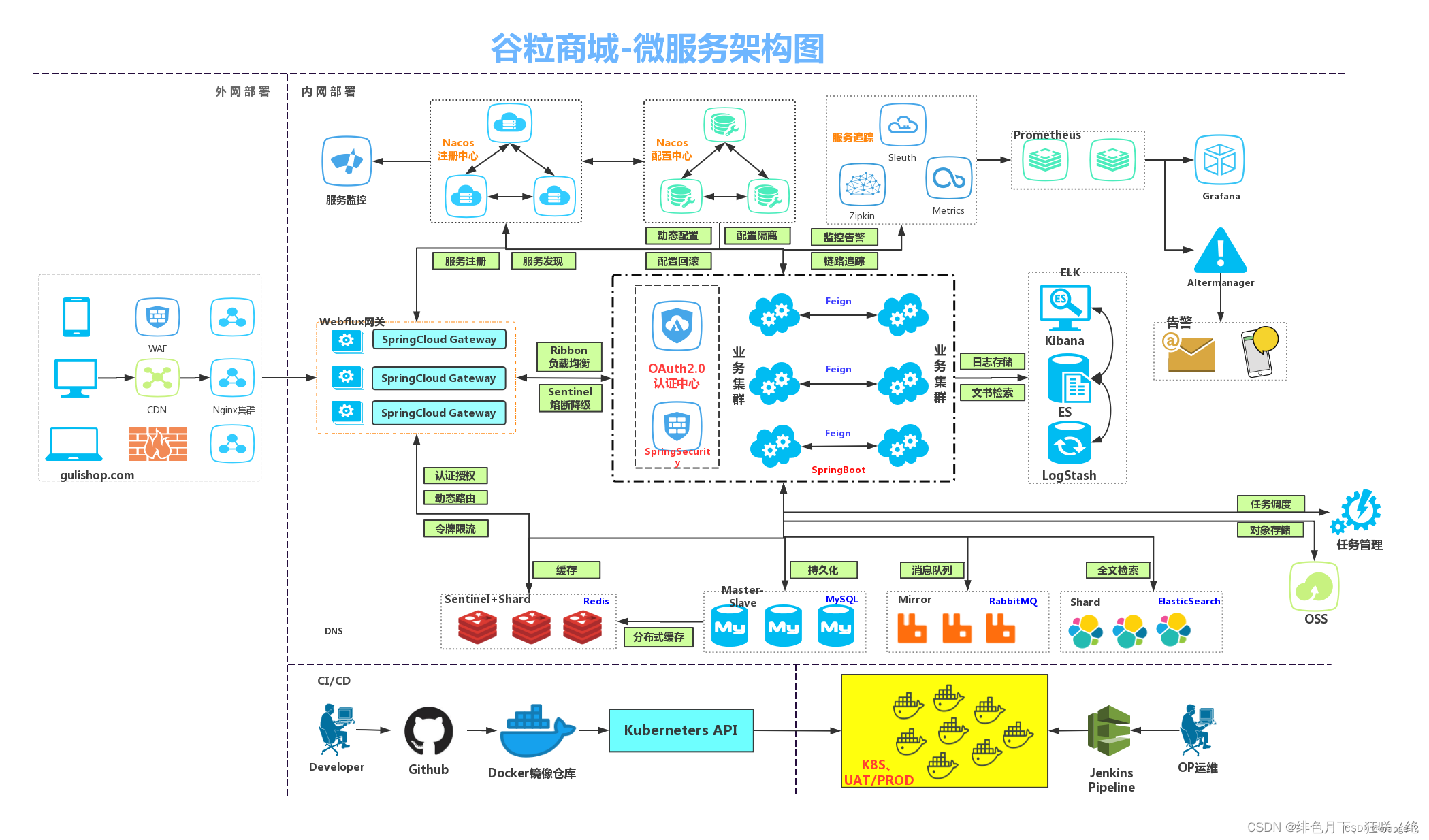

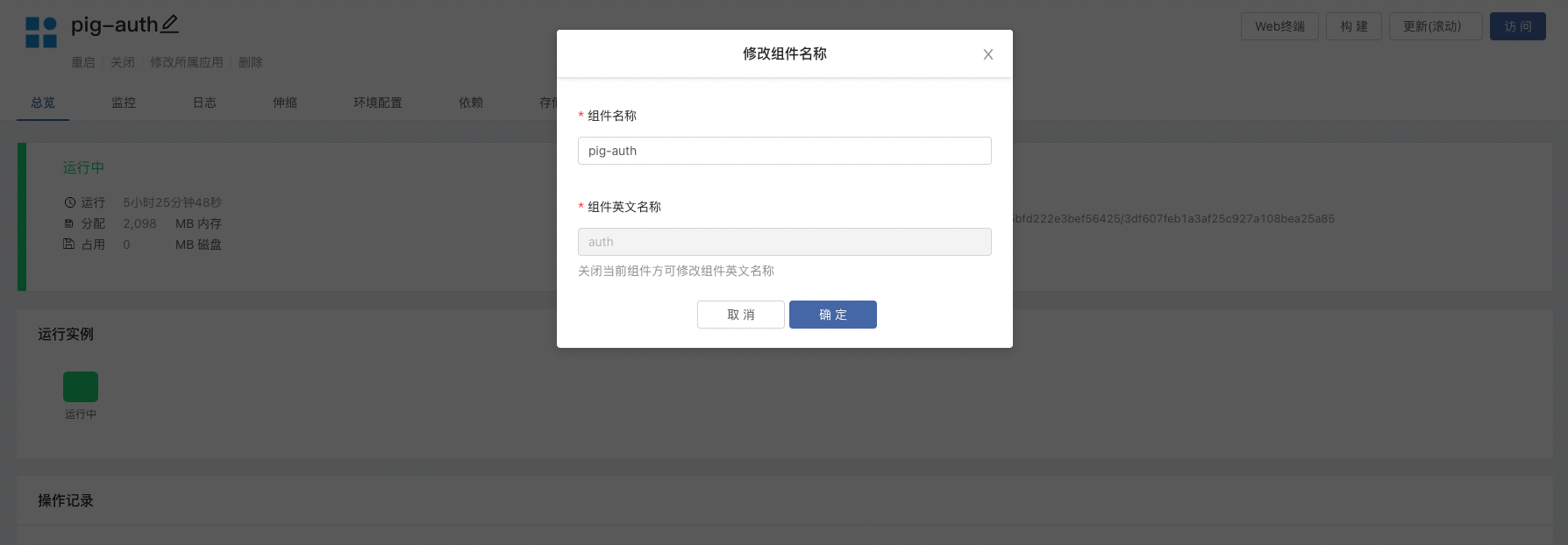

- 微服务远程Debug,Nocalhost + Rainbond微服务开发第二弹

- [solution] package 'XXXX' is not in goroot

- 【mysql篇-基础篇】事务

- MIT science and technology review article: AgI hype around Gato and other models may make people ignore the really important issues

- H3C S7000/S7500E/10500系列堆叠后BFD检测配置方法

- JNI 初级接触

- 开发那些事儿:Go加C.free释放内存,编译报错是什么原因?

猜你喜欢

随机推荐

CSDN语法说明

vulnhub之school 1

一. 基础概念

Open source heavy ware! Chapter 9 the open source project of ylarn causal learning of Yunji datacanvas company will be released soon!

机械臂速成小指南(十一):坐标系的标准命名

毕业季|遗憾而又幸运的毕业季

About cv2 dnn. Readnetfromonnx (path) reports error during processing node with 3 inputs and 1 outputs [exclusive release]

Cloud component development and upgrading

【论文阅读】MAPS: Multi-agent Reinforcement Learning-based Portfolio Management System

[résolution] le paquet « xxxx» n'est pas dans goroot

I Basic concepts

Force buckle 1037 Effective boomerang

关于cv2.dnn.readNetFromONNX(path)就报ERROR during processing node with 3 inputs and 1 outputs的解决过程【独家发布】

MIT science and technology review article: AgI hype around Gato and other models may make people ignore the really important issues

Force buckle 1232 Dotted line

Opencv learning notes high dynamic range (HDR) imaging

【解决】package ‘xxxx‘ is not in GOROOT

Force buckle 1961 Check whether the string is an array prefix

有用的win11小技巧

Vulnhub tre1