当前位置:网站首页>Understand chisel language thoroughly 06. Chisel Foundation (III) -- registers and counters

Understand chisel language thoroughly 06. Chisel Foundation (III) -- registers and counters

2022-07-04 14:08:00 【github-3rr0r】

Chisel Basics ( 3、 ... and )—— Registers and counters

Chisel In the last part of the foundation, we introduced Chisel Operators and combinatorial logic in , But to construct complex digital logic circuits , It is not enough to have combinational circuits , Because combinational circuits have no state information . This part introduces the basic components used to describe the state information of digital circuits , That's what we all know register (Register). After introducing registers and operations on registers , We will implement a counter with registers .

register

Chisel Register components are provided in , The essence is D- trigger (D flip-flops) Set ,D- The concept of trigger belongs to the category of digital logic circuit , Don't start here , We can abstract it into registers .

Chisel The registers in are implicitly connected to the global clock , And on every clock The rising edge updates the register Value .

When providing an initialization value when declaring a register , Registers will use Synchronous reset The signal .

The value stored in the register can be any number that can be represented as a set of bits Chisel type , The following code defines a bit width of 8 The register of , It will be initialized to 0:

val reg = RegInit(0.U(8.W))

Enter the update operator := Connect to register , The output of the register can be directly referenced by the register name , Used in expressions :

reg := d

val q = reg

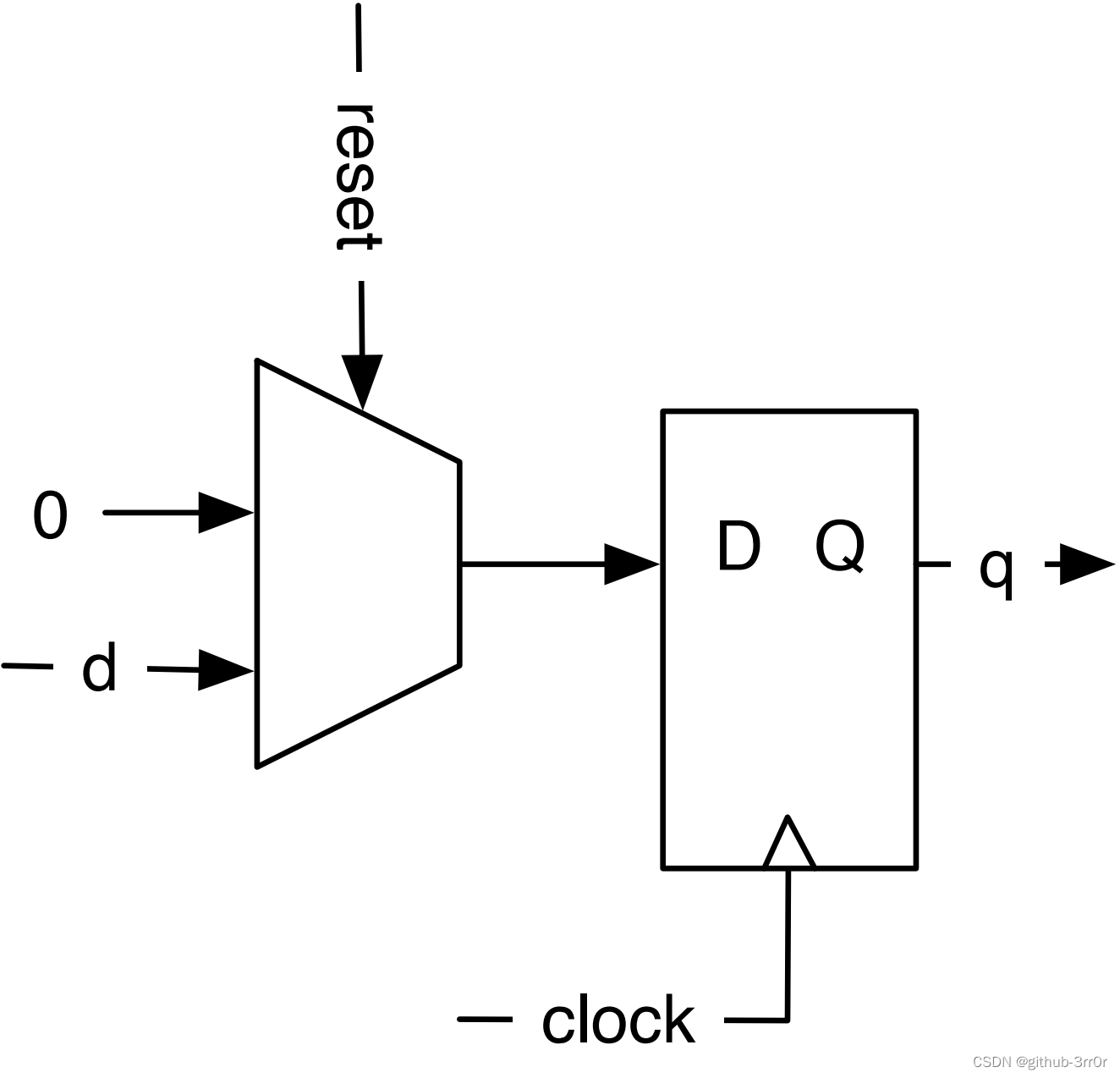

The register circuit defined by the above three lines of code is shown in the following figure , Including a Implicit The clock signal of clock、 An initialization register is 0.U Implicit synchronous reset signal reset、 Input signal d And output signal q, Global signal global and reset Are implicitly connected to each register :

Registers can also be used RegNext() To define , The parameters are its input and a constant as the initial value :

val bothReg = RegNext(d, 0.U)

In order to distinguish between combinational logic and register signals when writing code , Usually, when naming, the register will be suffixed Reg. Another common method , Commonly used in Java and Scala, Is the use of camelCase( Hump nomenclature ), Use multiple words as identifiers . In this way , Functions and variables start with lowercase , And category ( type ), For example, the module name , Just start with uppercase .

Chisel The naming in is relatively free , But it's best to use a good-looking and descriptive name . And it's important to note that ,Scala and Chisel Keywords in cannot be named . And about the Chisel Code specification of , I will write an article later .

Chisel Register and Mux Implementation counter

Counter is a very basic component in digital system , Such as performance counters 、 Program counter, etc . We may use registers to record the number of events , But more often it is used to define a time interval . That is, the counter records the number of clock cycles , When reaching a certain number ( After this time interval ) Trigger an action .

The simple method is to reset the counter when it reaches a certain upper limit . It should be noted that , Computer science and digital design , Counting is from 0 At the beginning , So if you want to count to 10, That's from 0 Count to 9.

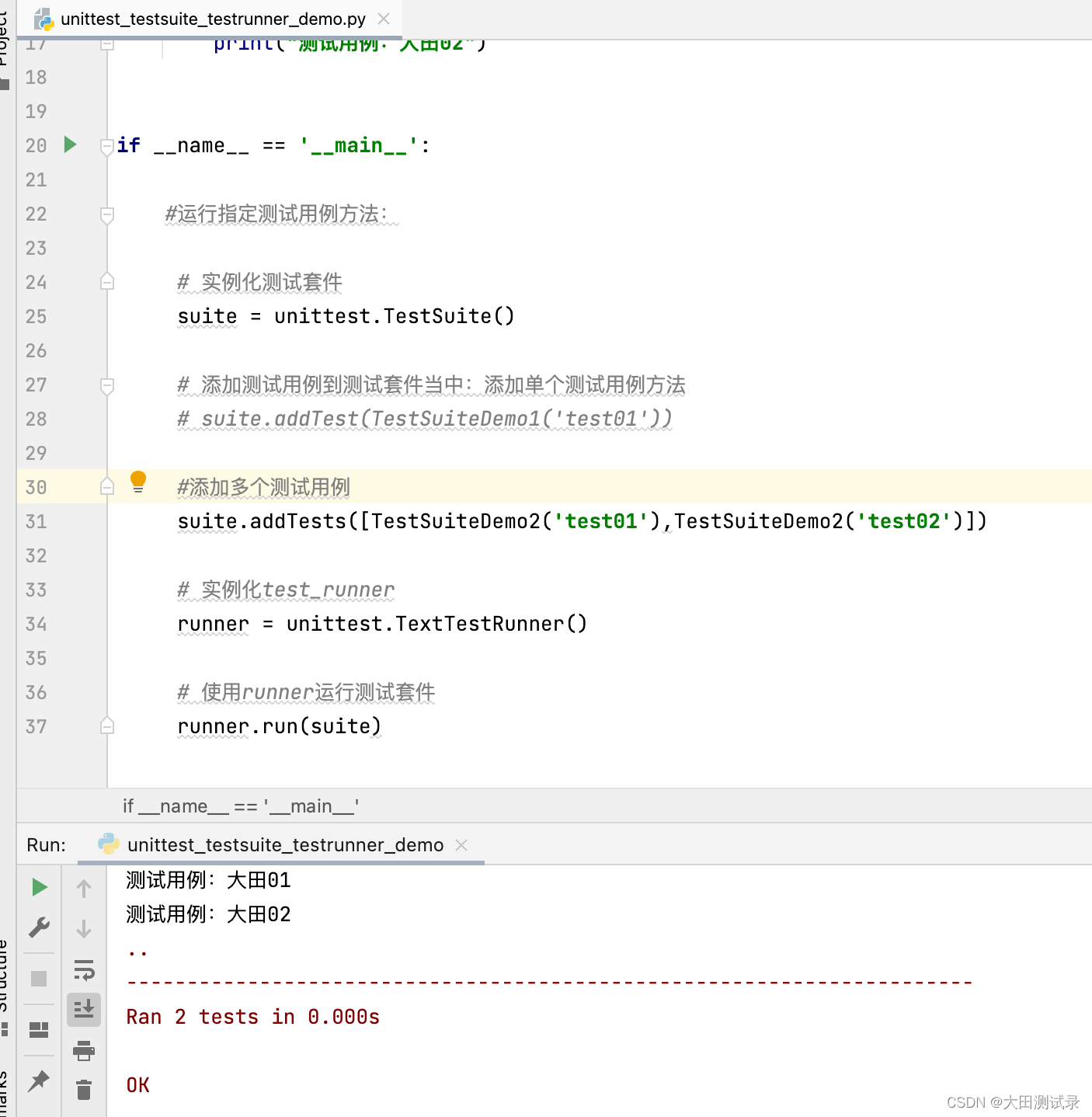

The following code implements a counter , Count up to 9, Then start again 0 Count to 9:

val cntReg = RegInit(0.U(8.W))

cntReg := Mux(cntReg === 9.U, 0.U, cntReg + 1.U)

Yes, of course ,Chisel There are counters in the standard components Counter Of , We'll talk about that later !

Although I say Chisel Will infer the required bit width for signals and registers , But it is better to specify the desired bit width when creating hardware objects . On most occasions , It is also best to give the register a known reset initialization value :

val reg = RegInit(0.S(8.W))

If no initialization value is given , Let the register value be undefined at reset , It may save a reset loading network , But it will be much easier if the reset value is known during testing and verification .

Conclusion

There is not much about registers , But registers are modules with status information , It also implicitly introduces a clock , Therefore, it is the basis of sequential circuits . Then the combinational circuit has , Sequential circuits also exist , Theoretically, we can do whatever we want to achieve any digital circuit , It's also natural to implement a processor . In the next section, we will discuss Chisel Medium Bundle and Vec To introduce , This is the pit dug in the last section , These two structures can bring us a lot of convenience in writing code !

边栏推荐

- Unittest框架中引入TestFixture

- 美国土安全部部长警告移民“不要踏上危险的旅程”

- Detailed explanation of Fisher information quantity detection countermeasure sample code

- Byte interview algorithm question

- 392. 判断子序列

- 205. 同构字符串

- 小程序直播 + 电商,想做新零售电商就用它吧!

- Animation and transition effects

- FS7867S是一款应用于数字系统供电电源电压监控的电压检测芯片

- The Secretary of Homeland Security warned immigrants "not to embark on a dangerous journey"

猜你喜欢

【Matlab】conv、filter、conv2、filter2和imfilter卷积函数总结

Yingshi Ruida rushes to the scientific and Technological Innovation Board: the annual revenue is 450million and the proposed fund-raising is 979million

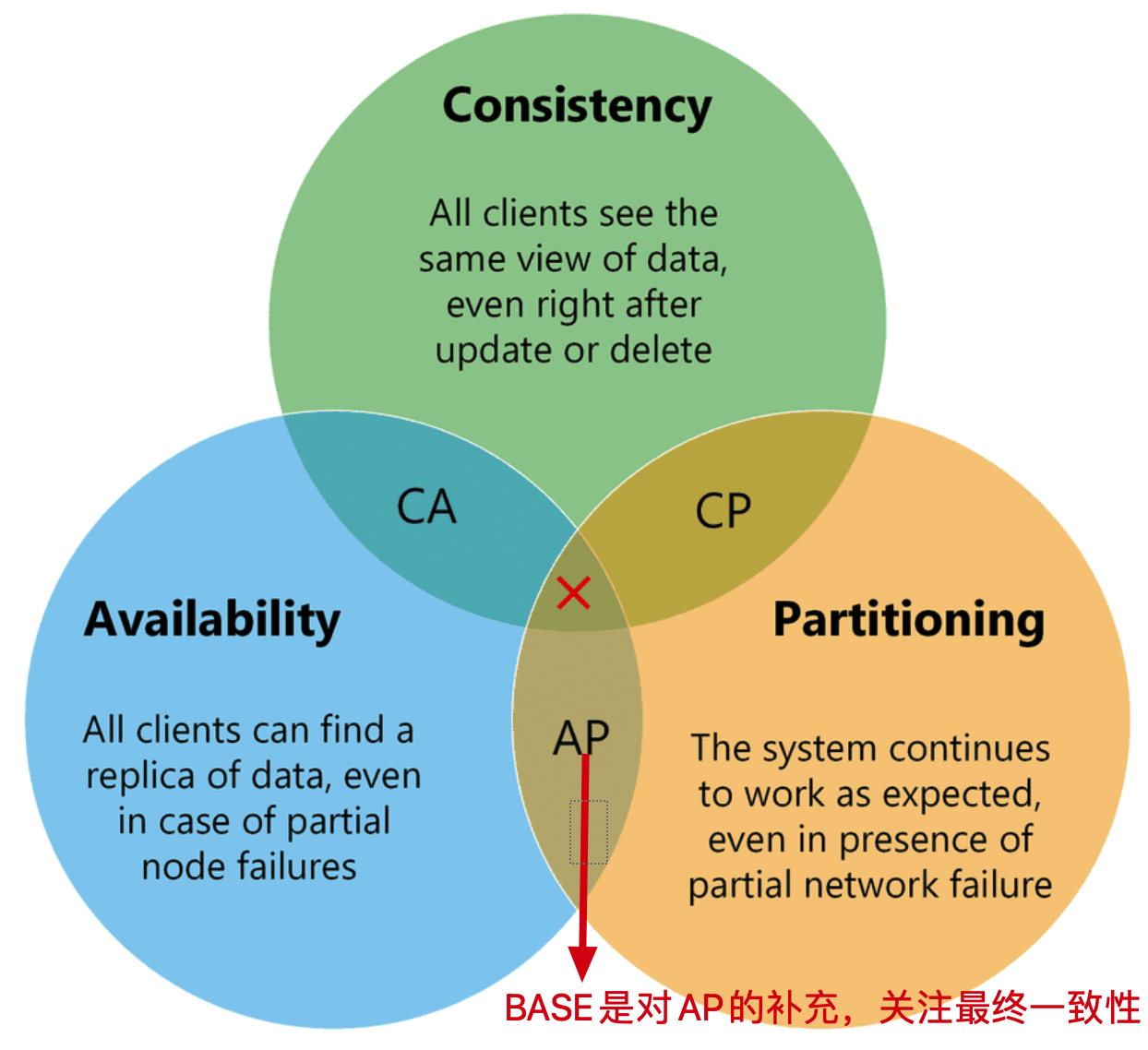

Distributed base theory

中邮科技冲刺科创板:年营收20.58亿 邮政集团是大股东

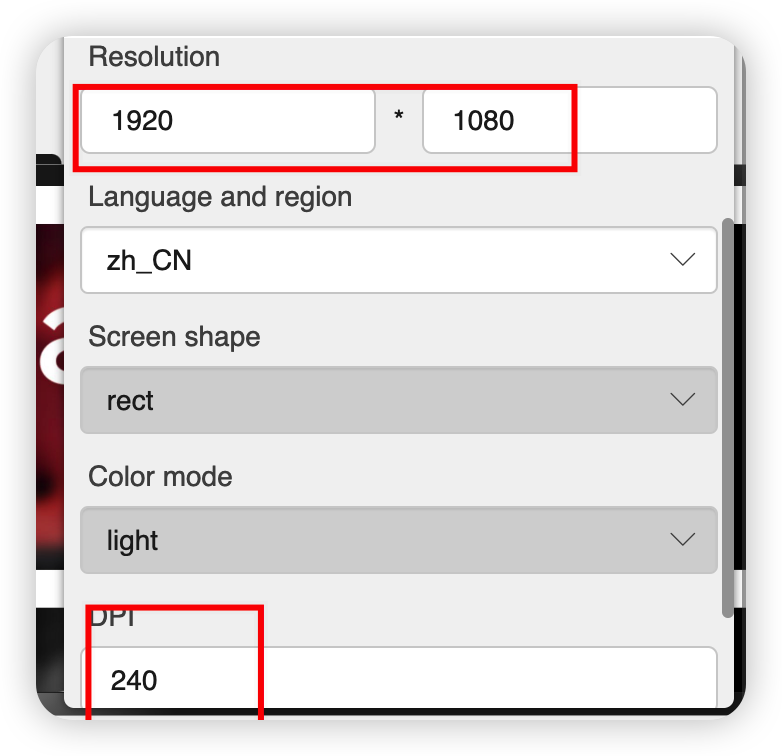

OpenHarmony应用开发之如何创建DAYU200预览器

ASP. Net core introduction I

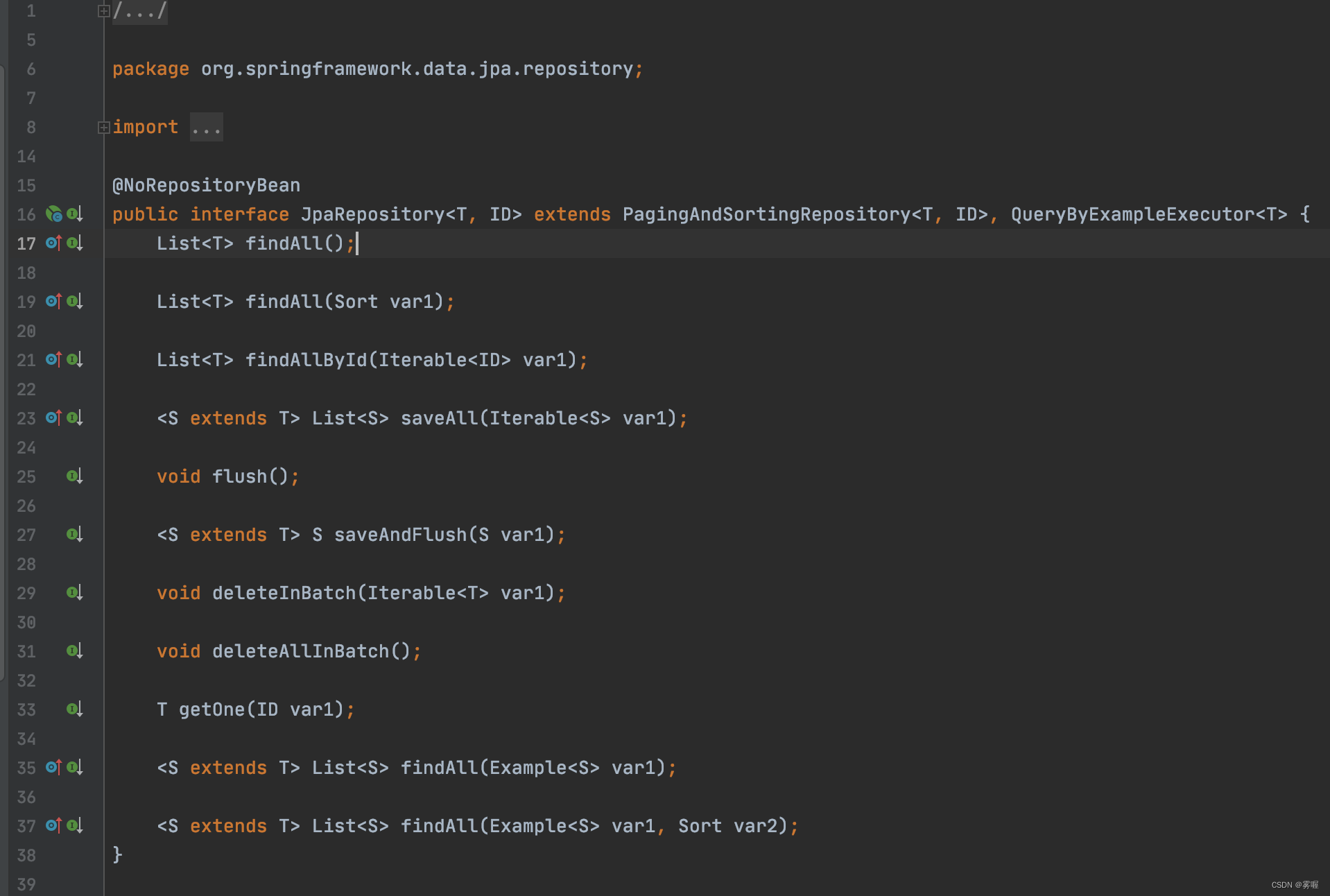

Unittest中的TestSuite和TestRunner

逆向调试入门-PE结构-资源表07/07

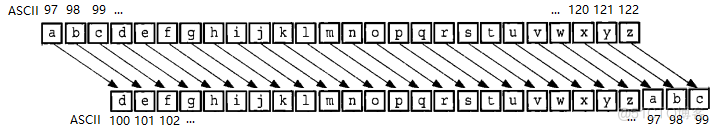

Getting started with the go language is simple: go implements the Caesar password

Summary of recent days (non-technical article)

随机推荐

One of the solutions for unity not recognizing riders

自主工业软件的创新与发展

ASP. Net core introduction I

Service Mesh的基本模式

sharding key type not supported

How to choose a technology stack for web applications in 2022

2022年起重机械指挥考试模拟100题模拟考试平台操作

DGraph: 大规模动态图数据集

JVM series - stack and heap, method area day1-2

安装trinity、解决报错

BLOB,TEXT GEOMETRY or JSON column 'xxx' can't have a default value query 问题

2022 practice questions and mock exams for the main principals of hazardous chemical business units

中邮科技冲刺科创板:年营收20.58亿 邮政集团是大股东

Detailed explanation of Fisher information quantity detection countermeasure sample code

Animation and transition effects

Qt如何实现打包,实现EXE分享

. Net delay queue

MySQL 5 installation and modification free

OpenHarmony应用开发之如何创建DAYU200预览器

OPPO Find N2产品形态首曝:补齐各项短板