当前位置:网站首页>CPU design practice - Chapter 4 practice task 3 use pre delivery technology to solve conflicts caused by related issues

CPU design practice - Chapter 4 practice task 3 use pre delivery technology to solve conflicts caused by related issues

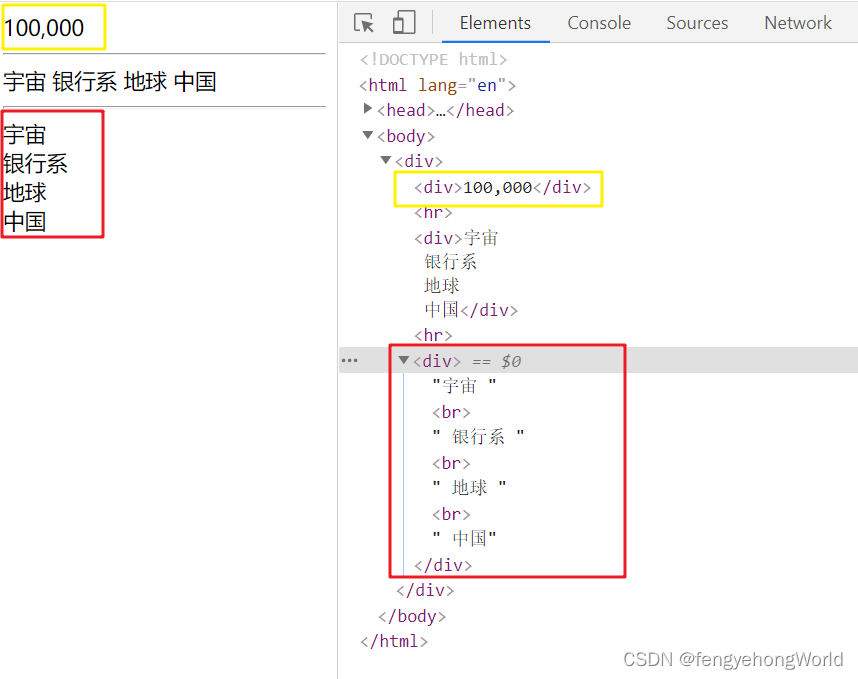

2022-07-05 14:38:00 【Xiaowei programmer】

Solve the conflict caused by data correlation with forward delivery technology

Preface

Practice task three is in Practical task 2 On the basis of the above !!!

stay lab4 In an experimental environment , Add the corresponding code and use the pre delivery technology to solve the conflicts caused by related , Finally, the simulation time is less than that of practical task two .

experiment

1. Add the execution level 、 The data of memory access level or write back level is delivered to the data path of decoding level

At the decoding level, it is judged that the current time is at the execution level 、 Whether the register number of the destination operand of the memory access level or write back level instruction is the same as that of the source operand of the decoding level , Indicates that data correlation has occurred , The execution level 、 The data of the memory access level or write back level is delivered to the decoding level . The code is as follows :

EXE_stage:

output [31:0] EXE_result, // Executive level

assign EXE_result = es_alu_result;

MEM_stage:

output [31:0] MEM_result

assign MEM_result = ms_final_result;

WB_stage:

output [31:0] WB_result

assign WB_result = ws_final_result;

ID_stage:

input [31:0] EXE_result,

input [31:0] MEM_result,

input [31:0] WB_result,

stay mycpu_top Add the corresponding signal to the instantiation of the corresponding module :

// Instantiate the line declaration used

wire [31:0] EXE_result;

wire [31:0] MEM_result;

wire [31:0] WB_result;

ID_stage:

.EXE_result (EXE_result),

.MEM_result (MEM_result),

.WB_result (WB_result)

EXE_stage:

.EXE_result (EXE_result)

MEM_stage:

.MEM_result (MEM_result)

WB_stage:

.WB_result (WB_result)

2. It is the execution level that needs to be delivered before judgment 、 Data at the access level or write back level

At the decoding level, we get that the current time is at the execution level 、 The instructions of memory access level and write back level need to be finally written back to the destination operand of the register , Next, we need to generate corresponding logic to judge that what needs to be passed forward is the execution level 、 Data at the access level or write back level . The code modified at the decoding level is as follows :

// Delete

/* assign rs_value = rf_rdata1; assign rt_value = rf_rdata2; */

// add to -begin

assign rs_value = rs_wait ? (rs == EXE_dest ? EXE_result :

rs == MEM_dest ? MEM_result : WB_result)

: rf_rdata1;

assign rt_value = rt_wait ? (rt == EXE_dest ? EXE_result :

rt == MEM_dest ? MEM_result : WB_result)

: rf_rdata2;

assign ds_ready_go = ds_valid & ~load_stall;

//load_stall In practice, task 2 has been added , It means the first one i The first instruction is load Instructions , The first i+1 Orders

// and load Instruction occurrence data correlation , At this time, the data that needs to be delivered in advance is not ready , Pipeline pause required .

// add to -end

experimental result

Simulation results :

launch_simulation: Time (s): cpu = 00:00:05 ; elapsed = 00:00:12 . Memory (MB): peak = 958.809 ; gain = 0.000

Tested :

----PASS!!!

run: Time (s): cpu = 00:00:18 ; elapsed = 00:00:16 . Memory (MB): peak = 958.809 ; gain = 0.000

边栏推荐

- Strong connection component

- 【NVMe2.0b 14-9】NVMe SR-IOV

- Explain Vue's plan to clean up keepalive cache in time

- 一网打尽异步神器CompletableFuture

- Longest common subsequence dynamic programming

- 矩阵链乘 - 动态规划实例

- 黑马程序员-软件测试-10阶段2-linux和数据库-44-57为什么学习数据库,数据库分类关系型数据库的说明Navicat操作数据的说明,Navicat操作数据库连接说明,Navicat的基本使用,

- Qingda KeYue rushes to the science and Innovation Board: the annual revenue is 200million, and it is proposed to raise 750million

- freesurfer运行完recon-all怎么快速查看有没有报错?——核心命令tail重定向

- [summary of leetcode weekly competition] the 81st fortnight competition of leetcode (6.25)

猜你喜欢

家用电器行业商业供应链协同平台解决方案:供应链系统管理精益化,助推企业智造升级

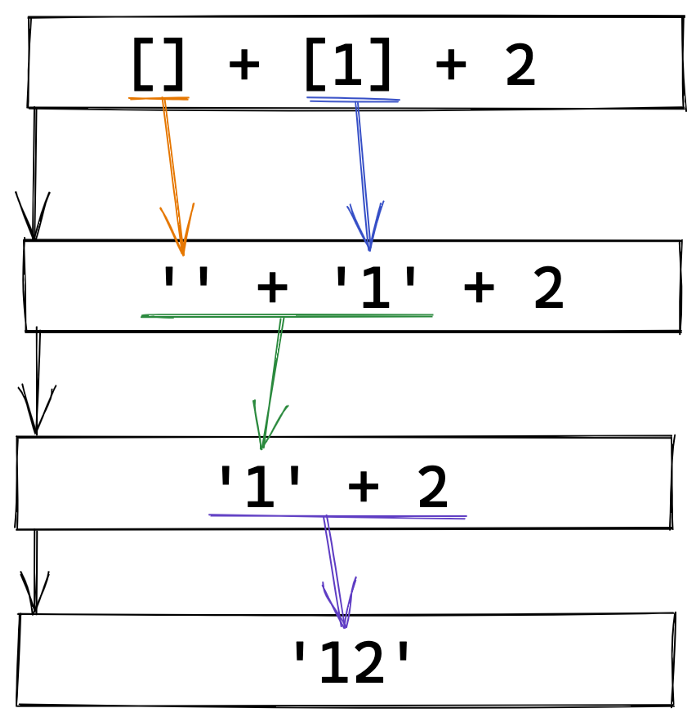

分享 20 个稀奇古怪的 JS 表达式,看看你能答对多少

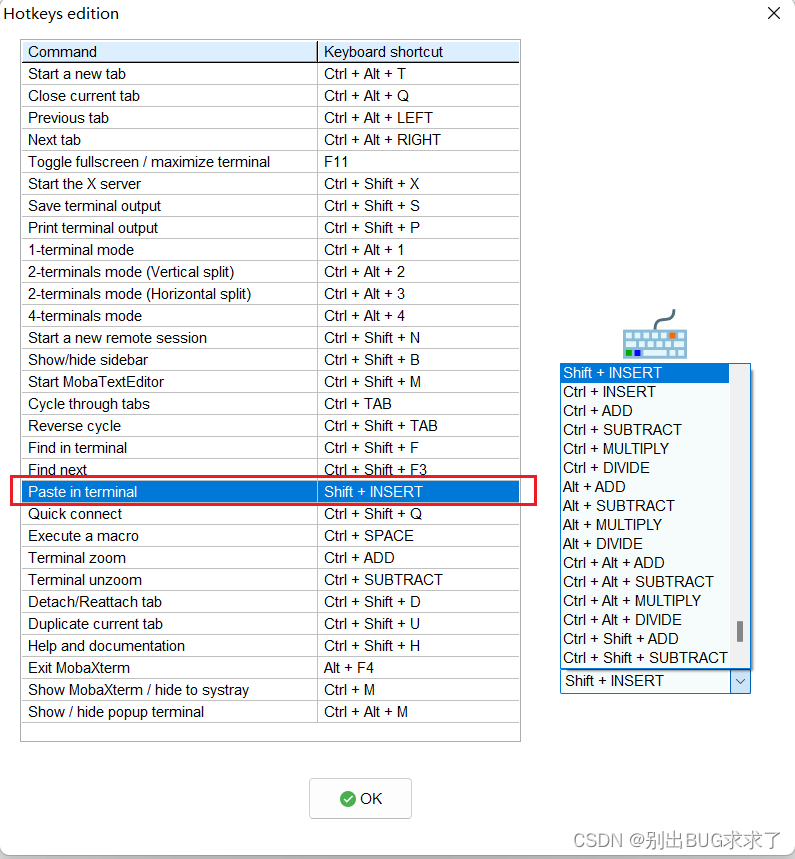

如何将电脑复制的内容粘贴进MobaXterm?如何复制粘贴

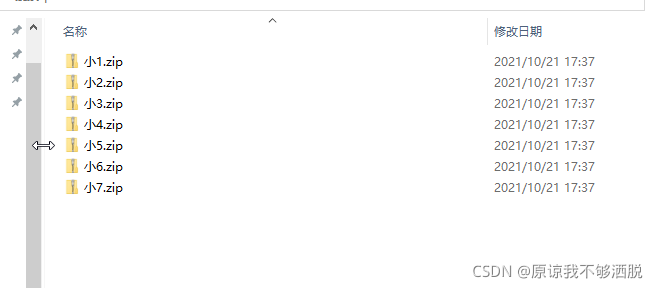

一键更改多个文件名字

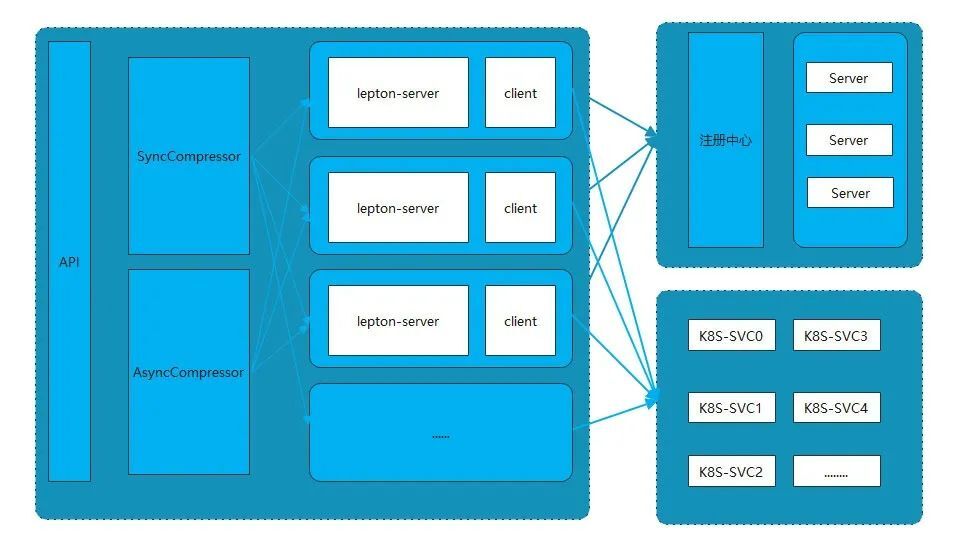

Lepton 无损压缩原理及性能分析

![[summary of leetcode weekly competition] the 81st fortnight competition of leetcode (6.25)](/img/d7/f49bca8da2ce286c18508325985990.png)

[summary of leetcode weekly competition] the 81st fortnight competition of leetcode (6.25)

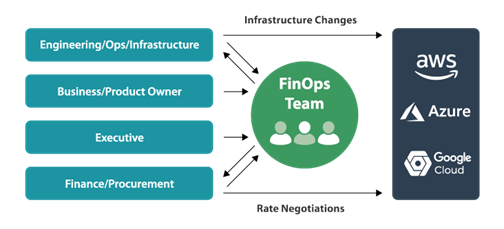

非技术部门,如何参与 DevOps?

Solution of commercial supply chain collaboration platform in household appliance industry: lean supply chain system management, boosting enterprise intelligent manufacturing upgrading

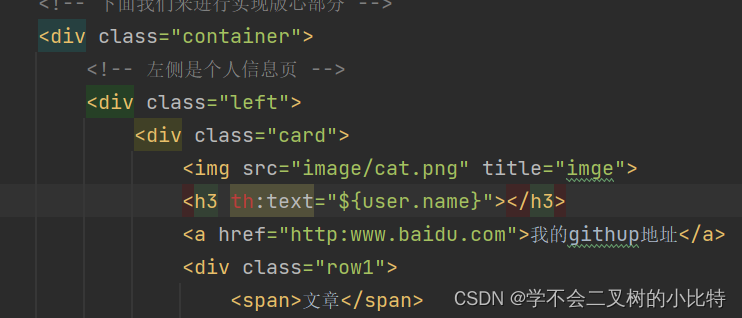

Implement a blog system -- using template engine technology

Thymeleaf 使用后台自定义工具类处理文本

随机推荐

Niuke: intercepting missiles

How to open an account of qiniu securities? Is it safe to open an account?

mysql8.0JSON_ Instructions for using contains

【NVMe2.0b 14-9】NVMe SR-IOV

03_ Dataimport of Solr

LeetCode_ 3 (longest substring without repeated characters)

分享 20 个稀奇古怪的 JS 表达式,看看你能答对多少

C语言中限定符的作用

强联通分量

CPU设计相关笔记

最长公共子序列 - 动态规划

Thymeleaf 使用后台自定义工具类处理文本

启牛学堂班主任给的证券账户安全吗?能开户吗?

Chow Tai Fook fulfills the "centenary commitment" and sincerely serves to promote green environmental protection

Catch all asynchronous artifact completable future

Opengauss database source code analysis series articles -- detailed explanation of dense equivalent query technology (Part 2)

Un week - end heureux

超级哇塞的快排,你值得学会!

【招聘岗位】基础设施软件开发人员

Shanghai under layoffs