当前位置:网站首页>CPU设计相关笔记

CPU设计相关笔记

2022-07-05 14:31:00 【小威程序员】

CPU设计-基于LoongArch架构的MIPS

1. 简单说说流水线CPU

单发射静态五级流水线CPU:

取指(IF)->译码(ID)->执行(EXE)->访存(MEM)->写回(WB)

流水线CPU设计的精髓理解起来就像是流水线生产的工场一样,一个阶段单独完成一项指定的功能。

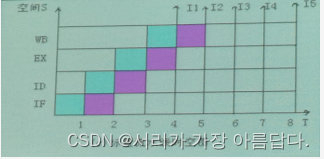

(1)时间流水

以五段流水为例,五段为:取指-译码-访存-执行-回写

把每一段当做一部分,在前一条指令由取指到译码阶段时,即开始下一条指令的取指。

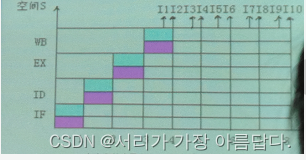

(2)空间流水

类比时间流水,简单理解为把每一部分扩充为原来工作效率的n倍;即原来在取指阶段一下取一条指令,现在可以一下取2条或多条。

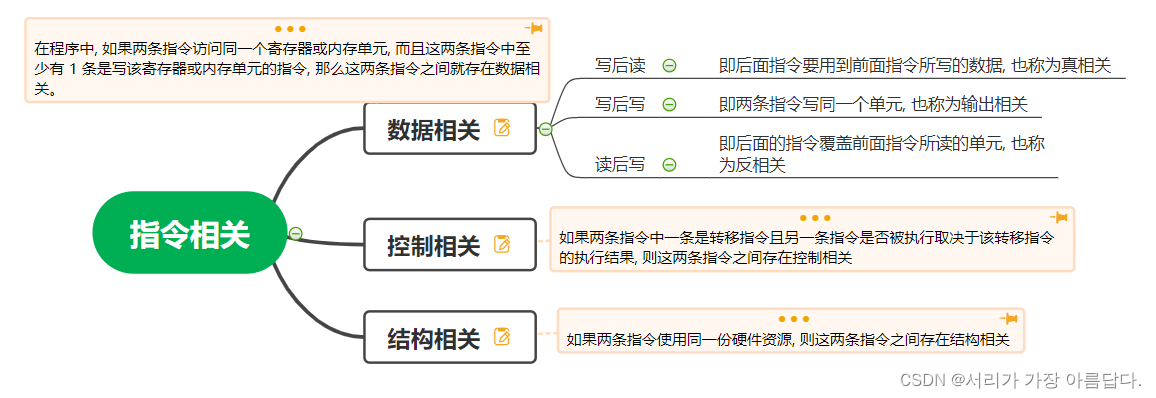

2.流水线CPU中的指令相关与流水线冲突

3.解决流水线CPU设计中的数据相关冲突方法

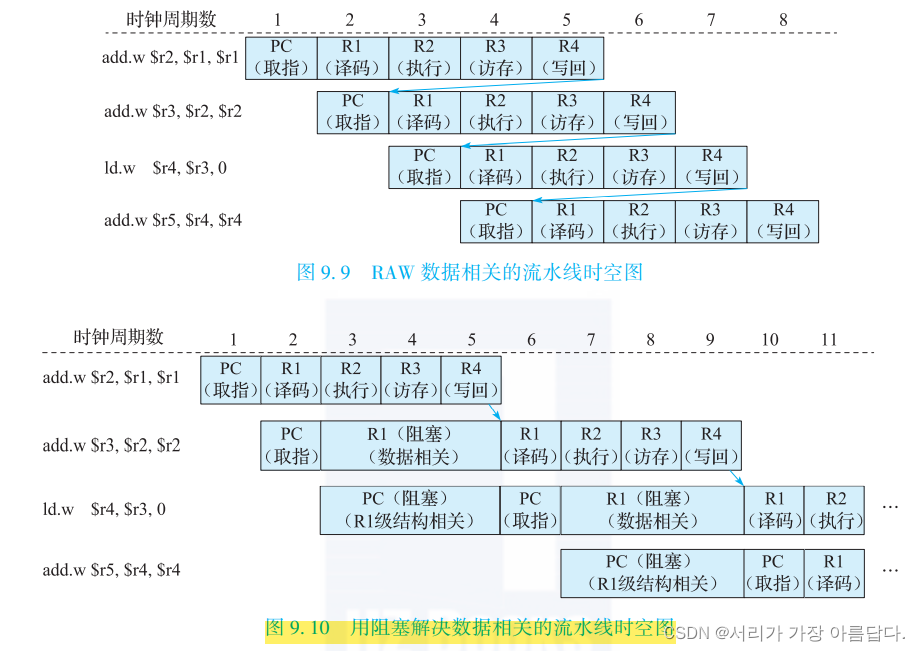

(1) 阻塞技术

简单理解:让下一条指令的某一级停下来去等待上面指令出来最后的待用结果,即等到上面指令已完全完成五级流水操作。

与“写后读”相关引发的冲突:即上一级还未写入寄存器或数据RAM而紧接着的下一条指令在执行阶段已经需要用到这个新值。

阻塞技术:让下一条指令在执行阶段等待上一条指令完成整个指令。

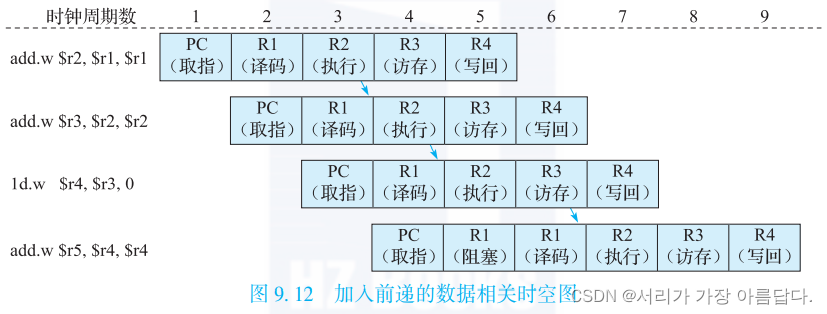

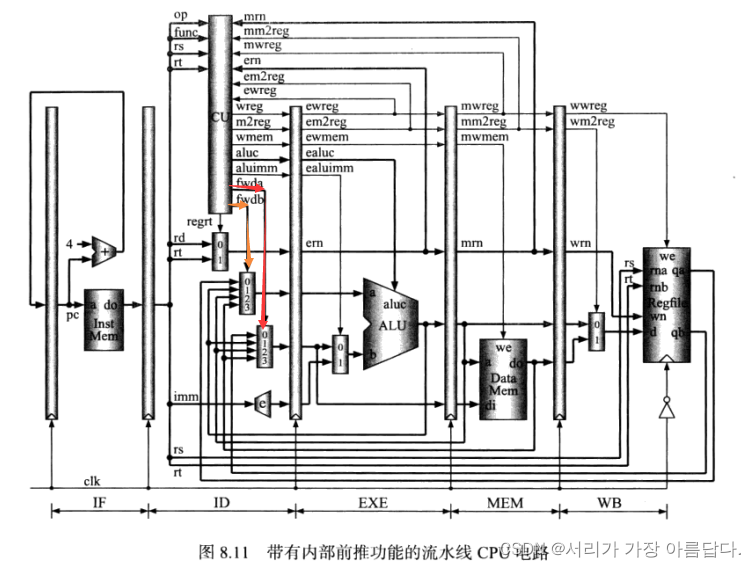

(2) 前递技术

简单理解:将出来的待用结果直接通过专用路径送到相应的流水级阶段,不用等到最后一段的写回操作。

解决与“写后读”相关引发的冲突:

前递技术:上一条指令需要写入的结果出来之后直接送到下一条指令需要的流水阶段。 我把刚刚出炉的新鲜的加法结果直接送给下一条指令去吃.这就是所谓内部前推(Internal Forwarding),或称内部旁路(Bypass)。

我把刚刚出炉的新鲜的加法结果直接送给下一条指令去吃.这就是所谓内部前推(Internal Forwarding),或称内部旁路(Bypass)。

参考文献:

《CPU设计实战》汪文祥 邢金璋 著

《计算机体系结构基础 第三版》 胡传武等著

《计算机原理与设计:Verilog HDL版》 李亚民著

边栏推荐

- 想进阿里必须啃透的12道MySQL面试题

- How to call the function mode of one hand and one machine

- Introduction, installation, introduction and detailed introduction to postman!

- Shenziyu, the new chairman of Meizu: Mr. Huang Zhang, the founder, will serve as the strategic adviser of Meizu's scientific and technological products

- 【学习笔记】阶段测试1

- 注意!软件供应链安全挑战持续升级

- Webrtc learning (II)

- [learning notes] connectivity and circuit of graph

- R語言ggplot2可視化:可視化折線圖、使用theme函數中的legend.position參數自定義圖例的比特置

- 周大福践行「百周年承诺」,真诚服务推动绿色环保

猜你喜欢

【leetcode周赛总结】LeetCode第 81 场双周赛(6.25)

软件测试人在深圳有哪些值得去的互联网公司【软件测试人员专供版】

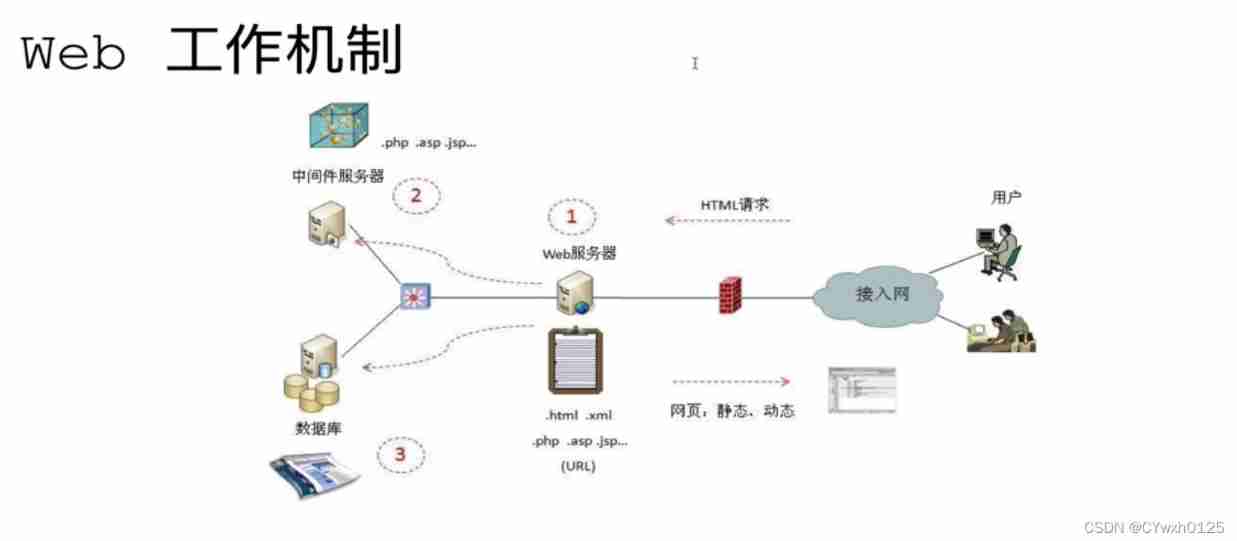

Security analysis of Web Architecture

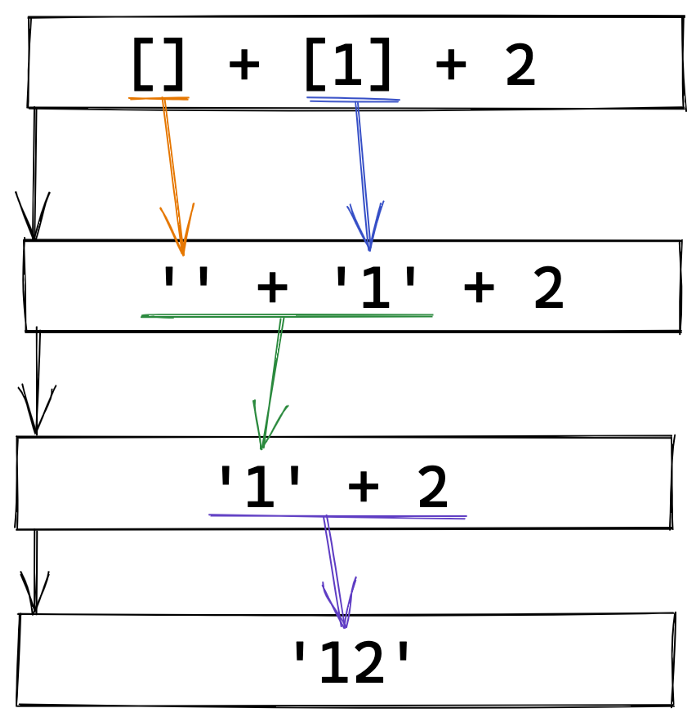

Share 20 strange JS expressions and see how many correct answers you can get

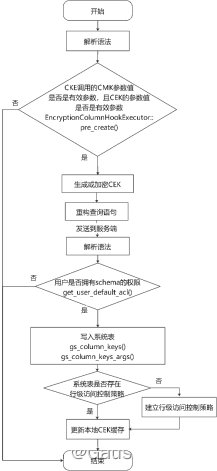

Opengauss database source code analysis series articles -- detailed explanation of dense equivalent query technology (Part 2)

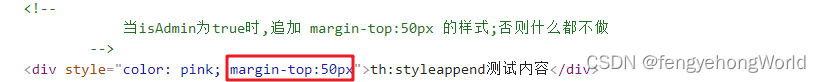

Thymeleaf th:classappend属性追加 th:styleappend样式追加 th:data-自定义属性

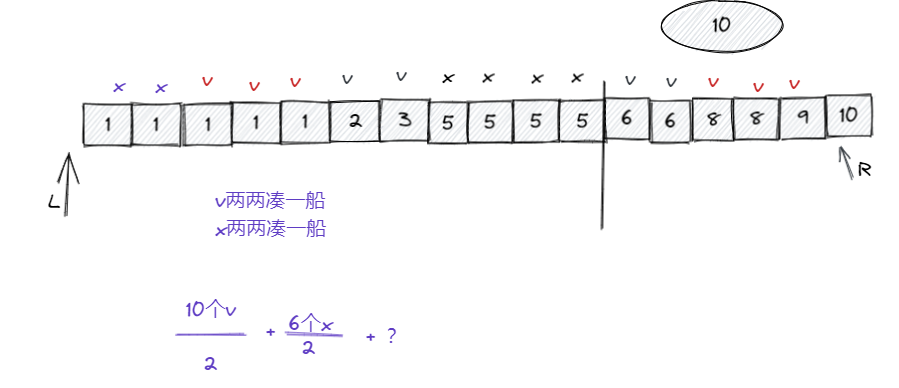

leetcode:881. 救生艇

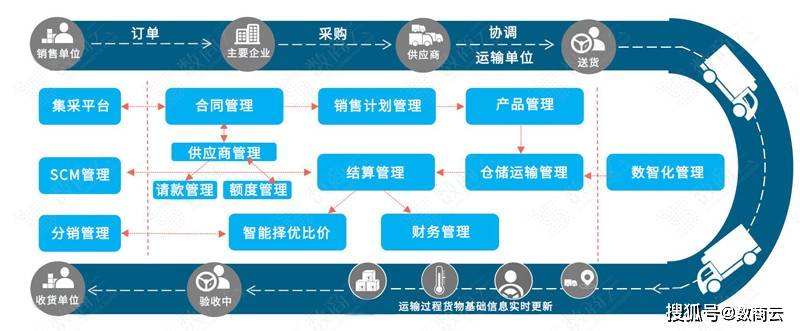

家用电器行业商业供应链协同平台解决方案:供应链系统管理精益化,助推企业智造升级

Countermeasures of enterprise supply chain management system in UCA Era

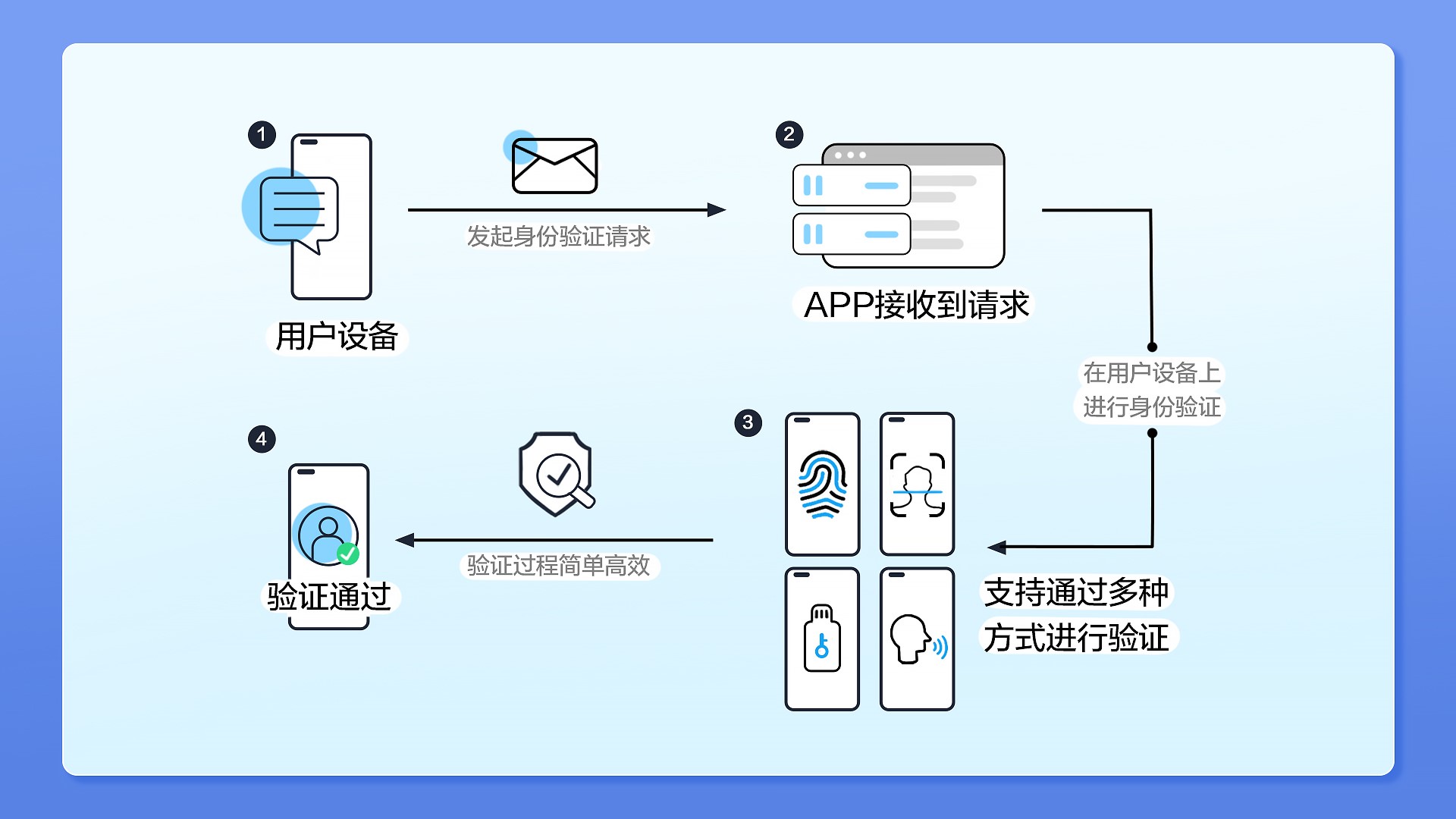

无密码身份验证如何保障用户隐私安全?

随机推荐

CyCa children's physical etiquette Ningbo training results assessment came to a successful conclusion

Is it OK to open the securities account on the excavation finance? Is it safe?

Fonctions communes de thymeleaf

网上电子元器件采购商城:打破采购环节信息不对称难题,赋能企业高效协同管理

R language dplyr package select function, group_ By function, mutate function and cumsum function calculate the cumulative value of the specified numerical variable in the dataframe grouping data and

Strong connection component

Structure - C language

Judge whether the variable is an array

总量分析 核算方法和势方法 - 分摊分析

Countermeasures of enterprise supply chain management system in UCA Era

Thymeleaf 常用函数

openGauss数据库源码解析系列文章—— 密态等值查询技术详解(下)

Tiflash compiler oriented automatic vectorization acceleration

Enjoy what you want. Zhichuang future

Which Internet companies are worth going to in Shenzhen for software testers [Special Edition for software testers]

04_ Use of solrj7.3 of solr7.3

【招聘岗位】基础设施软件开发人员

How to make a second clip of our media video without infringement

R language ggplot2 visualization: visual line graph, using legend in theme function The position parameter defines the position of the legend

Intelligent supply chain collaboration system solution for daily chemical products industry: digital intelligent SCM supply chain, which is the "acceleration" of enterprise transformation