当前位置:网站首页>UART Application Design and Simulation Verification 2 - TX Module Design (Stateless machine)

UART Application Design and Simulation Verification 2 - TX Module Design (Stateless machine)

2022-07-05 23:10:00 【Shaoqing n'est pas au temple Dali.】

Préface:C'est quelques mois après avoir revu ce petit projet,Dans les études ultérieures,Le nouveau professeur n'arrête pas de souligner,Réduire au minimum l'utilisation de la machine d'état dans le travail réel,J'ai oublié ce qu'il a dit quand j'ai trié l'article.Alors j'ai essayé de le réécrire moi - mêmeUART,Organiser une version sans machine d'état.

Voici quelques points logiques de base à revoir:

1)Le format complet de données d'un cadre contient:Position initiale,Bits de données valides,Bit de contrôle,Stop bit;

2)Feuille de calculbitTemps de transmission des données:Utilisationbaoud(Taux de Baud)Etclk(Horloge système),Unités de taux de Baudbit per second,HorlogeHzUnitétime per second ,Donc l'horloge divisée par le taux de Baud donnetime per bit,C'est - à - direbitCombien de cycles d'horloge correspondent;

3)Signal de référence:Signal de transmissionbaoud_cnt_half,ChaquebitÀ mi - chemin,Transmission des données;Basculer le signal de comptagebaoud_cnt_end,ChaquebitQuand le comptage sera terminé,Passer au prochain cycle de comptage;Nombre de bitsbit_cnt,Calculer les chiffres passés dans un cadre de données;Signalisation du processus de transmissionstart_flag,Tout au long de chaque transmission de données.

Code supérieur:

//date:2022.6.30

//edgar.yao

//uart_tx block

module uart_tx(

input clk,

input rst_n,

input[7:0] cmd_data,

input data_valid,

output tx,

output tx_read边栏推荐

- Error when LabVIEW opens Ni instance finder

- Metasploit(msf)利用ms17_010(永恒之蓝)出现Encoding::UndefinedConversionError问题

- Week 17 homework

- 第十七周作业

- 一文搞定JVM的内存结构

- Expectation, variance and covariance

- Detailed explanation of pointer and array written test of C language

- Element operation and element waiting in Web Automation

- Shell: operator

- Registration and skills of hoisting machinery command examination in 2022

猜你喜欢

Nangou Gili hard Kai font TTF Download with installation tutorial

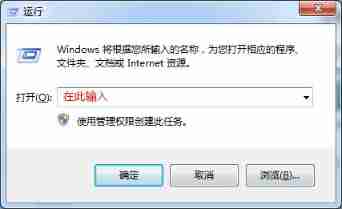

d3dx9_ How to repair 31.dll_ d3dx9_ 31. Solution to missing DLL

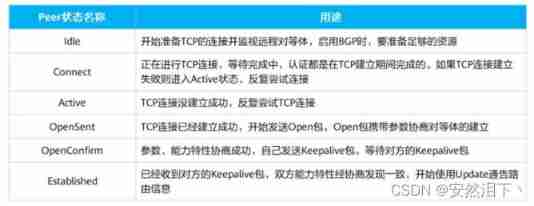

Hcip day 11 (BGP agreement)

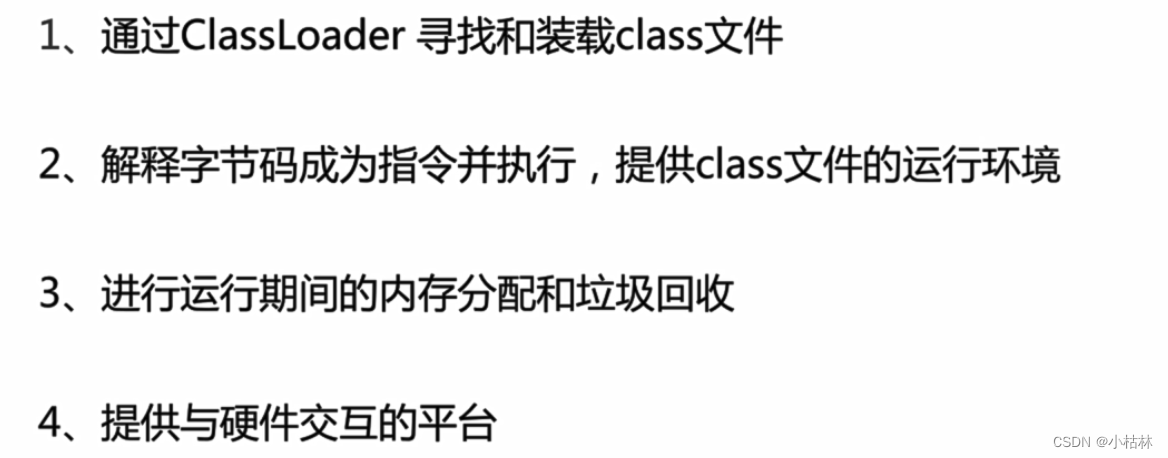

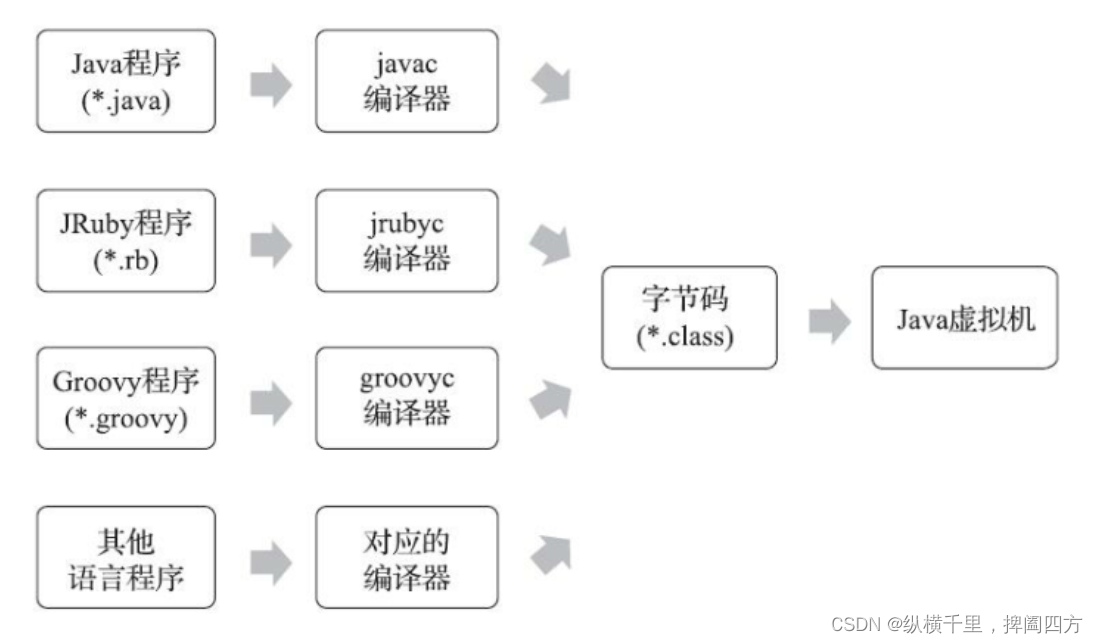

2:第一章:认识JVM规范1:JVM简介;

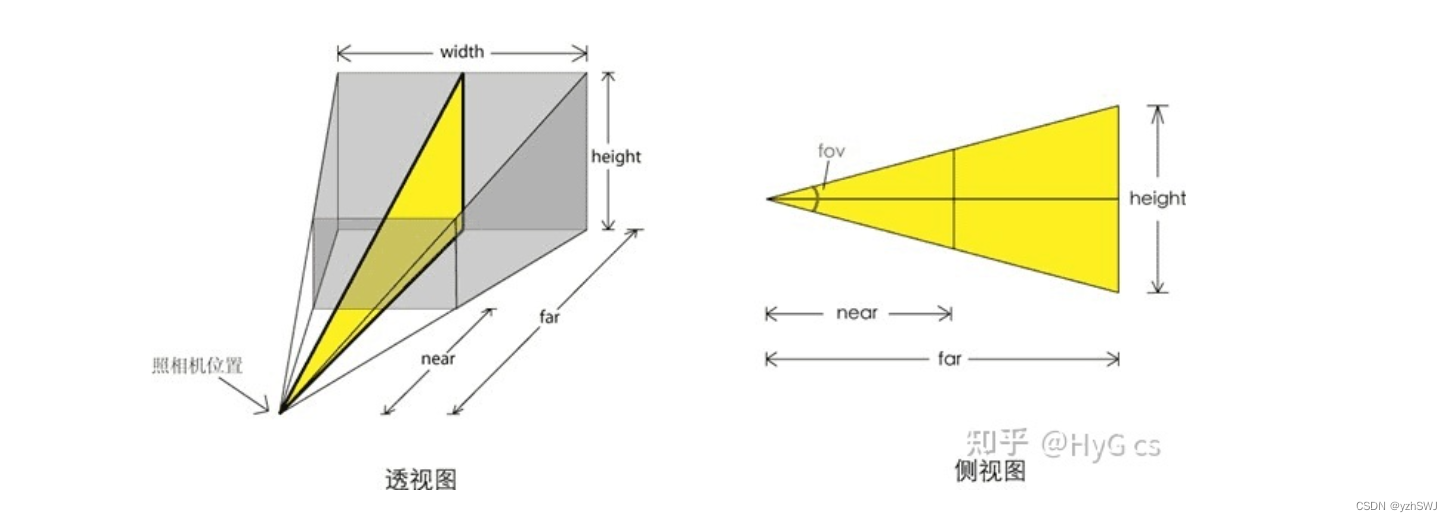

Three.js-01 入门

如何快速理解复杂业务,系统思考问题?

透彻理解JVM类加载子系统

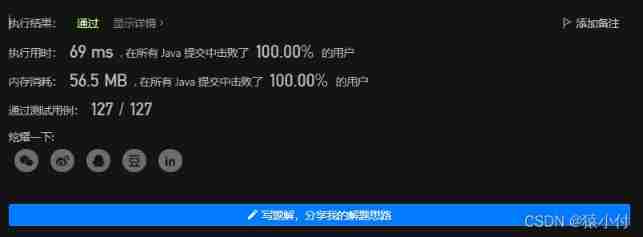

Leetcode weekly The 280 game of the week is still difficult for the special game of the week's beauty team ~ simple simulation + hash parity count + sorting simulation traversal

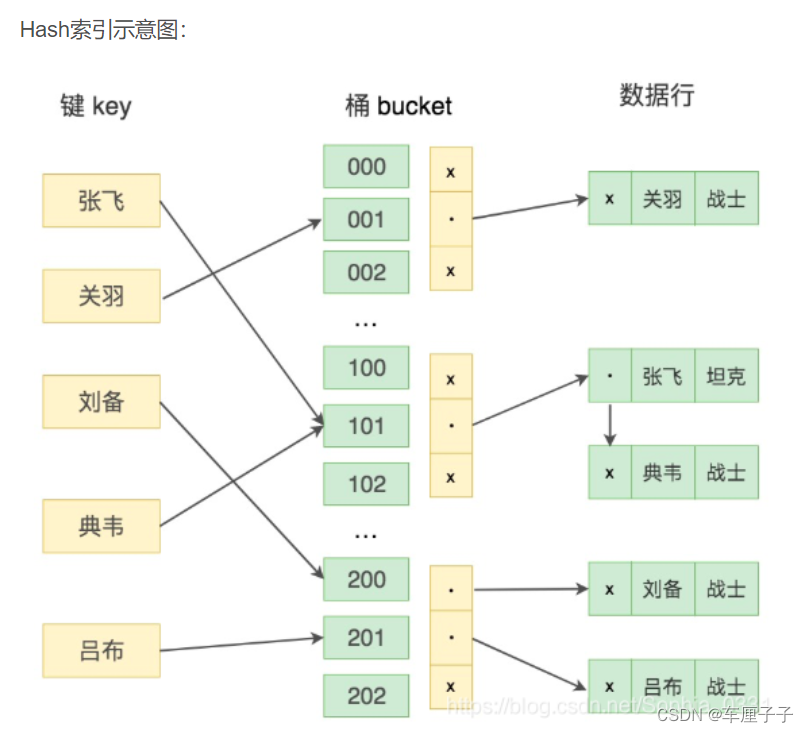

Basic knowledge of database (interview)

Non rigid / flexible point cloud ICP registration

随机推荐

Nangou Gili hard Kai font TTF Download with installation tutorial

Leetcode buys and sells stocks

[untitled]

Go语言实现原理——Map实现原理

Methods modified by static

ORB_ SLAM2/3

Calculating the number of daffodils in C language

CJ mccullem autograph: to dear Portland

2022 registration examination for safety management personnel of hazardous chemical business units and simulated reexamination examination for safety management personnel of hazardous chemical busines

Vcomp110.dll download -vcomp110 What if DLL is lost

d3dx9_ How to repair 31.dll_ d3dx9_ 31. Solution to missing DLL

Data type, variable declaration, global variable and i/o mapping of PLC programming basis (CoDeSys)

Codeforces Global Round 19

Overview of Fourier analysis

Registration and skills of hoisting machinery command examination in 2022

2:第一章:认识JVM规范1:JVM简介;

秒杀系统的设计与实现思路

Hcip day 11 (BGP agreement)

如何快速理解复杂业务,系统思考问题?

Global and Chinese market of water treatment technology 2022-2028: Research Report on technology, participants, trends, market size and share