当前位置:网站首页>Ram of IP core

Ram of IP core

2022-07-27 06:21:00 【Three assassins】

RAM IP Introduction to nuclear

- Single port RAM, Read and write operations share a set of address lines , Read and write operations cannot be performed at the same time

- Simple dual port RAM, Read and write operations have dedicated address ports ( A read port and a write port ), That is, the write port can only write but not read , The read port can only read but not write

- True dual port RAM, There are two address ports for read and write operations ( Two reads / Write the port ), That is, both ports can enter Line reading and writing .

True dual port RAM Interface signal

RAM IP Nuclear configuration

Single port RAM Configuration of

Simple double mouth RAM Configuration of

True dual port RAM Configuration of

RAM IP Nuclear use

RAM Control module

When you press the button 1 when (key1_flag=1) Explain to start going RAM The data is written in .RAM The writing sequence of is : When RAM The rising edge of the write clock is taken until the write enable is high , The data acquired by the rising edge can be written into the address acquired by the rising edge . So want to go RAM There must be a clock to write data in , Write enable , Address , Write data signal .

RAM Control module reference code (ram_ctrl.v)

module ram_ctrl

(

input wire sys_clk,

input wire sys_rst_n,

input wire wr_flag,

input wire rd_flag,

output reg wr_en, // Output write RAM Can make , High point level is effective

output reg [7:0] addr, // Output read / write RAM Address

output wire [7:0] wr_data, // Output write RAM Can make , High point level is effective

output reg rd_en // Output read RAM Can make , High active

);

parameter CNT_MAX =24'd9_999_999;

reg [23:0] cnt_200ms;

[email protected](posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_200ms <= 24'd0;

else if((cnt_200ms == CNT_MAX) || (wr_flag == 1'b1) || (rd_flag == 1'b1))

cnt_200ms <= 24'd0;

else if(rd_en == 1'b1)

cnt_200ms <= cnt_200ms + 1'b1;

//wr_en: Generate write RAM Enable signal

[email protected](posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

wr_en <= 1'b0;

else if(addr == 8'd255)

wr_en <= 1'b0;

else if(wr_flag == 1'b1)

wr_en <= 1'b1;

// When write enable is effective ,

[email protected](posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

addr <= 8'd0;

else if((addr == 8'd255&&wr_en == 1'b1) || (addr == 8'd255&&cnt_200ms == CNT_MAX)

|| (wr_flag == 1'b1) || (rd_flag == 1'b1))

addr <= 8'd0;

else if((wr_en == 1'b1) || (rd_en ==1'b1 && cnt_200ms == CNT_MAX))

addr <= addr + 1'b1;

// Make the written data equal to the number of addresses , That is, write data 0~255

assign wr_data = (wr_en == 1'b1) ? addr : 8'd0;

//rd_en: Generative reading RAM Enable signal

[email protected](posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

rd_en <= 1'b0;

else if(wr_flag == 1'b1)

rd_en <= 1'b0;

else if(rd_flag == 1'b1 && wr_en == 1'b0)

rd_en <= 1'b1;

else

rd_en <= rd_en;

endmodule

RAM Top level code module reference code (ram.v)

module ram

(

input wire sys_clk,

input wire sys_rst_n,

input wire wr_key,

input wire rd_key,

output wire ds,

output wire oe,

output wire shcp,

output wire stcp

);

wire wr_flag;

wire rd_flag;

wire wr_en ;

wire [7:0] addr ;

wire [7:0] wr_data;

wire rd_en ;

wire [7:0] out_data;

key_filter

#(

.CNT_MAX (20'd999_999)

)

key_filter_wr_inst

(

.sys_clk (sys_clk),

.sys_rst_n(sys_rst_n),

.key_in (wr_key),

.key_flag (wr_flag)

);

key_filter

#(

.CNT_MAX (20'd999_999)

)

key_filter_rd_inst

(

.sys_clk (sys_clk),

.sys_rst_n(sys_rst_n),

.key_in (rd_key),

.key_flag (rd_flag)

);

ram_ctrl ram_ctrl_inst

(

.sys_clk (sys_clk ),

.sys_rst_n(sys_rst_n),

.wr_flag (wr_flag ),

.rd_flag (rd_flag ),

.wr_en (wr_en ),

.addr (addr ),

.wr_data (wr_data),

.rd_en (rd_en )

);

ram_8x256_one ram_8x256_one_inst

(

.aclr ( ~sys_rst_n ),

.address ( addr ),

.clock ( sys_clk ),

.data ( wr_data ),

.rden ( rd_en ),

.wren ( wr_en ),

.q ( out_data )

);

seg_595_dynamic seg_595_dynamic_inst

(

.sys_clk (sys_clk ),

.sys_rst_n(sys_rst_n ),

.data ({12'b0,out_data} ),

.point (6'b000_000 ),

.sign (1'b0 ),

.seg_en (1'b1 ),

.ds (ds ),

.oe (oe ),

.shcp (shcp),

.stcp (stcp)

);

endmodule

RTL View

RAM IP Nuclear simulation

`timescale 1ns/1ns

module tb_ram();

reg sys_clk;

reg sys_rst_n;

reg wr_key;

reg rd_key;

wire ds ;

wire oe ;

wire shcp ;

wire stcp ;

initial

begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

wr_key = 1'b1;

rd_key = 1'b1;

#20

sys_rst_n <= 1'b1;

#10000

//rd_key

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#200

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#200000

//wr_key

#20

wr_key =1'b1;

#20

wr_key =1'b0;

#20

wr_key =1'b1;

#20

wr_key =1'b0;

#200

wr_key =1'b1;

#20

wr_key =1'b0;

#20

wr_key =1'b1;

#20

wr_key =1'b0;

#20

wr_key =1'b1;

#10000

//rd_key

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#200

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#200000

//rd_key

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#200

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

#20

rd_key =1'b0;

#20

rd_key =1'b1;

end

//sys_clk: Analog system clock , Every time 10ns The level is reversed once , The period is 20ns, The frequency is 50MHz

always #10 sys_clk = ~sys_clk;

// Redefine parameter values , Shorten the simulation time

defparam ram_inst.key_filter_wr_inst.CNT_MAX = 9;

defparam ram_inst.key_filter_rd_inst.CNT_MAX = 9;

defparam ram_inst.ram_ctrl_inst.CNT_MAX = 99;

ram ram_inst

(

.sys_clk (sys_clk ),

.sys_rst_n(sys_rst_n),

.wr_key (wr_key ),

.rd_key (rd_key ),

.ds (ds ),

.oe (oe ),

.shcp (shcp),

.stcp (stcp)

);

endmodule

边栏推荐

- Allow or prohibit connecting to a non domain and a domain network at the same time

- Robot navigation implementation

- Force buckle 110. Balanced binary tree

- 力扣题解 动态规划(5)

- Comparison of communication mechanisms

- 力扣 236. 二叉树的最近公共祖先

- 非真实感渲染(NPR)论文理解及其复现(Unity) - 《Stylized Highlights for Cartoon Rendering and Animation》

- What is the difference between single line and three line when renting servers in Hong Kong?

- IP核之PLL

- Solving binary tree with force deduction (8)

猜你喜欢

Tangent space and TBN matrix

Navigation related messages

Unity 实用小技巧(更新ing)

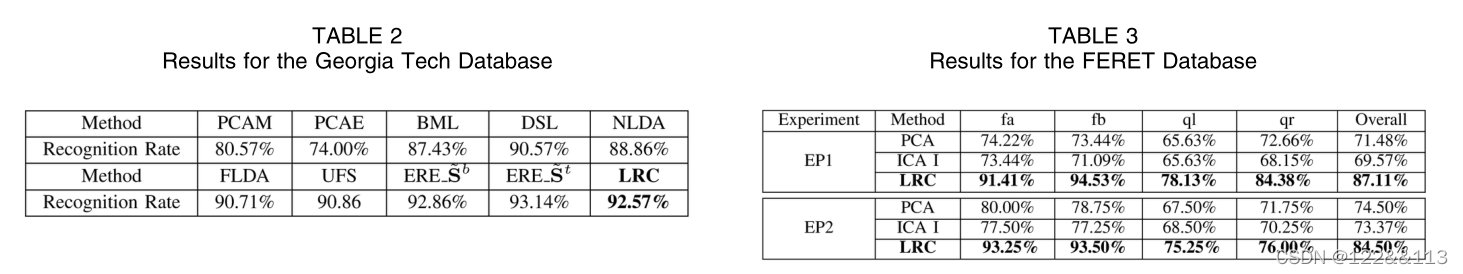

Linear progression for face recognition

5G网络身份识别---详解5G-GUTI

ROS通信机制进阶

Chapter for software testing

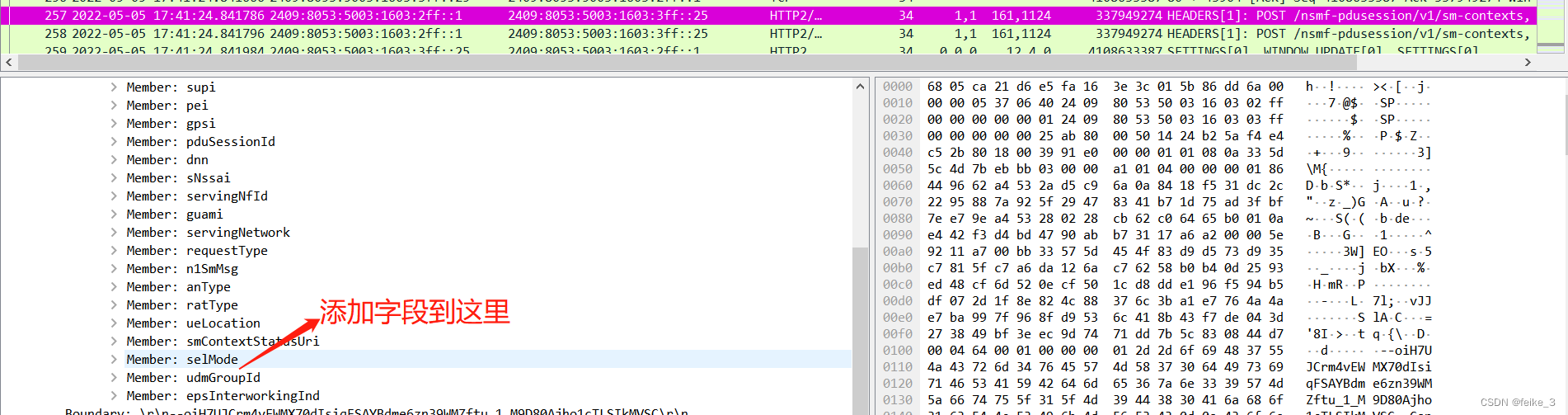

Wireshark packet modification -- adding or modifying message fields (2)

Unity practical tips (updating)

Simple understanding of network principle

随机推荐

数据库的索引和事务(重点)

Some experience of learning technology and theoretical knowledge

Solve binary tree (5)

The problem that tqdm cannot display in a single line

UnityShader-高斯模糊

Remote sensing image recognition - making data sets

机器人导航实现

Basic concepts of software testing

[Arduino] reborn Arduino monk (1)

shell script if嵌套for循环脚本

Calculation of Huffman tree, code implementation and proof, graphic interpretation

遥感影像识别-多类识别下的错分问题

文件内容的读写——数据流

力扣题解 二叉树(7)

Li Kou 236. the nearest common ancestor of binary tree

Wireshark function introduction

UnityShader-LowPoly

Communication mechanism cases

C#文件的读写

Acwing the number of square arrays of one question per day