当前位置:网站首页>#systemverilog# 可综合模型的结构总结

#systemverilog# 可综合模型的结构总结

2022-07-06 07:06:00 【那么菜】

一、可综合模型的结构

如果程序只用于仿真,那么几乎所有的语法和编程语句都可以使用。但如果程序是用于硬件实现,那么我们就必须保证程序的可综合性,即所编写的程序能被综合器 转化为相应的电路结构。不可综合的HDL语句在用综合工具综合时将被忽略或者报错。作为设计者,应该对可综合模型的结构有所了解。

虽然不同的综合工具对Verilog HDL语法结构的支持不尽相同,但Verilog HDL中某些典型的结构是很明确地被所有综合工具支持或不支持的。

(1)所有综合工具都支持的结 构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。

(2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。

(3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

因此,要编写出可综合的模型,应尽量采用所有综合工具都支持的结构来描述,这样才能保证设计的正确性和缩短设计周期。

二、建立可综合模型的原则

要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:

(1)不使用初始化语句。

(2)不使用带有延时的描述。

(3)不使用循环次数不确定的循环语句,如forever、while等。

(4)不使用用户自定义原语(UDP元件)。

(5)尽量使用同步方式设计电路。

(6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。

(7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。

(8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。

(9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。

(10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。

(11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。

(12)避免混合使用上升沿和下降沿触发的触发器。

(13)同一个变量的赋值不能受多个时钟控制,也不能受两种不同的时钟条件(或者不同的时钟沿)控制。

(14)避免在case语句的分支项中使用x值或z值。

三、阻塞与非阻塞

建议在时序逻辑建模时使用非阻塞式赋值。因为对于阻塞式赋值来说,赋值语句的顺序对最后的综合结果有着直接的影响,设计者稍不留意就会使综合结果与设计本 意大相径庭。而如果采用非阻塞式赋值,则可以不考虑赋值语句的排列顺序,只需将其连接关系描述清楚即可。如下面的模型:

always @ (posedge clkA) //Label AwA

… = DataOut; //读DataOut的值

always @ (posedge clkA) //Label AwB

DataOut <= …; //采用非阻塞式赋值

如果将上述模型改为阻塞式赋值“DataOut = …”,按照程序中的书写顺序模拟这些always语句,在clkA上升沿处,always语句AwA读取了DataOut的当前值,然后always语句 AwB再向DataOut赋新值。如果颠倒了这两条always语句的顺序(或仿真器选择重新排定这两条always语句的执行顺序),那么先执行 always语句AwB,导致零时间内将新值赋给DataOut,随后always语句AwA读取的便是更新后的DataOut值。这看起来是由于 always语句都可以执行时,向DataOut的赋值是在零时间内发生并完成的。因此根据先执行哪一条always语句,AwA中读取的DataOut 值可能是其原值,也可能是其新值。

使用非阻塞赋值就可以消除这种仿真行为的依赖性,这时,读取DataOut发生在当前时刻,而在当前仿真周期结束时(即所有的变量读取都已完成)才将新值 赋给DataOut。这样上述模型的行为不再受always语句执行顺序的影响。因此,在某条always语句内对变量赋值而在该always语句外读取 变量,那么赋值语句应是非阻塞式赋值。

边栏推荐

- 中青看点阅读新闻

- What is the biggest problem that fresh e-commerce is difficult to do now

- Pallet management in SAP SD delivery process

- Librosa audio processing tutorial

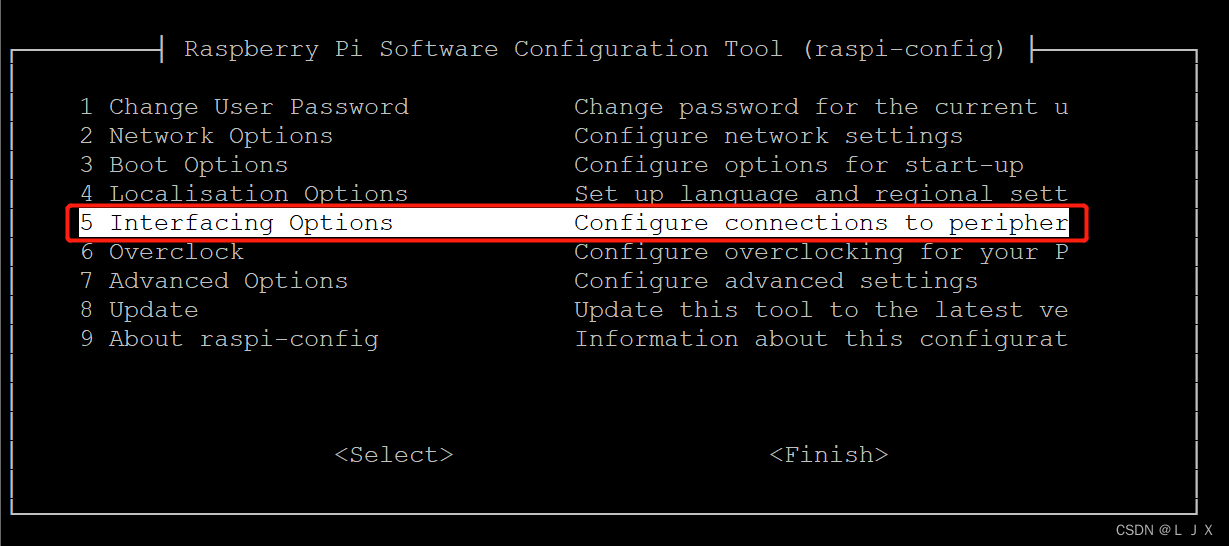

- Configure raspberry pie access network

- Win10 64 bit Mitsubishi PLC software appears oleaut32 DLL access denied

- MVVM of WPF

- Leetcode 78: subset

- [server data recovery] case of offline data recovery of two hard disks of IBM server RAID5

- Fast target recognition based on pytorch and fast RCNN

猜你喜欢

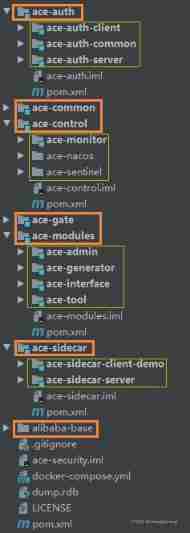

Establishment and operation of cloud platform open source project environment

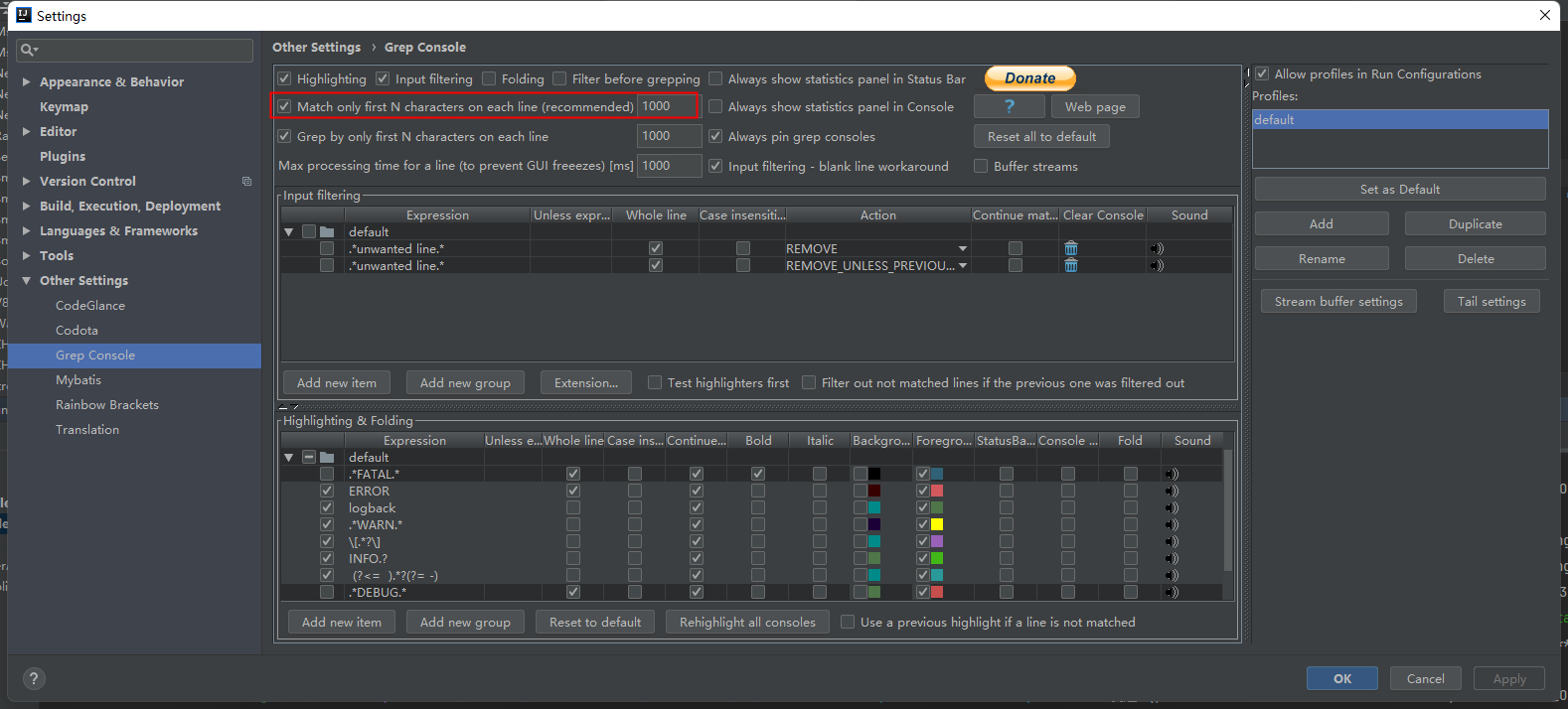

idea控制台彩色日志

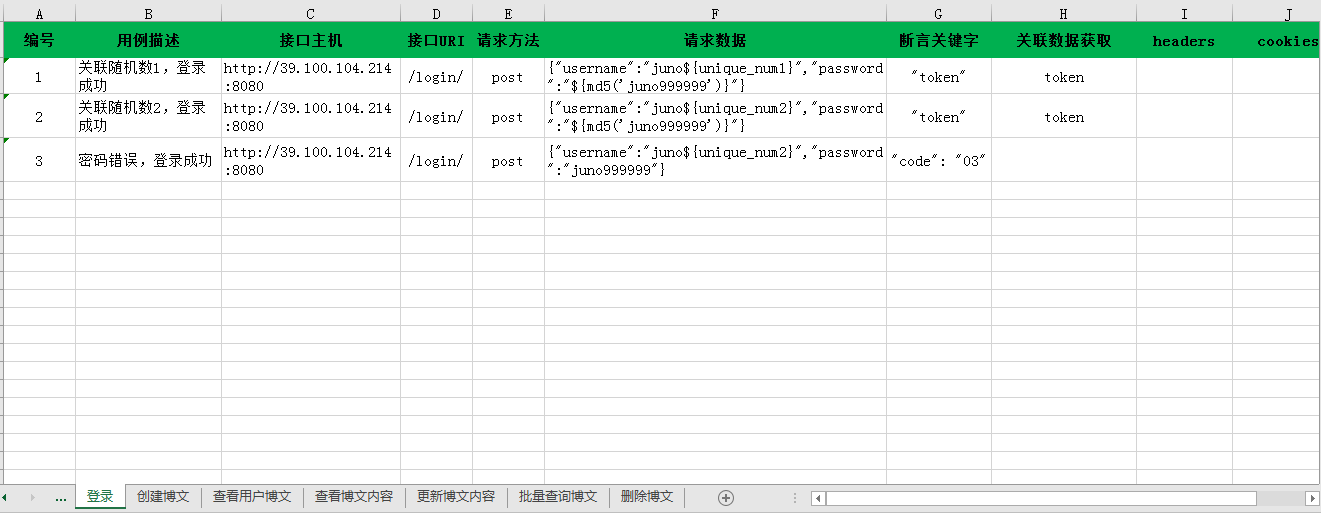

Interface automation test framework: pytest+allure+excel

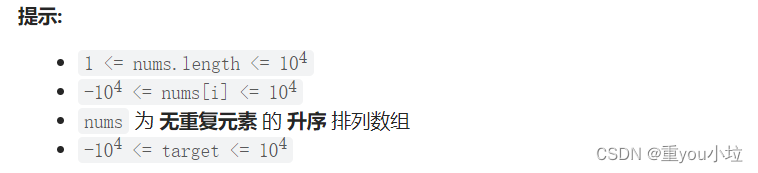

Leetcode35. search the insertion position (simple, find the insertion position, different writing methods)

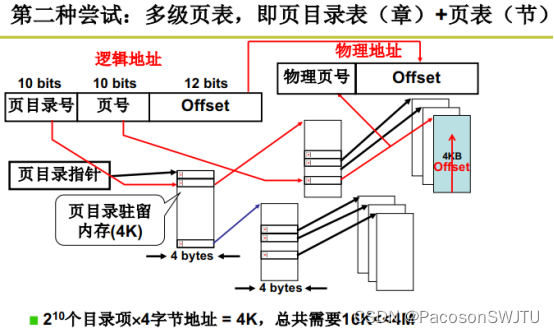

18. Multi level page table and fast table

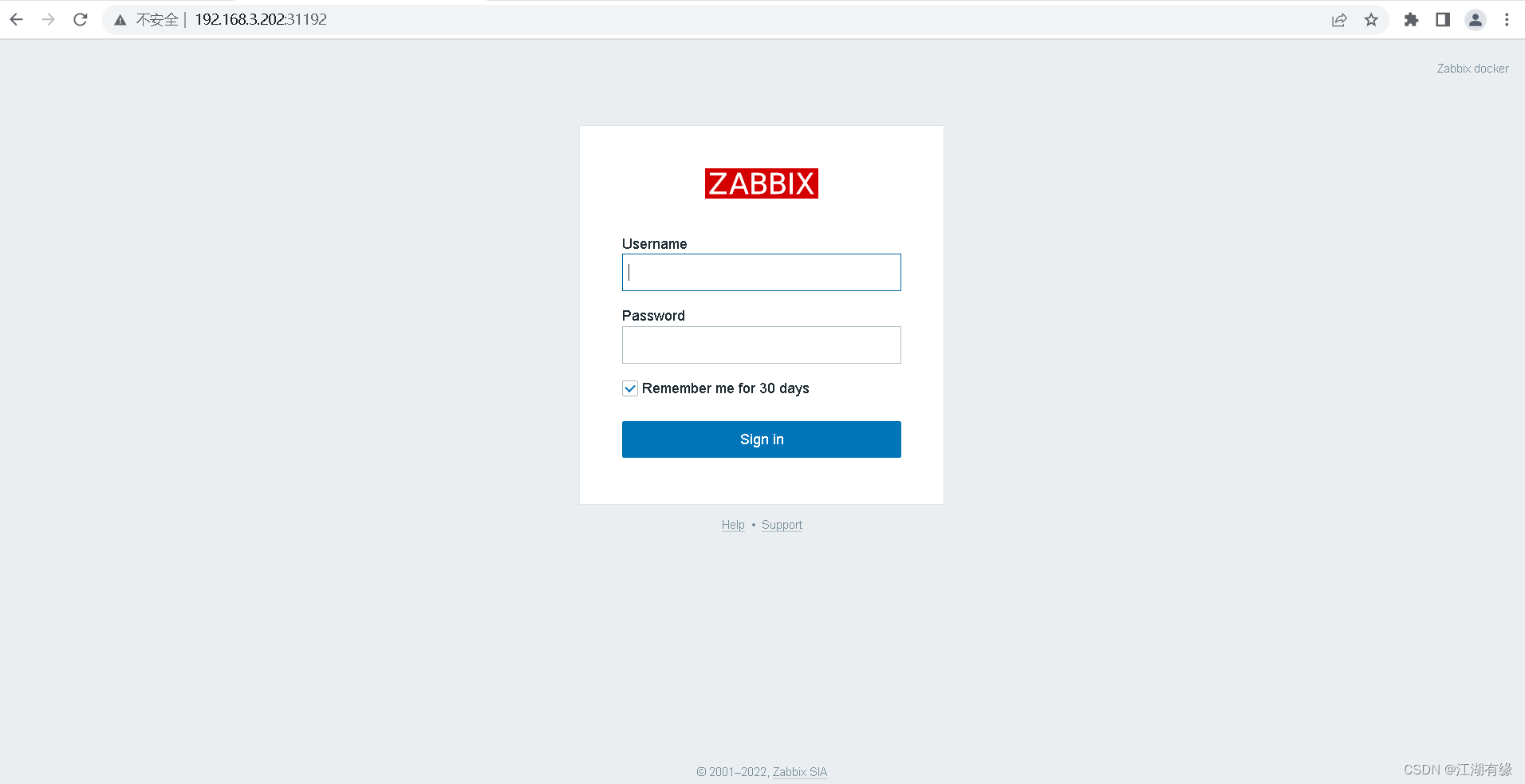

kubernetes集群搭建Zabbix监控平台

BUU的MISC(不定时更新)

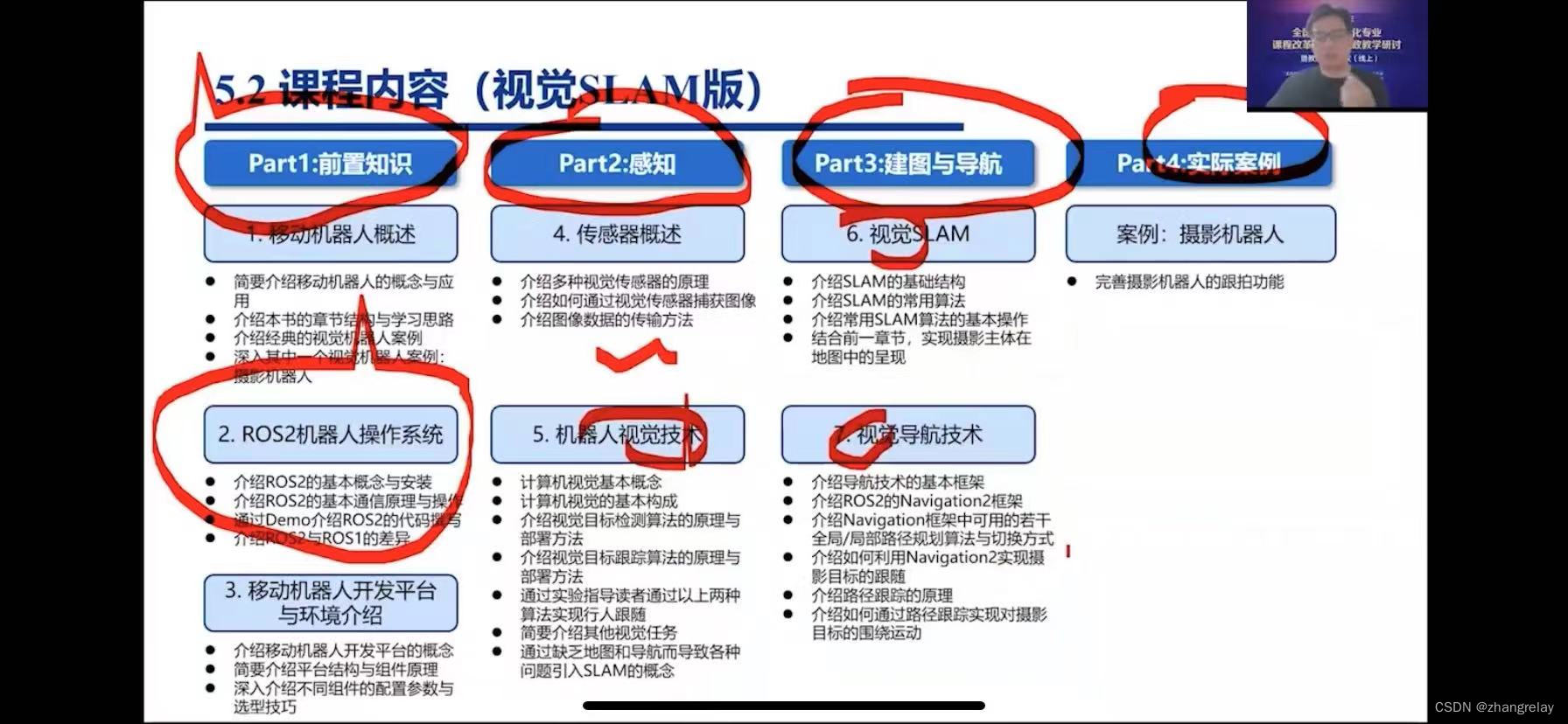

Brief introduction to the curriculum differences of colleges and universities at different levels of machine human major -ros1/ros2-

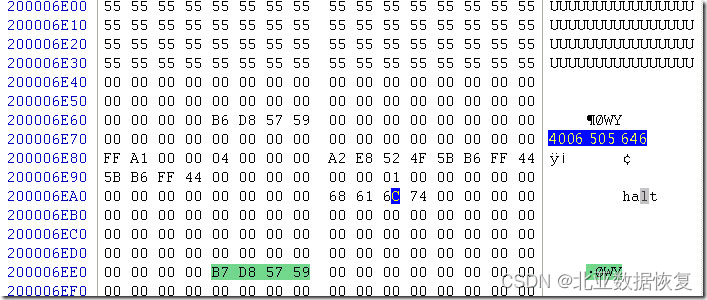

【服务器数据恢复】IBM服务器raid5两块硬盘离线数据恢复案例

Raspberry pie serial port login and SSH login methods

随机推荐

Leetcode59. spiral matrix II (medium)

What is the biggest problem that fresh e-commerce is difficult to do now

Setting and using richview trvstyle template style

The ECU of 21 Audi q5l 45tfsi brushes is upgraded to master special adjustment, and the horsepower is safely and stably increased to 305 horsepower

26岁从财务转行软件测试,4年沉淀我已经是25k的测开工程师...

AttributeError: Can‘t get attribute ‘SPPF‘ on <module ‘models.common‘ from ‘/home/yolov5/models/comm

[server data recovery] case of offline data recovery of two hard disks of IBM server RAID5

Proteus -- Serial Communication parity flag mode

Refer to how customer push e-commerce does content operation

A brief introduction of reverseme in misc in the world of attack and defense

The first Baidu push plug-in of dream weaving fully automatic collection Optimization SEO collection module

GET 和 POST 请求类型的区别

leetcode704. Binary search (find an element, simple, different writing)

Win10 64 bit Mitsubishi PLC software appears oleaut32 DLL access denied

NFT on fingertips | evaluate ambire on G2, and have the opportunity to obtain limited edition collections

Cif10 actual combat (resnet18)

开源的网易云音乐API项目都是怎么实现的?

作者已死?AI正用藝術征服人類

树莓派3B更新vim

Reflex WMS medium level series 3: display shipped replaceable groups