当前位置:网站首页>Verilog daily question (simple implementation of VL30 RAM)

Verilog daily question (simple implementation of VL30 RAM)

2022-07-28 17:22:00 【Don't make any more errors】

Title Description :

Achieve one Depth is 256, The seat width is 4bit Dual port RAM, All data are initialized to 0000. There are two sets of ports , Used for reading data and writing data respectively , Read and write operations can be performed simultaneously . When reading data indication signal read_en Is valid , By reading the address signal read_addr Read the data in the corresponding position read_data, And the output ; When writing data indication signal write_en Is valid , By writing the address signal write_addr And write data write-data, Write the corresponding data to the corresponding position .

The signal interface diagram of the program is as follows :

`timescale 1ns/1ns

module ram_mod(

input clk,

input rst_n,

input write_en,

input [7:0]write_addr,

input [3:0]write_data,

input read_en,

input [7:0]read_addr, // Address width log2(256)-1 = 7.

output reg [3:0]read_data

);

// Write data , Depth is 256, Storable 2^8=256 Data , Declaration array array

reg [3:0] array [255:0];

integer i;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

for(i=0;i<=255;i=i+1)

array[i] = 0; // Set all zeros

end

else

array[write_addr] =(write_en)? write_data:array[write_addr];

// According to the energy signal write_en, To declare the input address and data ( My understanding is to define a pointer )

end

// Read it ,

reg [3:0] data;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) read_data = 0; // Asynchronous zeroing

else read_data =(read_en)? array[read_addr]:read_data;

// The enable signal is 1 Read only when

end

endmodule// I'd like to review counting electricity when I'm free RAM Details of this part

边栏推荐

- Make full use of English

- The 16th program design competition of Dalian University of Technology (Problem Solver)

- Role of Fortress machine

- 火了 2 年的服务网格究竟给微服务带来了什么?(转载)

- Kubernetes service and ingress you need to master

- Goweb开发之Beego框架实战:第三节 程序执行流程分析

- Verilog 每日一题(VL29 单端口RAM)

- Classroom attendance system based on QT design (using RDS for MySQL cloud database)

- CNSA与CASC和CASIC的区别

- Pytorch Foundation: similarities and differences between torch.mul, torch.mm and torch.matmul

猜你喜欢

Atcoder regular contest 133 d.range XOR (digital dp+ classification discussion)

Unity shader screen post-processing

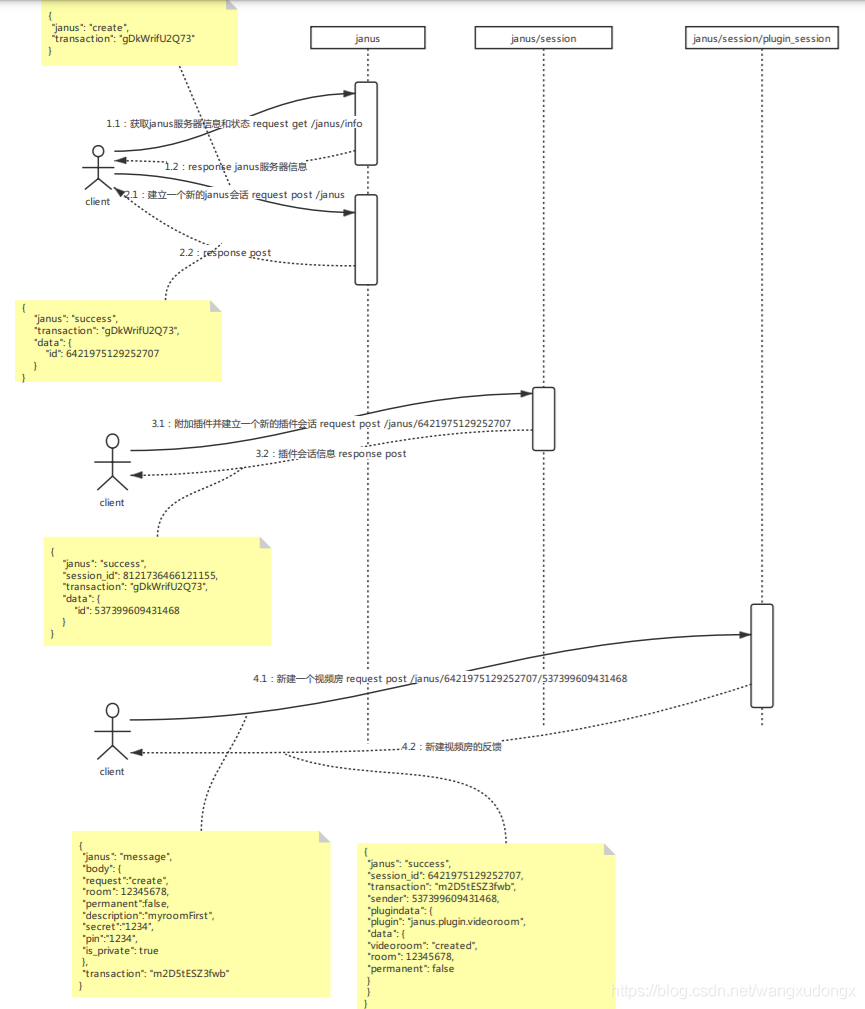

Janus series article 3 API usage guide videoroom creating a new video room

Verilog 每日一题 (VL30 RAM的简单实现)

Use of influxdb2

Goweb开发之Beego框架实战:第四节 数据库配置及连接

GEAR: Graph-based Evidence Aggregating and Reasoning for Fact Verification

Round 1A 2022 - Code jam 2022 c.weightlifting (interval DP)

QR code generation of wechat applet with parameters

Round 1C 2022 - Code jam 2022 b.square (Mathematics, thinking)

随机推荐

What does the service grid that has been popular for two years bring to microservices? (Reprinted)

部分情况下Error:(xx, xx) Failed to resolve: xxxxxx解决。

Unity shader uses rendered texture to achieve glass effect

Some attention code explanations

Educational codeforces round 126 (rated for Div. 2) f.teleporters (two sets and two points)

Codeforces round 770 (Div. 2) e. fair share

Leetcode 2022.04.10 China Merchants Bank special competition D. store promotion (DP)

带参数的微信小程序二维码生成

UNIQUE VISION Programming Contest 2022(AtCoder Beginner Contest 248)G. GCD cost on the tree

全链路灰度在数据库上我们是怎么做的?

Ugui learning notes (II) Scrollview related

微服务架构-服务注册中心和服务网关(6.8) (转载)

QR code generation of wechat applet with parameters

CNSA与CASC和CASIC的区别

一文了解 Kubernetes 中的服务发现

Jupyter notebook win installation record

Verilog daily question (vl29 single port RAM)

Vscode界面介绍

Goweb开发之Beego框架实战:第四节 数据库配置及连接

2022 Niuke multi school second CDE