当前位置:网站首页>verilog实现计算最大公约数和最小公倍数

verilog实现计算最大公约数和最小公倍数

2022-07-05 15:18:00 【不想上体育课】

设计一个时序电路,输入2个无符号数,位宽可以通过参数DATA_W确定,输出这两个数的最小公倍数和最大公约数。

解:在求解最大公约数与最小公倍数时,通常使用辗转相除法计算得到最大公约数,然后利用两数之积除最大公约数得到最小公倍数;

举例如下:

34 与 20;

(1)34 - 20 = 14;

(2)20 - 14 = 6;

(3)14 - 6 = 8;

(4)8 - 6 =2;

(5)6 - 2 = 4;

(6)4 - 2 = 2;

(7)2 - 2 = 0;

所以最大公约数为2;

则最小公倍数 = 34 * 20 /2 =340;

实现代码如下:

`timescale 1ns/1ns

module lcm#(

parameter DATA_W = 8)

(

input [DATA_W-1:0] A,

input [DATA_W-1:0] B,

input vld_in,

input rst_n,

input clk,

output wire [DATA_W*2-1:0] lcm_out,

output wire [DATA_W-1:0] mcd_out,

output reg vld_out

);

reg [DATA_W-1:0] A_reg;

reg [DATA_W-1:0] B_reg;

reg [DATA_W*2-1:0] lcm ;

reg [DATA_W*2-1:0] lcm_reg;

reg [DATA_W-1:0] mcd_reg;

reg [1:0] state;

parameter IDLE = 2'b00;

parameter st_1 = 2'b01;

parameter st_2 = 2'b10;

[email protected](posedge clk or negedge rst_n)

if(rst_n == 1'b0)

begin

vld_out<= 1'b0;

A_reg <= 'd0;

B_reg <= 'd0;

lcm <= 'd0;

mcd_reg <= 'd0;

lcm_reg <= 'd0;

state <= IDLE;

end

else case(state)

IDLE:

begin

vld_out <= 1'b0;

if(vld_in == 1'b1)

begin

A_reg <= A;

B_reg <= B;

lcm_reg<= A*B;

state <= st_1;

end

else

begin

A_reg <= A_reg;

B_reg <= B_reg;

lcm_reg<= lcm_reg;

state <= IDLE;

end

end

st_1:

if(A_reg == B_reg)

state <= st_2;

else

begin

state <= st_1;

if(A_reg > B_reg)

A_reg <= A_reg - B_reg;

else if(A_reg < B_reg)

B_reg <= B_reg - A_reg;

end

st_2:

begin

vld_out <= 1'b1;

lcm <= lcm_reg;

mcd_reg <= A_reg;

state <= IDLE;

end

endcase

assign lcm_out = lcm / mcd_reg;

assign mcd_out = mcd_reg;

endmodule仿真代码如下:

`timescale 1ns/1ns

module tb_lcm();

parameter DATA_W = 8;

reg [DATA_W-1:0] A;

reg [DATA_W-1:0] B;

reg vld_in;

reg rst_n;

reg clk;

wire [DATA_W*2-1:0] lcm_out;

wire [DATA_W-1:0] mcd_out;

wire vld_out;

initial

begin

A <= 'd0;

B <= 'd0;

vld_in <= 1'b0;

rst_n <= 1'b0;

clk = 1'b0;

#10

rst_n <= 1'b1;

A <= 'd6;

B <= 'd7;

vld_in <= 1'b1;

#2000

A <= 'd12;

B <= 'd8;

vld_in <= 1'b1;

#1000

A <= 'd15;

B <= 'd20;

vld_in <= 1'b1;

end

always #10 clk = ~clk;

lcm

#(

.DATA_W (DATA_W)

)

lcm_u

(

.A (A ),

.B (B ),

.vld_in (vld_in ),

.rst_n (rst_n ),

.clk (clk ),

.lcm_out (lcm_out),

.mcd_out (mcd_out),

.vld_out (vld_out)

);

endmodule波形如下:

边栏推荐

- Detailed explanation of C language branch statements

- Fundamentals of data communication - Principles of IP routing

- 超越PaLM!北大碩士提出DiVeRSe,全面刷新NLP推理排行榜

- MySQL 巨坑:update 更新慎用影响行数做判断!!!

- Explanation report of the explosion

- mapper. Comments in XML files

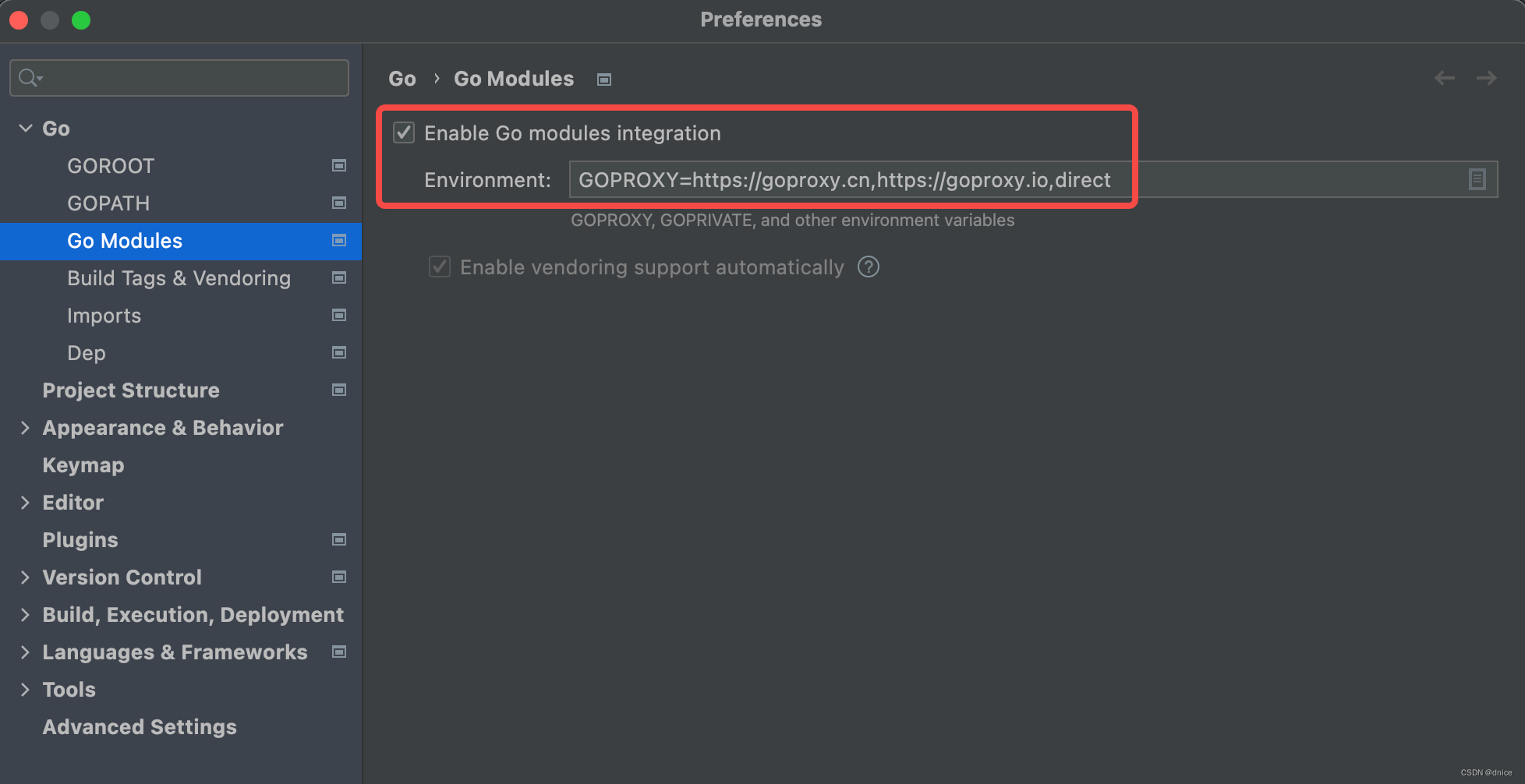

- 【 note 】 résoudre l'erreur de code IDE golang

- Install PHP extension spoole

- sql server学习笔记

- Creation and optimization of MySQL index

猜你喜欢

Detailed explanation of QT creator breakpoint debugger

Bugku easy_ nbt

Ctfshow web entry command execution

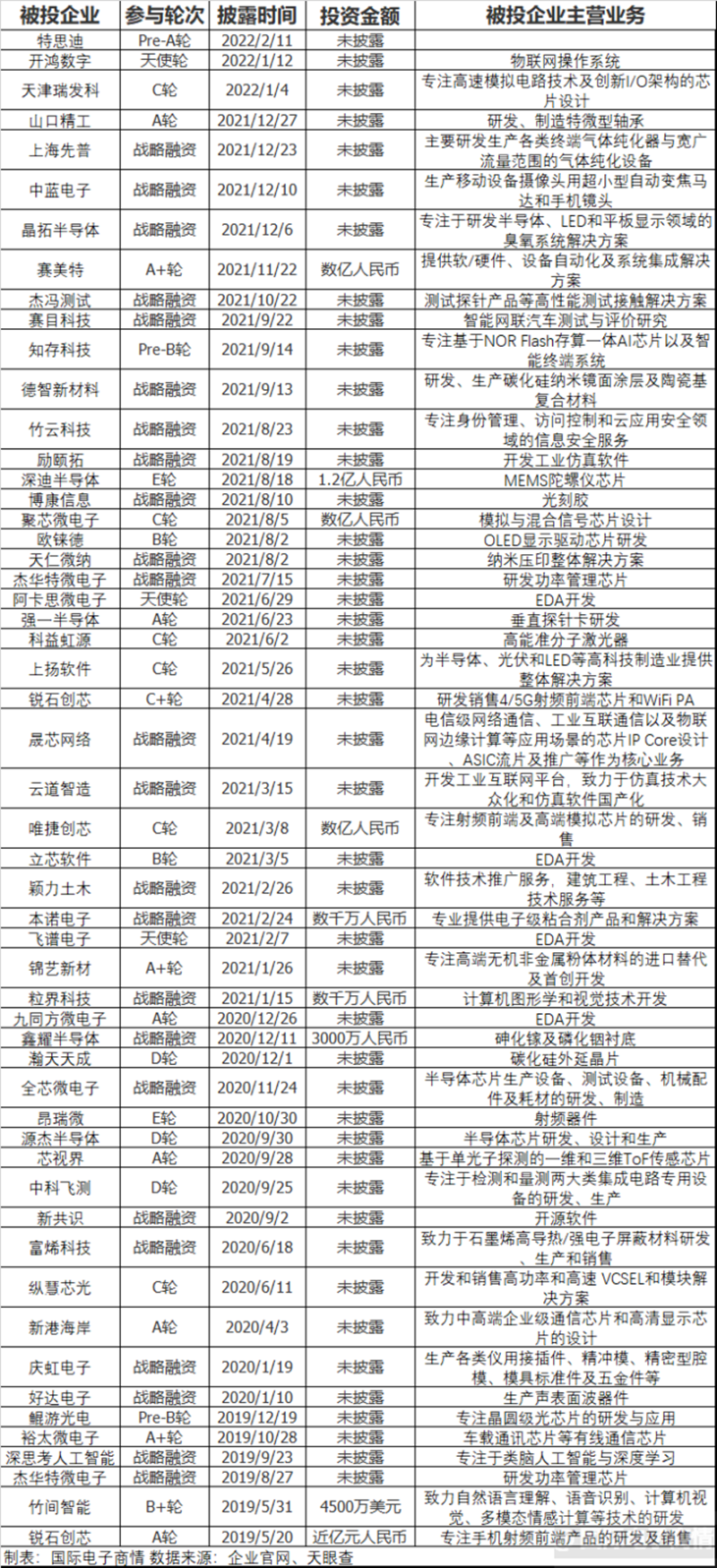

华为哈勃化身硬科技IPO收割机

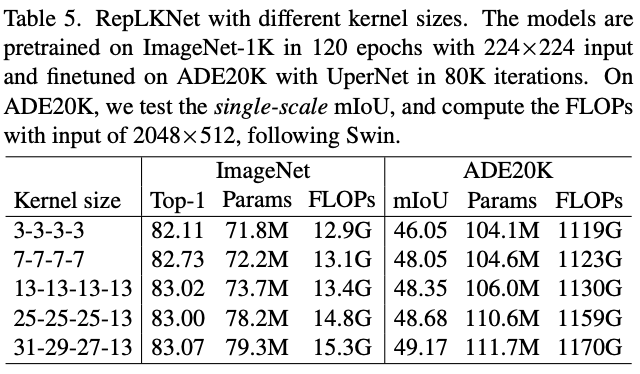

RepLKNet:不是大卷积不好,而是卷积不够大,31x31卷积了解一下 | CVPR 2022

Nine hours, nine people, nine doors problem solving Report

Bugku's Ah Da

swiper. JS to achieve barrage effect

【简记】解决IDE golang 代码飘红报错

wxml2canvas

随机推荐

Summary of the third class

Go learning ----- relevant knowledge of JWT

Calculate weight and comprehensive score by R entropy weight method

Reasons and solutions for redis cache penetration and cache avalanche

[brief notes] solve the problem of IDE golang code red and error reporting

Install PHP extension spoole

Thymeleaf uses background custom tool classes to process text

Garbage collection mechanism of PHP (theoretical questions of PHP interview)

Transfer the idea of "Zhongtai" to the code

keep-alive

The elimination strategy of redis

queryRunner. Query method

Noi / 1.5 06: element maximum span value of integer sequence

记录一下树莓派搭建环境中遇到的坑。。。

I spring web upload

Fundamentals of data communication - Principles of IP routing

sql server char nchar varchar和nvarchar的区别

你童年的快乐,都是被它承包了

Number protection AXB function! (essence)

Common redis data types and application scenarios