当前位置:网站首页>Hardware and software solution of FPGA key chattering elimination

Hardware and software solution of FPGA key chattering elimination

2022-07-05 08:01:00 【Drink more hot water-】

Catalog

RS trigger

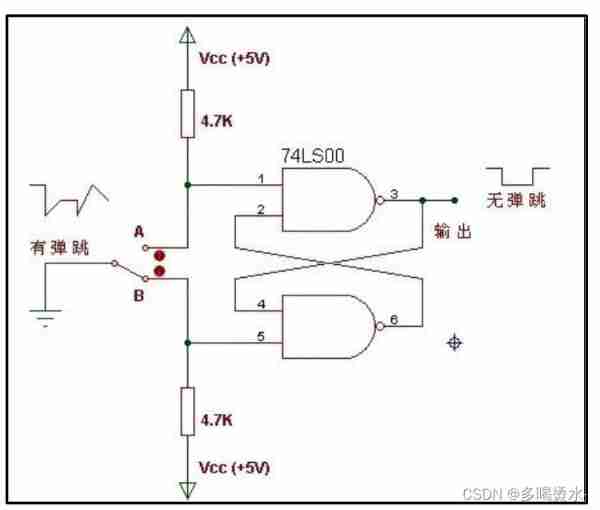

When the number of keys is small, hardware methods can be used to eliminate key jitter . Pictured Shown RS The trigger is used for common hardware to shake .

In the figure, two NAND gates form a RS trigger . When the key is not pressed , Output is 0;

When the key is pressed , Output is 1. At this time, the mechanical performance of the key is used , Make the key momentarily disconnected due to elastic jitter ( Jitter jump B), As long as the key does not return to the original state A, The state of the bistable circuit does not change , The output remains 0, Waveform without jitter . in other words , Even if B The voltage waveform of point is jittery , But after bistable circuit , Its output is normal rectangular wave . This point is analyzed RS The working process of the trigger can be easily verified

Software deblurring

If there are many keys , Commonly used software methods to shake , That is, execute a delay program after detecting that the key is closed , According to the shaking time 5ms~10ms, We produce a 20ms Time delay of , Let the leading edge jitter disappear and then check the state of the key again , If the closed state level is still maintained , Then confirm that there is a real key press .

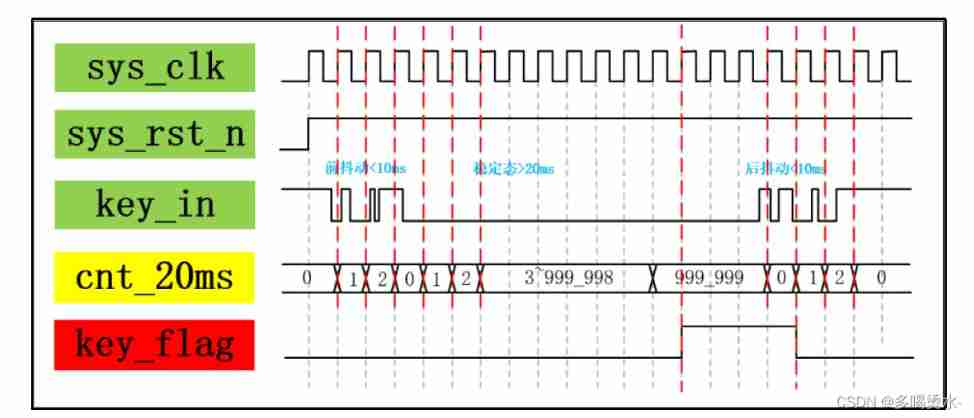

We add a name called cnt_20ms Used to count 20ms Time counter , Whenever the system detects that the key input signal is low cnt_20ms The counter starts counting , stay cnt_20ms During the counter counting period , If the key is detected to be high again, it means that the low level detected last time must be a jitter , Then we will clear this counter , This ensures the maximum delay 20ms Time will not be too short . Because we can't guarantee 20ms Applicable to every key press .

in addition , In order to avoid long level in the result of detecting keys , Instead of pulses, see the figure below

The fundamental reason is that cnt_20ms The counter counts to 999_999 Keep at 999_999 For too long . (999999 yes 20ms Of clk Count value )

And found out cnt_20ms The counter counts to 999_998 The number of times is only one , And closest 999_999, Make key_flag The signal only produces a pulse signal . The final waveform result is shown in the figure Shown .

Enclosed Verilog

module key

#(

parameter MAX_CNT = 20'd99_9999

)

(

input wire sys_clk,

input wire sys_rst_n,

input wire key_in, // Key in

output reg key_flag // Key value judgment bit

);

reg [19:0] clk_cnt_20ms; //20ms Of CLK The counter is stored here

// Clear every high level 0, The low level will increase itself

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clk_cnt_20ms <= 20'b0;

else if(key_in == 1'b1)

clk_cnt_20ms <= 20'b0;

else

clk_cnt_20ms <= clk_cnt_20ms + 1'b1;

// Low level 20ms after , The key is still low , It means that there is really a button pressed

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

key_flag <= 1'b0;

else if(clk_cnt_20ms == (MAX_CNT - 1'b1) && (key_in == 1'b0))

key_flag <= 1'b1;

else

key_flag <= 1'b0;

endmoduleThe method comes from brother fire , thank

边栏推荐

- OLED 0.96 inch test

- Detailed explanation of C language pointer

- Volatile of C language

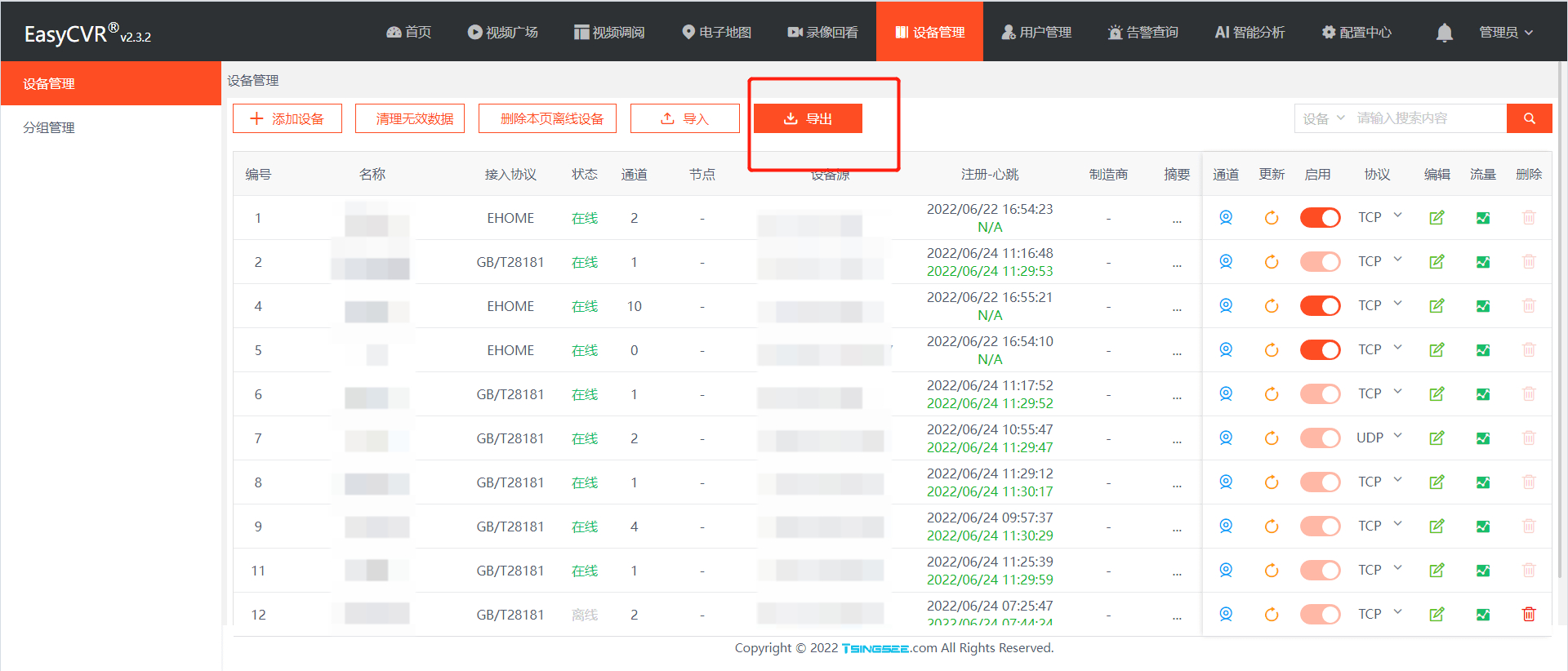

- 如何将EasyCVR平台RTSP接入的设备数据迁移到EasyNVR中?

- 1089 Insert or Merge 含测试点5

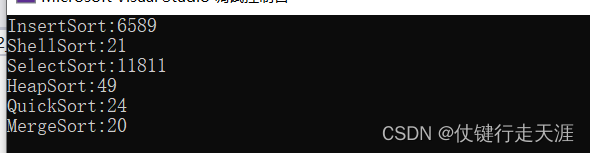

- 万字详解八大排序 必读(代码+动图演示)

- Train your dataset with yolov4

- Global and Chinese markets for waste treatment air switches 2022-2028: Research Report on technology, participants, trends, market size and share

- VESC Benjamin test motor parameters

- Global and Chinese markets for recycled boilers 2022-2028: Research Report on technology, participants, trends, market size and share

猜你喜欢

如何将EasyCVR平台RTSP接入的设备数据迁移到EasyNVR中?

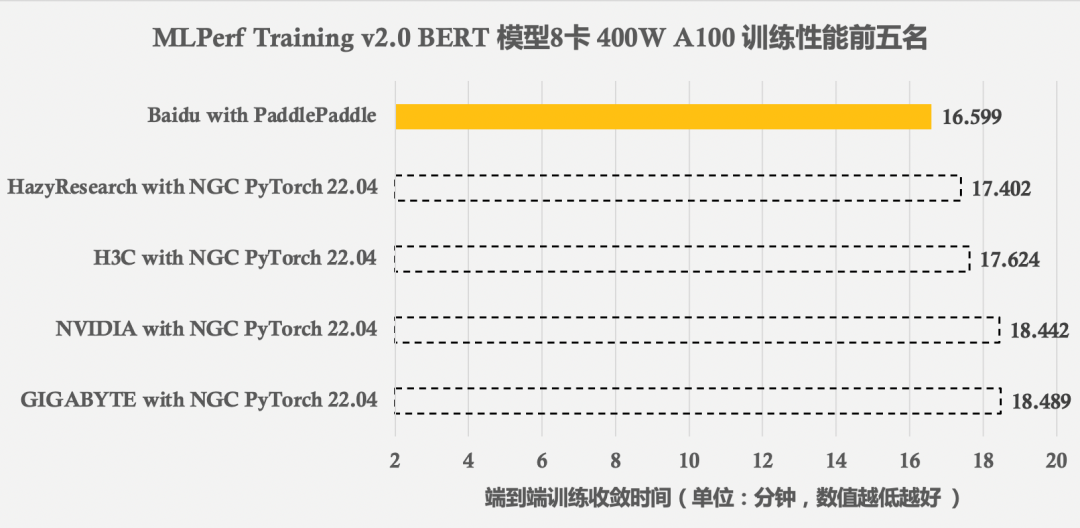

MLPerf Training v2.0 榜单发布,在同等GPU配置下百度飞桨性能世界第一

万字详解八大排序 必读(代码+动图演示)

![C WinForm [get file path -- traverse folder pictures] - practical exercise 6](/img/8b/1e470de4e4ecd4fd1bb8e5cf23f466.jpg)

C WinForm [get file path -- traverse folder pictures] - practical exercise 6

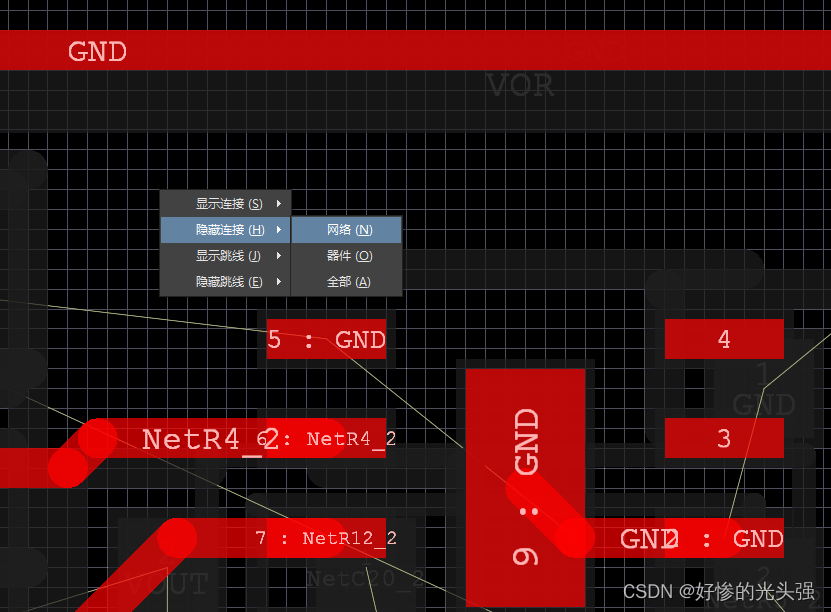

Altium Designer 19.1.18 - 隐藏某一个网络的飞线

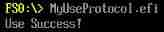

UEFI development learning 5 - simple use of protocol

Reasons for rapid wear of conductive slip rings

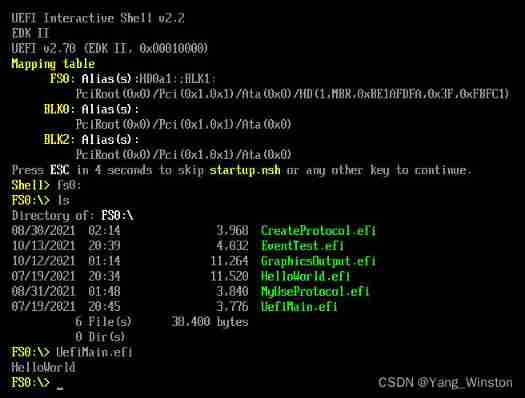

UEFI development learning 3 - create UEFI program

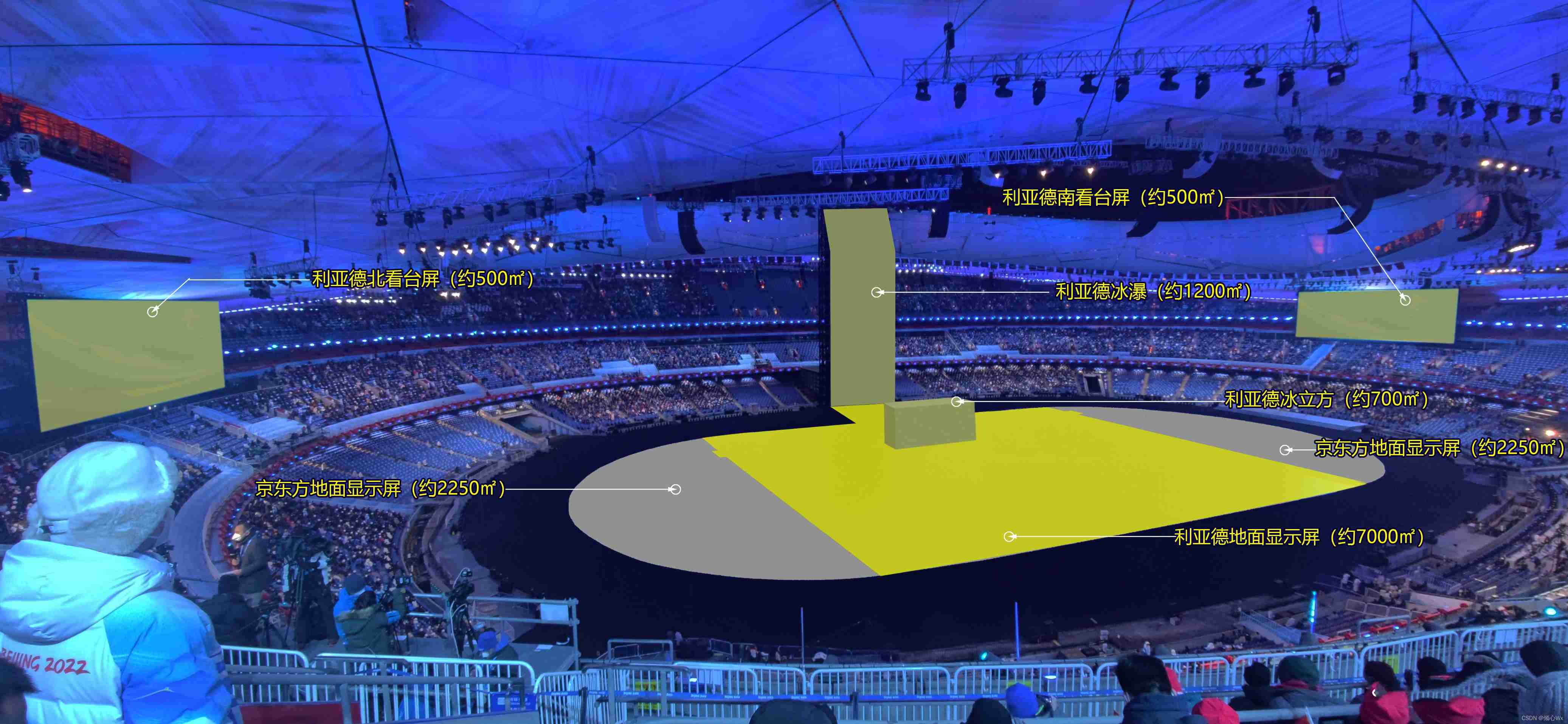

LED display equipment records of the opening ceremony of the Beijing Winter Olympics

Create inf module in AMI code

随机推荐

Global and Chinese market of plastic recycling machines 2022-2028: Research Report on technology, participants, trends, market size and share

Good websites need to be read carefully

Count and sort the occurrence times of specific fields through SQL statements

Reasons for rapid wear of conductive slip rings

Step motor generates S-curve upper computer

C WinForm [realize the previous and next selection pictures] - practice 7

C language uses arrays to realize the intersection, union, difference and complement of sets

Bootloader implementation of PIC MCU

Markdown tips

Gradle composite construction

mysql 盲注常见函数

Measurement fitting based on Halcon learning [i] fuse Hdev routine

[popular science] some interesting things that I don't know whether they are useful or not

Shape template matching based on Halcon learning [v] find_ cocoa_ packages_ max_ deformation. Hdev routine

[professional literacy] specific direction of analog integrated circuits

Some errors in configuring the environment

Train your dataset with yolov4

UEFI development learning 5 - simple use of protocol

How to excavate and research ideas from the paper

Create inf module in AMI code