当前位置:网站首页>[quick start of Digital IC Verification] 9. Finite state machine (FSM) necessary for Verilog RTL design

[quick start of Digital IC Verification] 9. Finite state machine (FSM) necessary for Verilog RTL design

2022-07-05 20:09:00 【luoganttcc】

Reading guide : The author has the honor to be a pioneer in the field of electronic information in China “ University of electronic technology ” During postgraduate study , Touch the cutting edge Numbers IC Verification knowledge , I heard something like Huawei Hisilicon 、 Tsinghua purple light 、 MediaTek technology And other top IC related enterprises in the industry , Pairs of numbers IC Verify some knowledge accumulation and learning experience . Want to get started for help IC Verified friends , After one or two thoughts , This column is specially opened , In order to spend the shortest time , Take the least detours , Most learned IC Verify technical knowledge .

List of articles

One 、 The basic theory

State machine Shorthand for FSM( Finite State Machine), Also known as synchronous finite state machine , We usually call it state machine for short , Reason why “ Sync ” Because all state jumps in the state machine are carried out under the action of the clock , and “ Co., LTD. ” It means that the number of States is limited . State machines are divided into two categories according to the reasons that affect the output , namely Moore State machine and Mealy State machine , What they have in common is : The jump of state is only related to input . The difference is mainly in the output : If the final output is only related to the current state and has nothing to do with the input, it is called Moore State machine ; If the final output is related not only to the current state but also to the input, it is called Mealy State machine . State machine is a very important application in sequential logic circuit , It is often used in large and complex systems .

Two 、 Automatic beverage vending machine

2.1、 Problem description

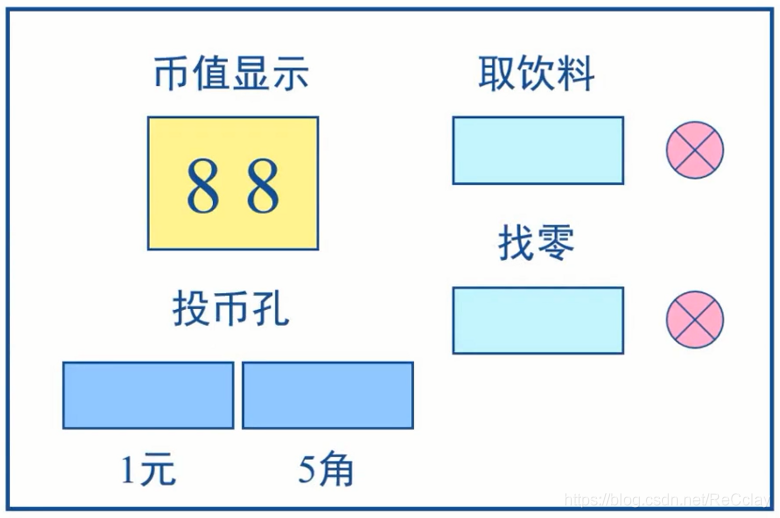

Design an automatic beverage machine , Set the price of drinks 2.5 element , You can use 5 Angular sum 1 Yuan coins , With change function .

notes : You can only cast at the same time 1 Yuan or 5 horn , You can't throw two at the same time .

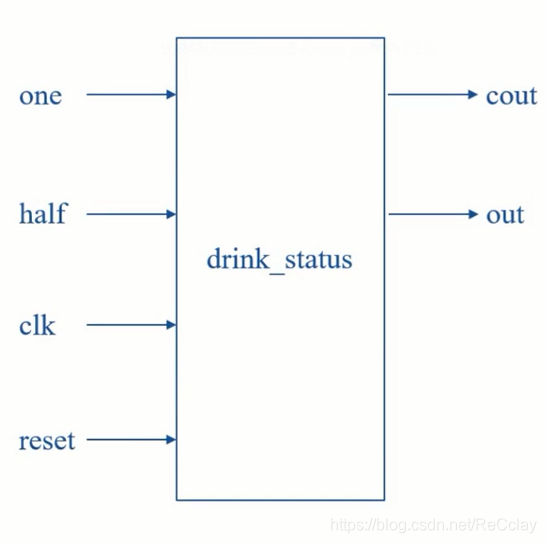

2.2、 Functional block diagram and interface definition

Interface signal definition

- clk: Clock input

- reset: System reset signal

- half: input 5 Dimes

- one: input 1 Yuan coins

- cout: Change signal

- out: The machine sells drinks

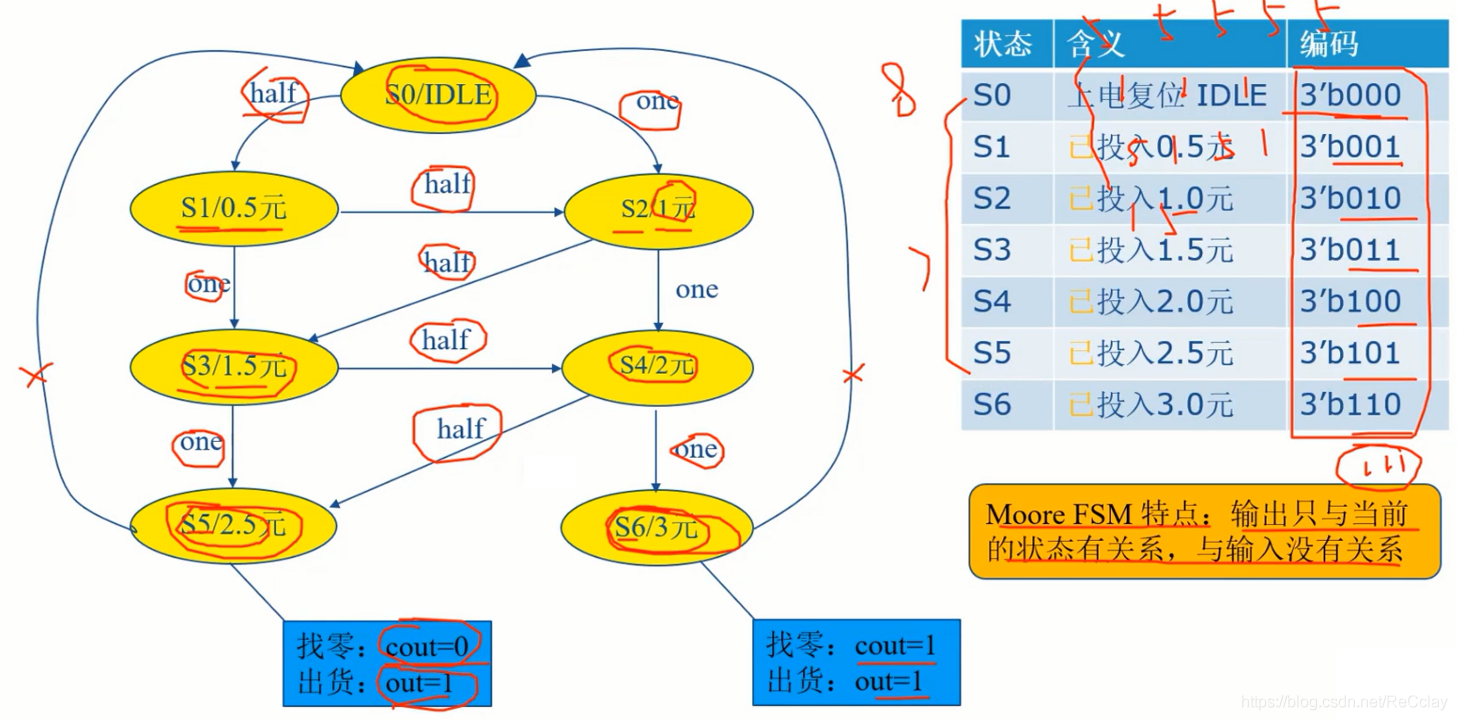

2.3、 State transition diagram - moore FSM

notes :Moore FSM characteristic : The output is only related to the current state , It has nothing to do with input !

Moore FSM Of RTL Code

module drink_status_moore(

input wire clk,

input wire reset,

input wire half,

input wire one,

output wire out,

output wire cout

);

parameter [2:0] S0 = 3'b000,

S1 = 3'b001,

S2 = 3'b010,

S3 = 3'b011,

S4 = 3'b100,

S5 = 3'b101,

S6 = 3'b110;

reg [2:0] curr_state;

reg [2:0] next_state;

//first segment:state transfer

[email protected](posedge clk or negedge reset)

if(!reset)

curr_state <= S0;

else

curr_state <= next_state;

//second segment:transfer condition

[email protected](*)

case(curr_state)

S0 : if(half == 1'b1) next_state = S1;

else if(one == 1'b1) next_state = S2;

else next_state = S0;

S1 : if(half == 1'b1) next_state = S2;

else if(one == 1'b1) next_state = S3;

else next_state = S1;

S2 : if(half == 1'b1) next_state = S3;

else if(one == 1'b1) next_state = S4;

else next_state = S2;

S3 : if(half == 1'b1) next_state = S4;

else if(one == 1'b1) next_state = S5;

else next_state = S3;

S4 : if(half == 1'b1) next_state = S5;

else if(one == 1'b1) next_state = S6;

else next_state = S4;

S5 : next_state = S0;

S6 : next_state = S0;

default : next_state = S0;

endcase

//third segment:state output

//moore type FSM

assign out = ((curr_state == S5) || (curr_state == S6) ) ? 1'b1 : 1'b0;

assign cout = (curr_state == S6) ? 1'b1 : 1'b0;

endmodule

FSM Three paragraph writing :

- Good coding style

- Logic synthesis

- Readable stars

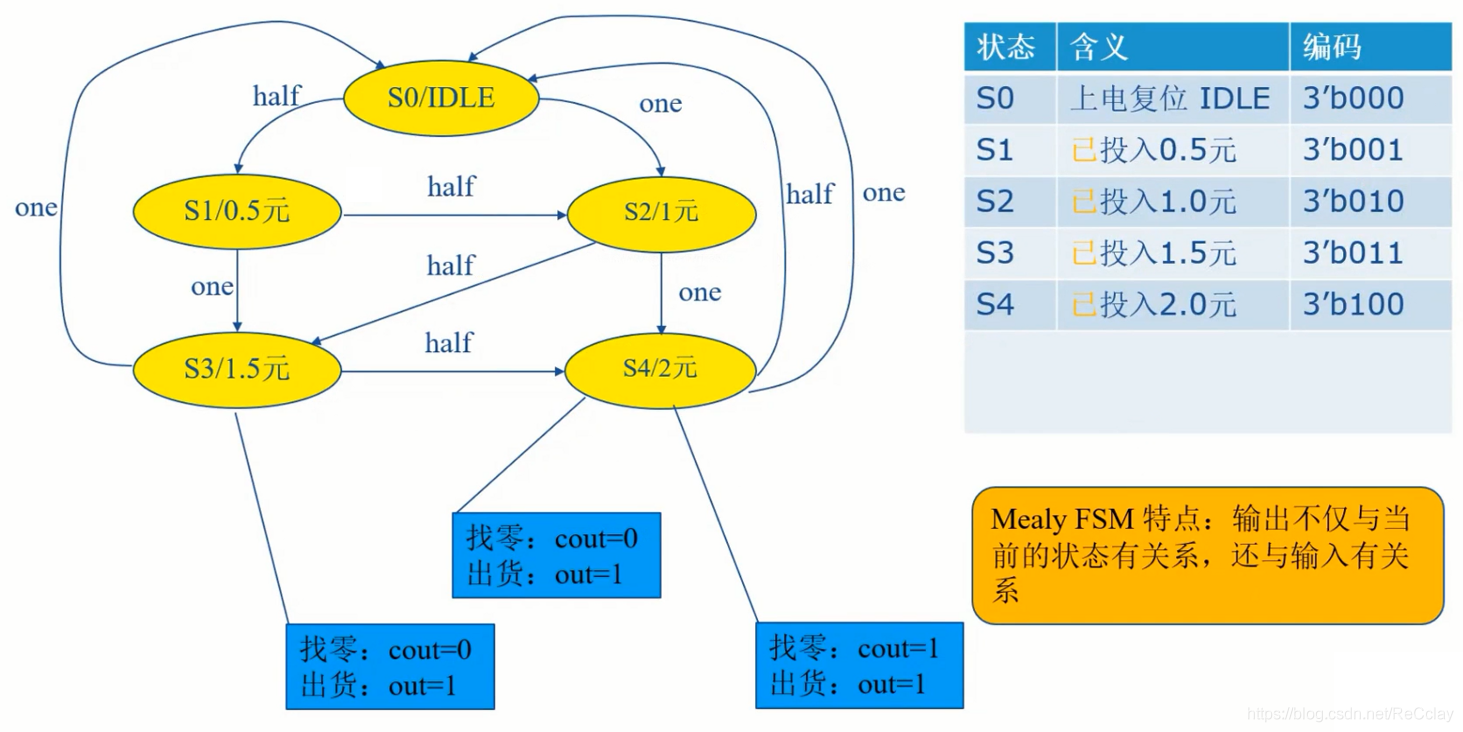

2.4、 State transition diagram - Mealy FSM

notes :Mealy FSM characteristic : The output is not only related to the current state , It is also related to input !

- Mealy It only took 5 States , But the output control will become complex !

Mealy FSM Of RTL Code

module drink_status_mealy(

input wire clk,

input wire reset,

input wire half,

input wire one,

output wire out,

output wire cout

);

parameter [2:0] S0 = 3'b000,

S1 = 3'b001,

S2 = 3'b010,

S3 = 3'b011,

S4 = 3'b100,

S5 = 3'b101,

S6 = 3'b110;

reg [2:0] curr_state;

reg [2:0] next_state;

//first segment:state transfer

[email protected](posedge clk or negedge reset)

if(!reset)

curr_state <= S0;

else

curr_state <= next_state;

//second segment:transfer condition

[email protected](*)

case(curr_state)

S0 : if(half == 1'b1) next_state = S1;

else if(one == 1'b1) next_state = S2;

else next_state = S0;

S1 : if(half == 1'b1) next_state = S2;

else if(one == 1'b1) next_state = S3;

else next_state = S1;

S2 : if(half == 1'b1) next_state = S3;

else if(one == 1'b1) next_state = S4;

else next_state = S2;

S3 : if(half == 1'b1) next_state = S4;

else if(one == 1'b1) next_state = S0;

else next_state = S3;

S4 : if(half == 1'b1) next_state = S0;

else if(one == 1'b1) next_state = S0;

else next_state = S4;

default : next_state = S0;

endcase

//third segment:state output

//mealy type FSM

assign out = ((curr_state == S3 && one == 1'b1) || (curr_state == S4 && (half==1'b1 || one==1'b1)) ) ? 1'b1 : 1'b0;

assign cout = (curr_state == S4 && one == 1'b1) ? 1'b1 : 1'b0;

endmodule

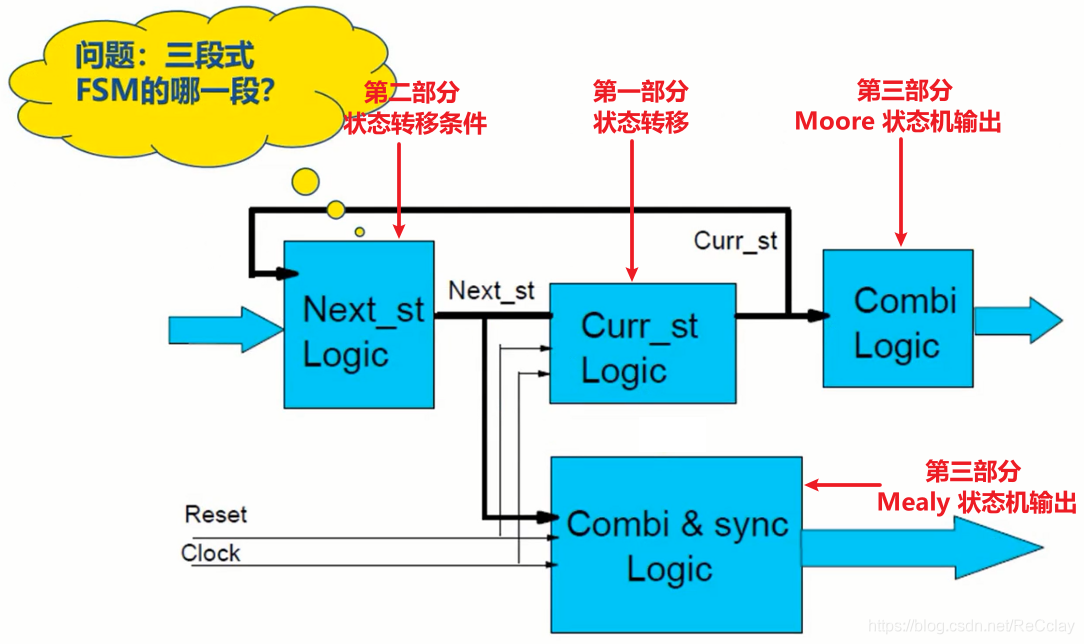

2.5、 Finite state machine circuit logic diagram

2.6、 Finite state machine summary

- FSM Design steps of finite state machine

- Interface definition

- State definition and coding

- Transition diagram of state

- According to the three segment coding style RTL Code

- To write TestBench Code

- Use Questasim Compile and simulate

- Check the input excitation through the waveform tool 、 Status signal and output signal

Frequently asked questions : Finite state machine classification ?

- answer :Moore State machine : The output of the state machine is only related to the current state

- Mealy State machine : The output of the state machine is not only related to the current state , Also related to the current input

Frequently asked questions : The difference between the two state machines ?

- answer :1、Moore State machine : After a finite gate delay of the clock pulse , The output is stable . The output will remain stable for a complete clock cycle , Even if the input signal changes within this clock , The output signal will not change . transport The influence of input on output can only be reflected in the next clock cycle . Separate input and output , yes Moore Important features of state machines .

- 2、Melay State machine : Because the output is directly affected by the input , The input can change at any time of the clock cycle , This makes the output state ratio Moore The output state of the state arrives one cycle in advance . The noise of the input signal may appear on the output signal .

- 3、 For the same circuit , Use Moore State machine design may be better than using Mealy The state machine has more States .

The key to state machine writing , Write in three parts :

- 1、 The first part is responsible for : State jump

- 2、 The second part is responsible for : Jump conditions

- 3、 The third part is responsible for : The output signal

2.7、 Something to be aware of :full case

- Define the complete state , Even some states may not appear in the circuit

- The purpose is to avoid the occurrence of Combinational logic ring

- Combinational logic rings can lead to STA There's no way to analyze ,DFT There is no way to cover

- Asynchronous timing (timing The path cannot be constrained , There is no way to analyze ) The problem of

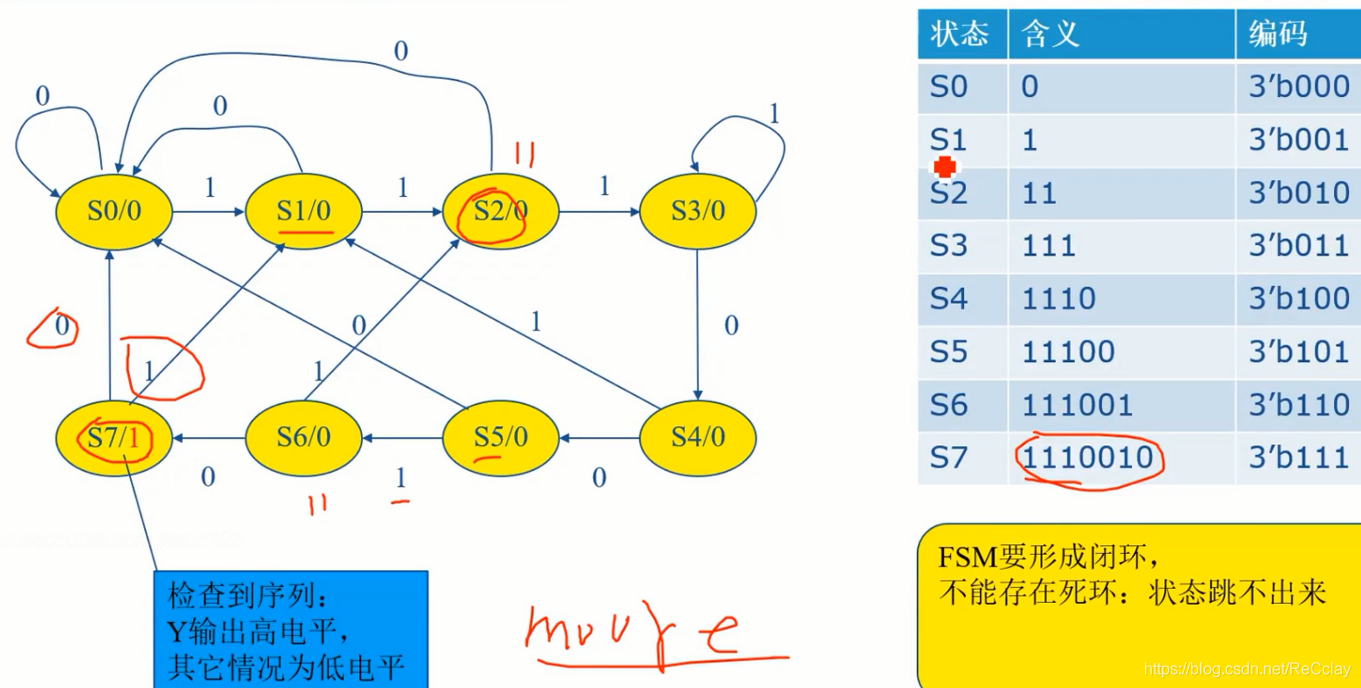

3、 ... and 、 Actual test : Sequence detector

3.1、 Functional requirements of sequence detector

- The design requirements

- Design sequence detector with state machine (1110010)

- Design function

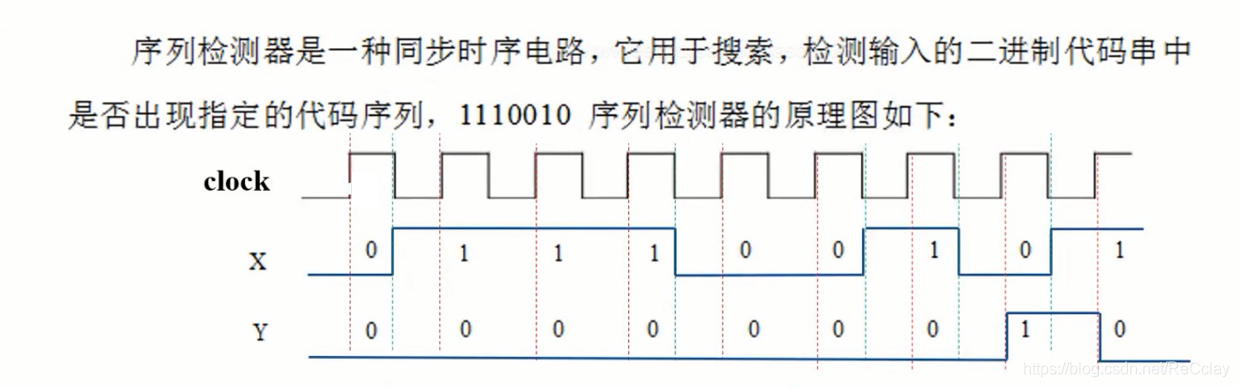

- Design a sequence detector , The sequence of detection is “1110010”

- When the input signal X In turn “1110010” when , The output signal Y Output a high level

- Otherwise, the output signal Y Low level

notes : Sequence detectors are often used in Engineering , be used for Detect sequence header !

3.2、 Timing diagram of timing detector

3.3、 State transition diagram of timing detector

Look for the , The output is independent of the input , This is a Moore State machine !

3.4、 Reference code of sequence detector

RTL Reference code

// 1110010

module seq(

input wire in,

input wire clk,

input wire reset,

output wire out

);

parameter [2:0] S0 = 3'b000,

S1 = 3'b001,

S2 = 3'b010,

S3 = 3'b011,

S4 = 3'b100,

S5 = 3'b101,

S6 = 3'b110,

S7 = 3'b111;

reg [2:0] cur_state;

reg [2:0] next_state;

//first step: state transfer

[email protected](posedge clk or negedge reset)

if(~reset)

cur_state <= S0;

else

cur_state <= next_state;

//second: transfer condition

[email protected](*)

case(cur_state)

S0:begin

if(in == 1) next_state = S1;

else next_state = S0;

end

S1:begin

if(in == 1) next_state = S2;

else next_state = S0;

end

S2:begin

if(in == 1) next_state = S3;

else next_state = S0;

end

S3:begin

if(in == 0) next_state = S4;

else next_state = S3;

end

S4:begin

if(in == 0) next_state = S5;

else next_state = S1;

end

S5:begin

if(in == 1) next_state = S6;

else next_state = S0;

end

S6:begin

if(in == 0) next_state = S7;

else next_state = S2;

end

S7:begin

if(in == 0) next_state = S0;

else next_state = S1;

end

default: next_state = S0;

endcase

//third: output

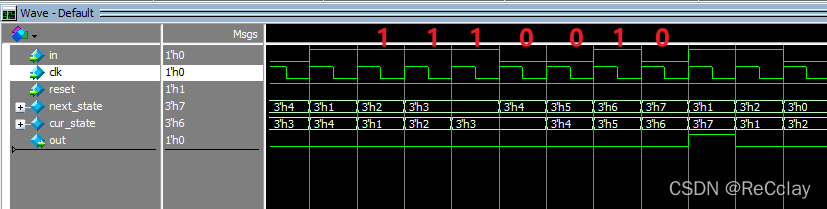

assign out = (cur_state == S7) ? 1'b1 : 1'b0;

endmodule

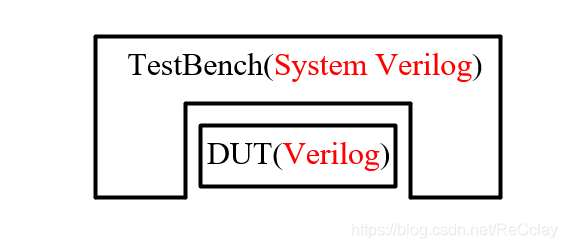

TestBench Reference code

`timescale 1ns/1ns

module tb_led();

//reg define

reg clk;

reg rst_n;

reg C;

//wire define

wire Y;

// // Initialize the system clock 、 Global reset

initial begin

clk = 1'b1;

rst_n <= 1'b0;

#10

rst_n <= 1'b1;

end

always #5 clk = ~clk;

[email protected](posedge clk or negedge rst_n)

if(rst_n == 1'b0)

C <= 1'b0;

else

C <= {$random} % 2;

seq seq_inst(

.clk (clk ),

.reset (rst_n ),

.in (C ),

.out (Y )

);

endmodule

The selected simulation results are as follows :

Reference resources

- 《 Wildfire journey Altera EP4CE10 - State machine 》

- Combinational logic ring (Combinational Loop)

- State machine , Start with the details ( One stage 、 Two-stage type 、 Three paragraph ,moore type 、mealy type )

边栏推荐

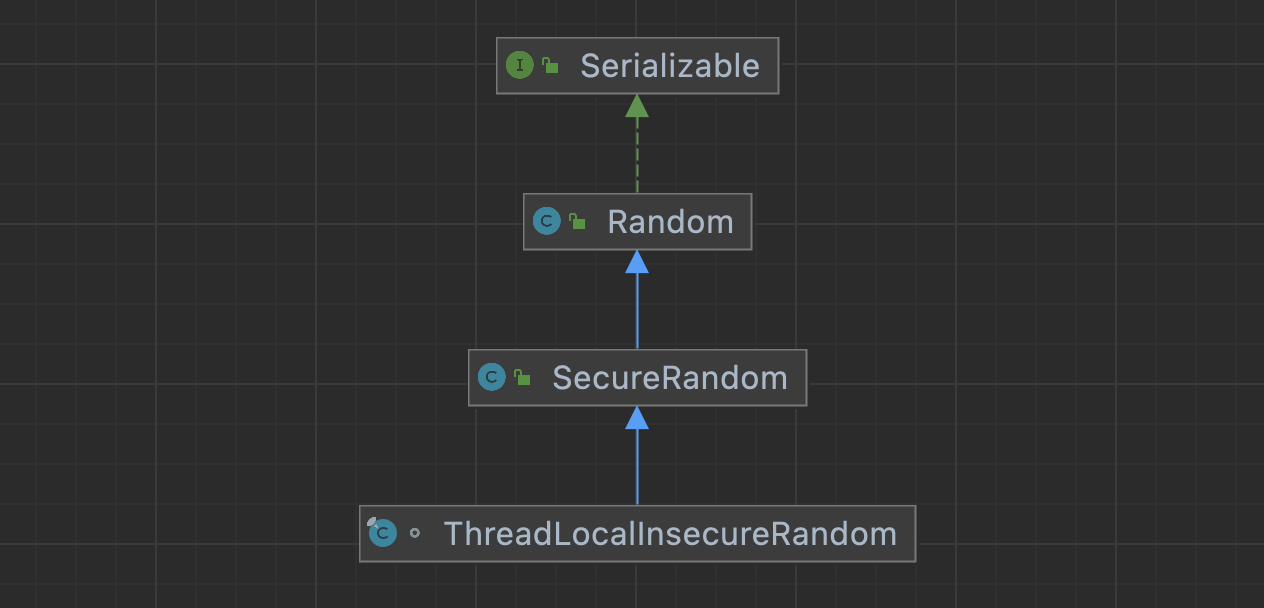

- Let's talk about threadlocalinsecurerandom

- 淺淺的談一下ThreadLocalInsecureRandom

- 《乔布斯传》英文原著重点词汇笔记(十二)【 chapter ten & eleven】

- Analysis of openh264 decoded data flow

- Is it safe for Guosen Securities to open an account online?

- Debezium series: modify the source code to support drop foreign key if exists FK

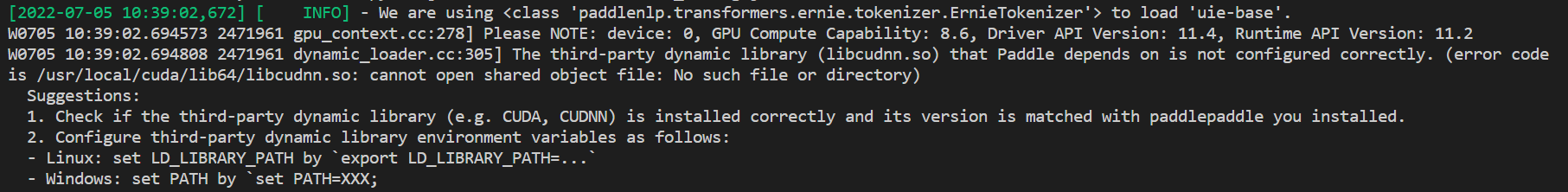

- third-party dynamic library (libcudnn.so) that Paddle depends on is not configured correctl

- 1:引文;

- leetcode刷题:二叉树12(二叉树的所有路径)

- Multi branch structure

猜你喜欢

【数字IC验证快速入门】1、浅谈数字IC验证,了解专栏内容,明确学习目标

Leetcode brush question: binary tree 13 (the same tree)

如何安全快速地从 Centos迁移到openEuler

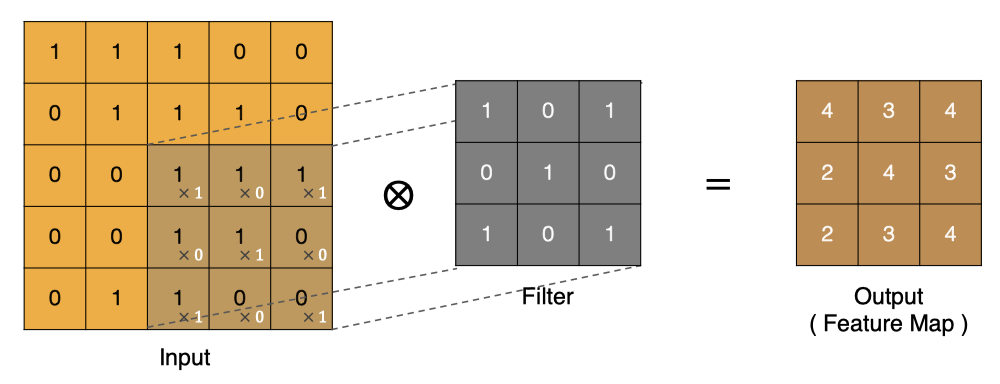

深度学习 卷积神经网络(CNN)基础

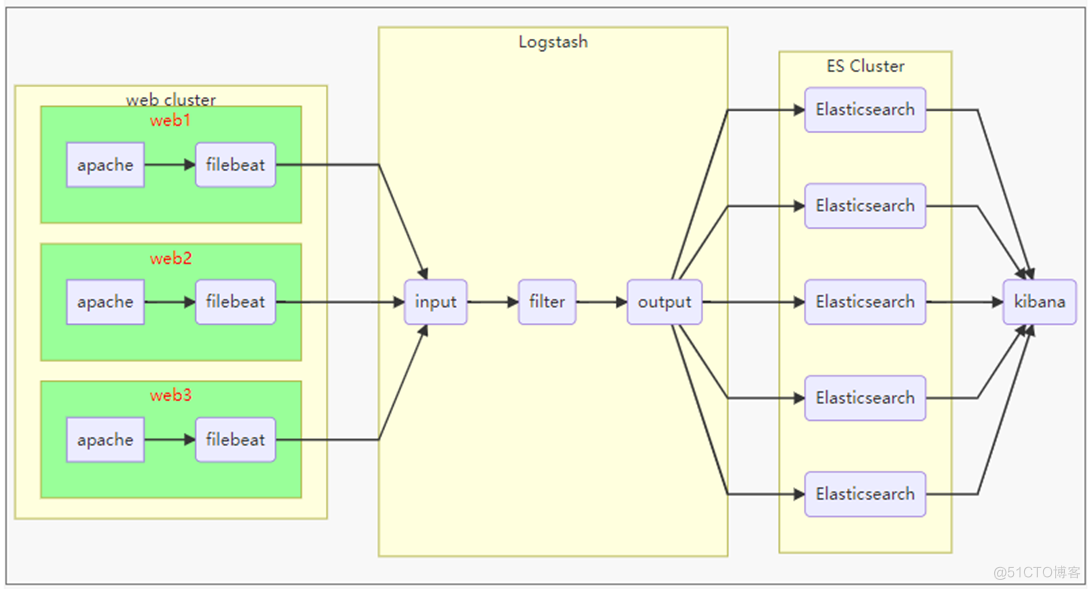

Elk distributed log analysis system deployment (Huawei cloud)

leetcode刷题:二叉树11(平衡二叉树)

third-party dynamic library (libcudnn.so) that Paddle depends on is not configured correctl

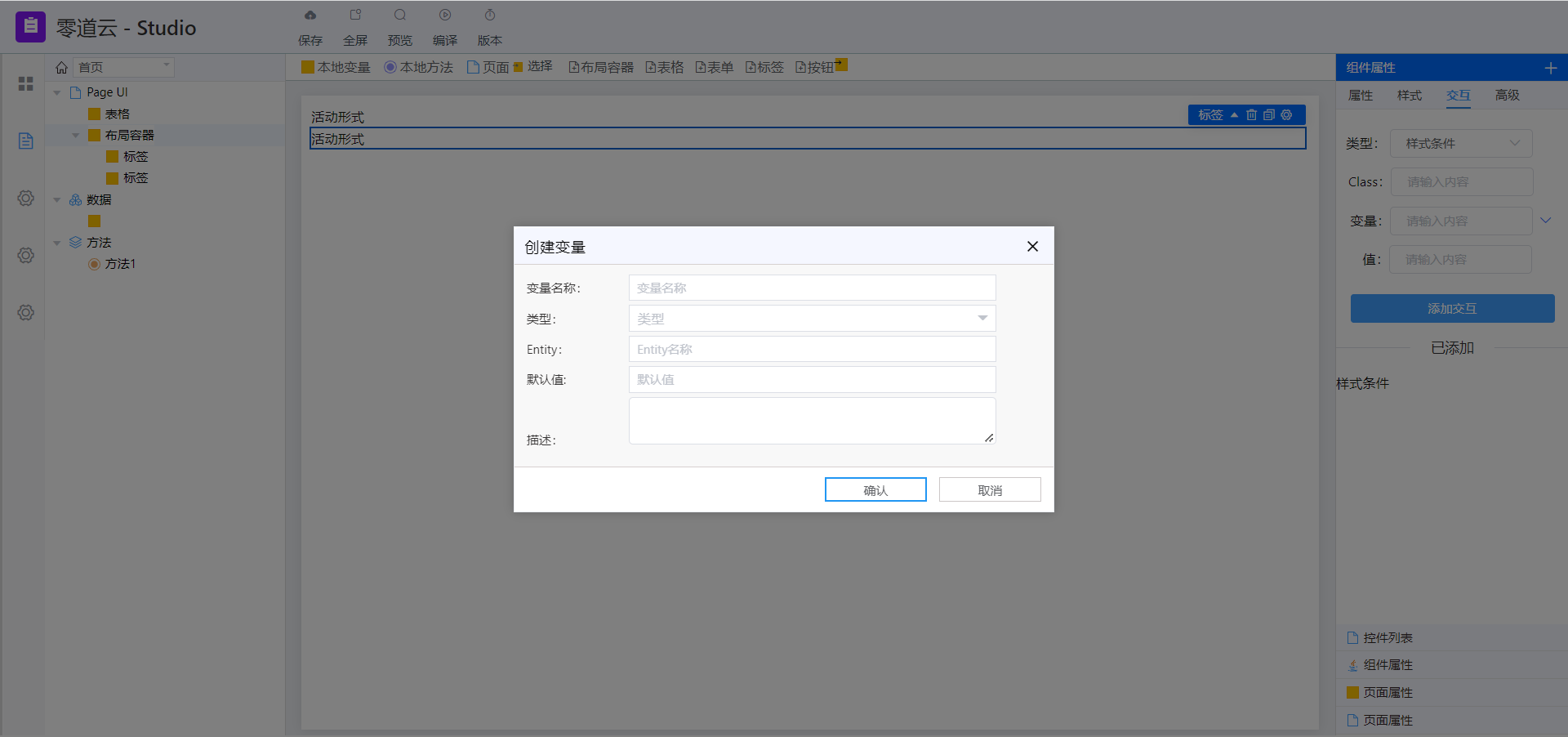

零道云新UI设计中

Wechat applet regular expression extraction link

浅浅的谈一下ThreadLocalInsecureRandom

随机推荐

银河证券在网上开户安全吗?

Guidelines for application of Shenzhen green and low carbon industry support plan in 2023

Unity编辑器扩展 UI控件篇

Parler de threadlocal insecurerandom

炒股开户最低佣金,低佣金开户去哪里手机上开户安全吗

Go language learning tutorial (XV)

Leetcode: binary tree 15 (find the value in the lower left corner of the tree)

函数的概念及语法

实操演示:产研团队如何高效构建需求工作流?

ffplay文档[通俗易懂]

Leetcode skimming: binary tree 16 (path sum)

.Net分布式事務及落地解决方案

通配符选择器

Common operators and operator priority

Complete interview questions for interviewers and senior Android engineers in front-line Internet enterprises

解决php无法将string转换为json的办法

Win10 x64环境下基于VS2017和cmake-gui配置使用zxing以及opencv,并实现data metrix码的简单检测

Leetcode brush question: binary tree 13 (the same tree)

Debezium series: parsing the default value character set

Is it safe to open a mobile stock account? Is it reliable?