当前位置:网站首页>Verilog and VHDL signed and unsigned number correlation operations

Verilog and VHDL signed and unsigned number correlation operations

2022-07-02 11:13:00 【Little by little progress】

Catalog

One 、Verilog Signed or unsigned number operation

3. Multiplication of signed numbers and signed numbers ( Input and output are original code )

Two 、VHDL In depth explanation of binary unsigned and signed addition processing overflow problem

One 、Verilog Signed or unsigned number operation

1. Addition and subtraction of signed numbers and signed numbers ( Input and output are original code )

step1: Convert data to Complement code .

step2: determine Output the result A wide .

( The bit width of the result is added to the bit width of the largest data . Such as 6bit And 3bit Add and subtract , The result is 7bit.)

step3: Extend the sign bit to the bit width of the output result , And then directly calculate .

step4: Process output .( Because the result is complement , It needs to be converted into the original code before output . Transformation method : Judge the sign bit , If the sign bit is 0, Indicates a positive number , Direct output ( Positive source code and complement are equal ). If the sign bit is 1, Indicates a negative number , The sign bit is required to remain unchanged , The significant bit is inverted plus one before output ( Complement to original ).)

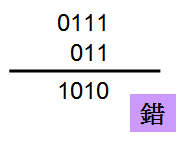

example 1:(-3) -(-6)

analysis :-3 Denote with a signed number , The original code is 3bit Of 111.-6 Denote with a signed number , The original code is 4bit Of 1110.

step1: Convert each number into a complement .-3 The complement of is 101,-6 The complement of is 1010

step2: Determine the bit width of the output result . The largest data bit width is 4bit, Then the bit width of the output result is 5bit Signed number of .

step3: Extend the sign bit to the bit width of the output result , And then directly calculate .

Output results out=1_1101-1_1010=0_0011( Note that the result should take 5bit)

step4: Sign bit out[5] = 0, Indicates a positive number , Direct output ,out=0_0011(+3)

example 2:(-3) - (+6)

analysis :-3 Denote with a signed number , The original code is 3bit Of 111.+6 Denote with a signed number , The original code is 4bit Of 0110.

step1: Convert to complement .-3 The complement of is 101,+6 The complement of is 0110.( The complement of a positive number is the same as the original code )

step2: Determine the bit width of the output result . The largest data bit width is 4bit, Then the bit width of the output result is 5bit Signed number of .

step3: Extend the sign bit to the bit width of the output result , And then directly calculate .

Output results out=1_1101-0_0110=1_0111( Note that the result should take 5bit)

step4: Sign bit out[5] = 1, Indicates a negative number , Then the sign bit remains unchanged , Valid is to add one to the inverse and output ,out=1_1001(-9)

2. The addition and subtraction of unsigned numbers and signed numbers ( Input and output are original code )

step1: Convert unsigned numbers to signed numbers .

step2: Convert data to Complement code .

step3: Determine the bit width of the output result .

( The bit width of the result is added to the bit width of the largest data . Such as 6bit And 3bit Add and subtract , The result is 7bit.)

step4: Extend the sign bit to the bit width of the output result , And then directly calculate .

step5: Process output .( Because the result is complement , It needs to be converted into the original code before output . Transformation method : Judge the sign bit , If the sign bit is 0, Indicates a positive number , Direct output ( Positive source code and complement are equal ). If the sign bit is 1, Indicates a negative number , The sign bit is required to remain unchanged , The significant bit is inverted plus one before output ( Complement to original ).)

example 3: (3) + (-6)

analysis :3 Use unsigned numbers to express , The original code is 2bit Of 11.-6 Denote with a signed number , The original code is 4bit Of 1110.

step1: Convert unsigned numbers to signed numbers .2bit The unsigned number of 11, Is a signed number 3bit Of 011

step2: Convert to complement .3 The complement of is 011,-6 The complement of is 1010.( The complement of a positive number is the same as the original code )

step3: Determine the bit width of the output result . The largest data bit width is 4bit, Then the bit width of the output result is 5bit Signed number of .

sep4: Extend the sign bit to the bit width of the output result , And then directly calculate .

Output results out=0_0011+1_1010=1_1101( Note that the result should take 5bit)

step5: Sign bit out[5] = 1, Indicates a negative number , Then the sign bit remains unchanged , Valid is to add one to the inverse and output ,out=1_0011(-3)

summary : The calculation of unsigned numbers and signed numbers can be transformed into the calculation of signed numbers and signed numbers .

3. Multiplication of signed numbers and signed numbers ( Input and output are original code )

step1: Determine the output result bit width .( A sign bit + The sum of the effective bit widths of the two data , Such as 1 individual 4bit Signed number of A, and 1 individual 5bit Signed number of B Multiply ,A The effective bit of is 3bit,B The significant bits of are 4bit, Then the effective bit width of the output result is 7bit, The total bit width is 8bit).

step2: Calculate the sign bit of the output result .( XOR the sign bits of two data , Judge whether it is positive or negative ).

step3: Calculate the significant bit of the output result .( Multiply the two data directly , The result obtained is the significant bit of the output result ).

step4: Concatenate sign bits and significant bits and output .

example 4:(-3)*(-6)

analysis :-3 Denote with a signed number , The original code is 3bit Of 111.-6 Denote with a signed number , The original code is 4bit Of 1110.

step1: Determine the output result bit width .(-3 The effective bit of is 2bit,-6 The significant bits of are 3bit, Then the effective bit width of the output result is 5bit, The total bit width is 6bit).

step2: Calculate the sign bit of the output result . The sign bits of both data are 1, be 1^1=0, Then the output result is a positive number .

step3: Calculate the significant bit of the output result .2'b11 * 3'b110 = 5'b1_0010.

step4: Concatenate sign bits and significant bits and output .out=6'b01_0010(+18)

ps: If the input is a complement , Then convert to the original code before operation , Just follow the above steps .

Two 、VHDL In depth explanation of binary unsigned and signed addition processing overflow problem

1.Unsigned adders

This is simpler , Just in A、B Expand one bit in front 0 Prevent overflow , Fill in the overflow number to n position cout,n-1 To 0 Bit is sum.

2.Signed adders

At first, I didn't understand why the symbol bit should be extended in the following figure , How to add two sign bits ? To look down ↓

2.1 Analysis

In the real beginning to use Verilog do signed Before addition , Let's first look at the actual binary singed How to add ?

Normal Condition ( No, Overflow)

(+6) + (-3) = (+3)

In order to save resource, We deliberately use 4 bit Of +6 And 3 bit Of -3 Add up , If you directly put two signed Value addition , The answer for -7, Obviously, the answer is not correct .

because 4 bit And 3 bit Add up , The result may be rounded to 5 bit, The correct way is to 4 bit Of +6 do signed extension To 5 bit, And 3 bit Of -3 Also do signed extension To 5 bit after , Then add , If the last carry to 6 bit, It doesn't take 6 bit Value .

What is meant by Singed Extension? To put it simply , When more bit Show signed Value of type , repeat signed bit A filling .

In a sense , Namely 3 bit Of signed If the value should be in 5 bit Presentation time , We must make up signed bit Can be in 5 bit Express , therefore 101 To become 11101.

Boundary Condition ( just Overflow)

(+7) + (+3) = (+10)

In order to save resource, We also deliberately use 4 bit Of +7 And 3 bit Of +3 Add up , If you directly put two signed Value addition , The answer for -6, Obviously, the answer is not correct .

According to the experience of the last example ,+7 And +3 Must do signed extension To add up , Only in this way can we get the correct answer +10.

But now the problem comes ,+10 Must move to 5 bit To display , If the output value range is 4 bit, Can only -8 ~ +7,+10 It's obviously already overflow 了 ‧

If only 4 bit Express , Because it's positive ,MSB Must be 0(SUM[3]=0), So if MSB yes 1 It means from carry , That is to say, positive overflow 了 ( In this case SUM[3] by 1, So it has been overflow), Plus, because the current calculation result is 5 bit, And it is positive , therefore SUM[5] It has to be for 0.

in other words , if SUM[5]=0 And SUM[4]=1 when , Being positive overflow, therefore 01010 about 4 bit Come on , Yes overflow.

Boundary Condition ( negative Overflow)

(-5) + (-4) = (-9)

Also in order to save resource, We deliberately use 4 bit Of -5 And 3 bit Of -4 Add up , If you directly put two signed Value addition , The answer for -1, Obviously, the answer is not correct .

According to the previous two examples ,-5 And -4 The same must be done signed extension To add up , Only in this way can we get the correct answer -9‧ Carry to 6 bit Of 1 Give up , So the answer is 10111‧

The same question comes ,-9 Must move to 5 bit To display , If the output value range is 4 bit, Can only -8 ~ +7,-9 It is obviously negative overflow 了 .

If only 4 bit Express , Because it's negative ,MSB Must be 1(SUM[3]=1), So if MSB yes 0 It means from carry , That is negative overflow 了 ( In this case SUM[3] by 0, So it has been negative overflow), Plus, because the current calculation result is 5 bit, And negative , therefore SUM[5] It has to be for 1‧

in other words , if SUM[5] by 1 And SUM[4] by 0 when , Negative overflow, therefore 10111 about 4 bit Come on , It's negative overflow.

2.2 Summary

According to the previous three practical examples , We come to the following conclusion :

m bit + m bit =< (m+1) bit m bit + n bit =< (m+1) bit, among n < m ul style='list-style:disc outside none;' > m bit And n bit Must be done first signed extension To (m+1) bit To add up If the result is (m+2) bit Ignore it , The actual result is (m+1) bit if Sum[m+1] ^ Sum[m] by 1, Express overflow if Sum[m+1] by 0 And Sum[m] by 1, It's positive overflow if Sum[m+1] by 1 And Sum[m] by 0, It's negative overflow

[1] How to realize signed unsigned addition and subtraction , How to deal with it overflowhttp://www.eeskill.com/article/id/4575

Reference link :verilog Related operations of signed and unsigned numbers in _ Haibinfeng's blog -CSDN Blog _verilog Signed and unsigned number operations

【VHDL】 In depth explanation of binary unsigned and signed addition processing overflow problem

边栏推荐

- Appgallery connect scenario development practice - image storage and sharing

- Hdu1228 a + B (map mapping)

- 从攻击面视角,看信创零信任方案实践

- TIPC介绍1

- STM32单片机编程学习

- 如何使用IDE自动签名调试鸿蒙应用

- How to transfer event objects and user-defined parameters simultaneously in Huawei express applications

- mmrotate旋转目标检测框架使用记录

- Resources读取2d纹理 转换为png格式

- TIPC Service and Topology Tracking4

猜你喜欢

二叉树专题--AcWing 1497. 树的遍历(利用后、中序遍历,构建二叉树)

2022 love analysis · panoramic report of digital manufacturers of state-owned enterprises

How to use ide to automatically sign and debug Hongmeng application

Flink two Open, implement Batch Lookup join (attached source)

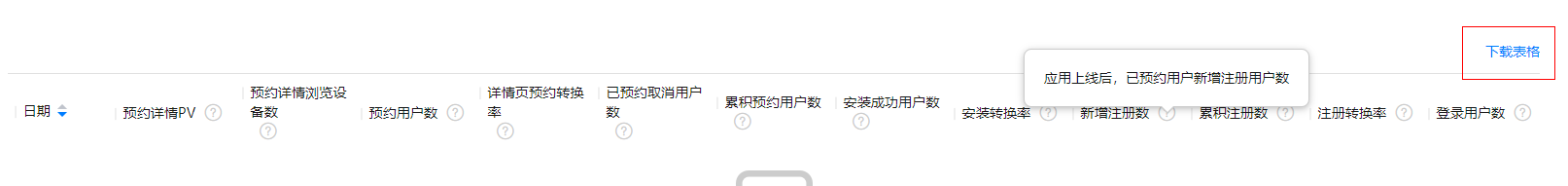

Uncover the secrets of Huawei application market application statistics

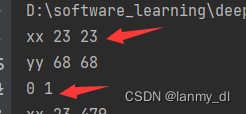

Pit of the start attribute of enumrate

JVM garbage collector

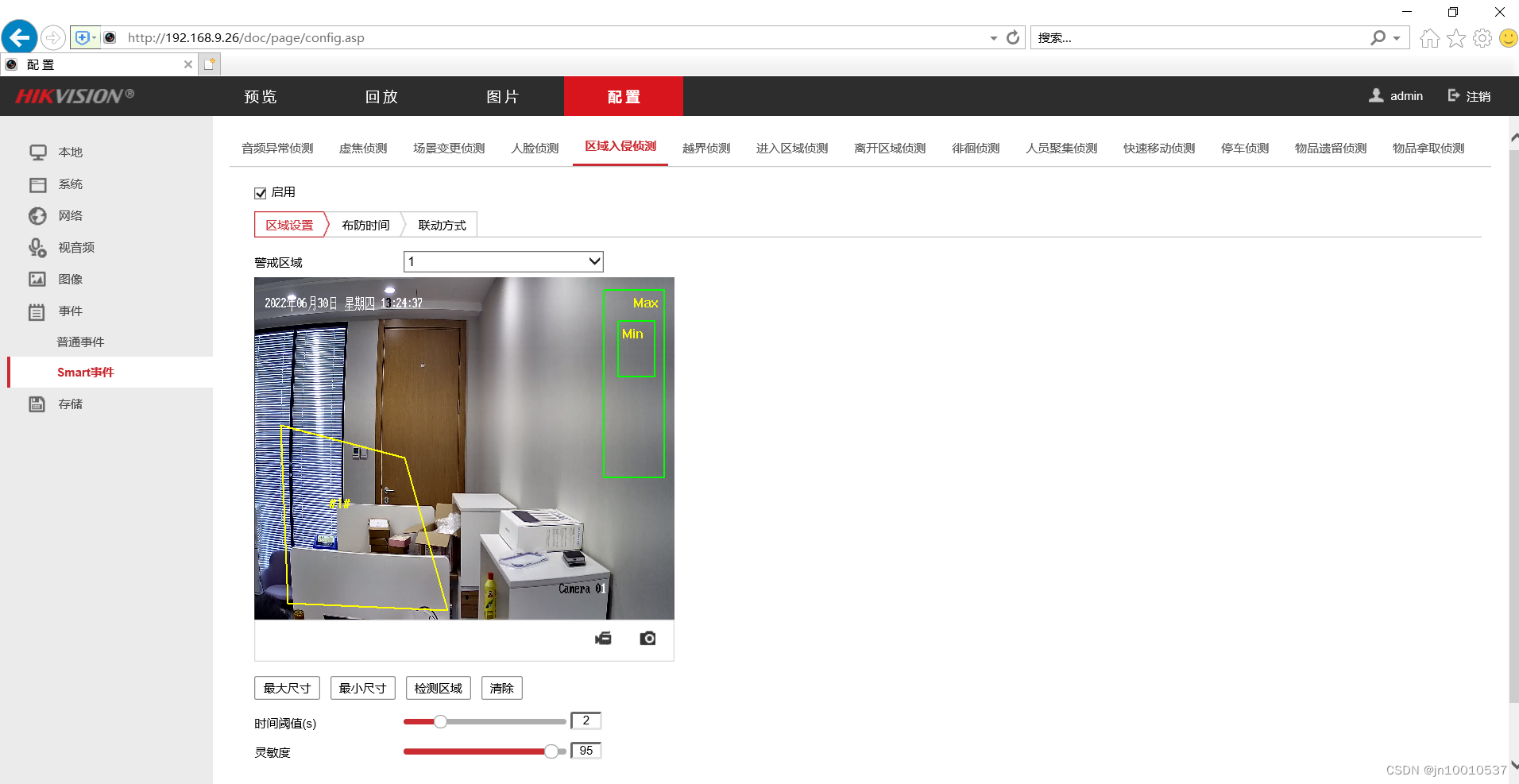

【AI应用】海康威视iVMS-4200软件安装

Tick Data and Resampling

V2x SIM dataset (Shanghai Jiaotong University & New York University)

随机推荐

Implementation of six singleton modes

Regular and common formulas

Special topic of binary tree -- acwing 3540 Binary search tree building (use the board to build a binary search tree and output the pre -, middle -, and post sequence traversal)

Leetcode 182 Find duplicate email (2022.07.01)

Uncover the secrets of Huawei application market application statistics

ImportError: cannot import name ‘Digraph‘ from ‘graphviz‘

flink二開,實現了個 batch lookup join(附源碼)

TIPC 寻址2

Matlab processing of distance measurement of experimental electron microscope

OpenMLDB Meetup No.4 会议纪要

TIPC介绍1

TIPC messaging3

Hdu1234 door opener and door closer (water question)

How to transfer event objects and user-defined parameters simultaneously in Huawei express applications

sql left join 主表限制条件写在on后面和写在where后面的区别

The working day of the month is calculated from the 1st day of each month

洛谷 P4281 [AHOI2008]紧急集合 / 聚会(树上倍增 LCA)

Special topic of binary tree -- acwing 1589 Building binary search tree

How to use ide to automatically sign and debug Hongmeng application

[quick application] there are many words in the text component. How to solve the problem that the div style next to it will be stretched