当前位置:网站首页>FPGA parsing B code----serial 4

FPGA parsing B code----serial 4

2022-08-05 06:56:00 【transparent light】

前言

Finished writing yesterday100The data is latched into the corresponding register,Below is the solutionB码的过程.

第一章:计算UTC时间

(*noprune*)reg [7:0] utc_sec;

(*noprune*)reg [7:0] utc_min;

(*noprune*)reg [7:0] utc_hou;

(*noprune*)reg [9:0] utc_day;

(*noprune*)reg [7:0] utc_yea;

[email protected](posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)begin

utc_sec <= 8'd0;

utc_min <= 8'd0;

utc_hou <= 8'd0;

utc_day <= 10'd0;

utc_yea <= 8'd0;

end

else if (bcodeflag == 1'b1)begin

if(b_data_rec3 >= 4'd1)utc_sec[0] <= 1'b0;

if(b_data_rec3 >= 4'd2)utc_sec[0] <= 1'b1;

if(b_data_rec4 >= 4'd1)utc_sec[1] <= 1'b0;

if(b_data_rec4 >= 4'd2)utc_sec[1] <= 1'b1;

if(b_data_rec5 >= 4'd1)utc_sec[2] <= 1'b0;

if(b_data_rec5 >= 4'd2)utc_sec[2] <= 1'b1;

if(b_data_rec6 >= 4'd1)utc_sec[3] <= 1'b0;

if(b_data_rec6 >= 4'd2)utc_sec[3] <= 1'b1;

if(b_data_rec8 >= 4'd1)utc_sec[4] <= 1'b0;

if(b_data_rec8 >= 4'd2)utc_sec[4] <= 1'b1;

if(b_data_rec9 >= 4'd1)utc_sec[5] <= 1'b0;

if(b_data_rec9 >= 4'd2)utc_sec[5] <= 1'b1;

if(b_data_rec10 >= 4'd1)utc_sec[6] <= 1'b0;

if(b_data_rec10 >= 4'd2)utc_sec[6] <= 1'b1;

if(b_data_rec12 >= 4'd1)utc_min[0] <= 1'b0;

if(b_data_rec12 >= 4'd2)utc_min[0] <= 1'b1;

if(b_data_rec13 >= 4'd1)utc_min[1] <= 1'b0;

if(b_data_rec13 >= 4'd2)utc_min[1] <= 1'b1;

if(b_data_rec14 >= 4'd1)utc_min[2] <= 1'b0;

if(b_data_rec14 >= 4'd2)utc_min[2] <= 1'b1;

if(b_data_rec15 >= 4'd1)utc_min[3] <= 1'b0;

if(b_data_rec15 >= 4'd2)utc_min[3] <= 1'b1;

if(b_data_rec17 >= 4'd1)utc_min[4] <= 1'b0;

if(b_data_rec17 >= 4'd2)utc_min[4] <= 1'b1;

if(b_data_rec18 >= 4'd1)utc_min[5] <= 1'b0;

if(b_data_rec18 >= 4'd2)utc_min[5] <= 1'b1;

if(b_data_rec19 >= 4'd1)utc_min[6] <= 1'b0;

if(b_data_rec19 >= 4'd2)utc_min[6] <= 1'b1;

if(b_data_rec20 >= 4'd1)utc_min[7] <= 1'b0;

if(b_data_rec20 >= 4'd2)utc_min[7] <= 1'b1;

if(b_data_rec22 >= 4'd1)utc_hou[0] <= 1'b0;

if(b_data_rec22 >= 4'd2)utc_hou[0] <= 1'b1;

if(b_data_rec23 >= 4'd1)utc_hou[1] <= 1'b0;

if(b_data_rec23 >= 4'd2)utc_hou[1] <= 1'b1;

if(b_data_rec24 >= 4'd1)utc_hou[2] <= 1'b0;

if(b_data_rec24 >= 4'd2)utc_hou[2] <= 1'b1;

if(b_data_rec25 >= 4'd1)utc_hou[3] <= 1'b0;

if(b_data_rec25 >= 4'd2)utc_hou[3] <= 1'b1;

if(b_data_rec27 >= 4'd1)utc_hou[4] <= 1'b0;

if(b_data_rec27 >= 4'd2)utc_hou[4] <= 1'b1;

if(b_data_rec28 >= 4'd1)utc_hou[5] <= 1'b0;

if(b_data_rec28 >= 4'd2)utc_hou[5] <= 1'b1;

if(b_data_rec29 >= 4'd1)utc_hou[6] <= 1'b0;

if(b_data_rec29 >= 4'd2)utc_hou[6] <= 1'b1;

if(b_data_rec30 >= 4'd1)utc_hou[7] <= 1'b0;

if(b_data_rec30 >= 4'd2)utc_hou[7] <= 1'b1;

if(b_data_rec32 >= 4'd1)utc_day[0] <= 1'b0;

if(b_data_rec32 >= 4'd2)utc_day[0] <= 1'b1;

if(b_data_rec33 >= 4'd1)utc_day[1] <= 1'b0;

if(b_data_rec33 >= 4'd2)utc_day[1] <= 1'b1;

if(b_data_rec34 >= 4'd1)utc_day[2] <= 1'b0;

if(b_data_rec34 >= 4'd2)utc_day[2] <= 1'b1;

if(b_data_rec35 >= 4'd1)utc_day[3] <= 1'b0;

if(b_data_rec35 >= 4'd2)utc_day[3] <= 1'b1;

if(b_data_rec37 >= 4'd1)utc_day[4] <= 1'b0;

if(b_data_rec37 >= 4'd2)utc_day[4] <= 1'b1;

if(b_data_rec38 >= 4'd1)utc_day[5] <= 1'b0;

if(b_data_rec38 >= 4'd2)utc_day[5] <= 1'b1;

if(b_data_rec39 >= 4'd1)utc_day[6] <= 1'b0;

if(b_data_rec39 >= 4'd2)utc_day[6] <= 1'b1;

if(b_data_rec40 >= 4'd1)utc_day[7] <= 1'b0;

if(b_data_rec40 >= 4'd2)utc_day[7] <= 1'b1;

if(b_data_rec42 >= 4'd1)utc_day[8] <= 1'b0;

if(b_data_rec42 >= 4'd2)utc_day[8] <= 1'b1;

if(b_data_rec43 >= 4'd1)utc_day[9] <= 1'b0;

if(b_data_rec43 >= 4'd2)utc_day[9] <= 1'b1;

if(b_data_rec52 >= 4'd1)utc_yea[0] <= 1'b0;

if(b_data_rec52 >= 4'd2)utc_yea[0] <= 1'b1;

if(b_data_rec53 >= 4'd1)utc_yea[1] <= 1'b0;

if(b_data_rec53 >= 4'd2)utc_yea[1] <= 1'b1;

if(b_data_rec54 >= 4'd1)utc_yea[2] <= 1'b0;

if(b_data_rec54 >= 4'd2)utc_yea[2] <= 1'b1;

if(b_data_rec55 >= 4'd1)utc_yea[3] <= 1'b0;

if(b_data_rec55 >= 4'd2)utc_yea[3] <= 1'b1;

if(b_data_rec57 >= 4'd1)utc_yea[4] <= 1'b0;

if(b_data_rec57 >= 4'd2)utc_yea[4] <= 1'b1;

if(b_data_rec58 >= 4'd1)utc_yea[5] <= 1'b0;

if(b_data_rec58 >= 4'd2)utc_yea[5] <= 1'b1;

if(b_data_rec59 >= 4'd1)utc_yea[6] <= 1'b0;

if(b_data_rec59 >= 4'd2)utc_yea[6] <= 1'b1;

if(b_data_rec60 >= 4'd1)utc_yea[7] <= 1'b0;

if(b_data_rec60 >= 4'd2)utc_yea[7] <= 1'b1;

end

endThe previously latched signal is 3,2,1和0信号,3代表P标志位,2代表高电平,1代表低电平.So first convert the value of the latch to 01信号,判断完毕后,进行计算.

注意:The pulse signal used here is bcodeflag,This signal is being collected101Calculated at points,And there is no time slot.因为BThe last digit of the code does not represent information,So this does not need to think too much about the issue of latching and not latching,所有的BThe codes are all front99个里面.

reg resettime3_en_d0;

reg resettime3_en_d1;

wire resettime3_falling_flag;

wire resettime3_rasing_flag;

assign resettime3_falling_flag = (~resettime3_en_d0) & resettime3_en_d1;

assign resettime3_rasing_flag = (~resettime3_en_d1) & resettime3_en_d0;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

resettime3_en_d0 <= 1'b0;

resettime3_en_d1 <= 1'b0;

end

else begin

resettime3_en_d0 <= bcodeflag;

resettime3_en_d1 <= resettime3_en_d0;

end

end在bcodeflagone cycle after the falling edge of ,That is, the judgment is completed01之后,进行计算.

(*noprune*)reg [31:0] utc_SecondData;

(*noprune*)reg [31:0] utc_MinuteData;

(*noprune*)reg [31:0] utc_HourData;

(*noprune*)reg [31:0] utc_DayData;

(*noprune*)reg [31:0] utc_YearData;

[email protected](posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

utc_SecondData <= 32'd0;

else if (resettime3_falling_flag == 1'b1)begin

utc_SecondData = utc_sec[0] + 2*utc_sec[1] + 4*utc_sec[2] + 8*utc_sec[3]

+(utc_sec[4] + 2*utc_sec[5] + 4*utc_sec[6])*10;

utc_MinuteData = utc_min[0] + 2*utc_min[1] + 4*utc_min[2] + 8*utc_min[3]

+(utc_min[4] + 2*utc_min[5] + 4*utc_min[6] + 8*utc_min[7])*10;

utc_HourData = utc_hou[0] + 2*utc_hou[1] + 4*utc_hou[2] + 8*utc_hou[3]

+(utc_hou[4] + 2*utc_hou[5] + 4*utc_hou[6] + 8*utc_hou[7])*10;

utc_DayData = utc_day[0] + 2*utc_day[1] + 4*utc_day[2] + 8*utc_day[3]

+(utc_day[4] + 2*utc_day[5] + 4*utc_day[6] + 8*utc_day[7])*10

+(utc_day[8] + 2*utc_day[9])*100;

utc_YearData = utc_yea[0] + 2*utc_yea[1] + 4*utc_yea[2] + 8*utc_yea[3]

+(utc_yea[4] + 2*utc_yea[5] + 4*utc_yea[6] + 8*utc_yea[7])*10;

end

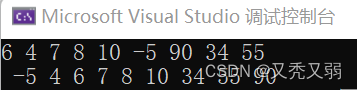

endIn this way, the corresponding value is calculated at the last pulse widthutc时间.

第二章:波形验证

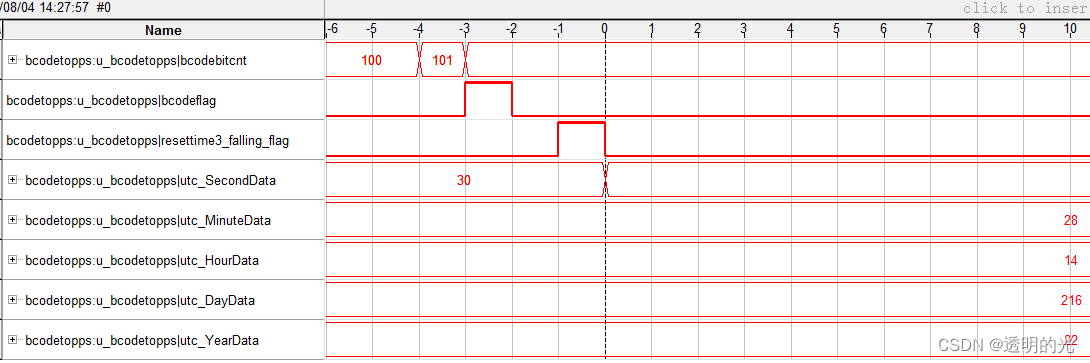

接入BIt can be seen after the code,cnt到100,然后变为101,But becomes before latching0.之后再resetime3subsequent falling edge,BThe second time of the code can be seen to be31s,and other times14点28,The year corresponds to 22,即2022年,验证后,天数为216天,即2022年8月4日.Of course this is just verificationUTCtime decoding,Other key information has not been extracted.It should be possible to put other information into a register in the same way.

第三章:存在的BUG

[email protected](posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

bcodebitcnt <= 8'd0;

else if (bpluse_falling_flag == 1)

bcodebitcnt <= bcodebitcnt + 1'b1;

else if (bcodereadyflag == 1)

bcodebitcnt <= 8'd3;

else if (bcodebitcnt == 8'd101)

bcodebitcnt <= 0;

else

bcodebitcnt <= bcodebitcnt;

end

[email protected](posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

bcodeflag <= 1'd0;

else if (bpluse_falling_flag == 1)

bcodeflag <= 1'd0;

else if (bcodebitcnt == 8'd101)

bcodeflag <= 1'd1;

else

bcodeflag <= 1'd0;

endThis code outputs two quantities,一个是cnt,That is, when there is no latch,在B码的下降沿时,从0到100,After latching from3到100.另一个是bcodeflag,Equals when the falling edge comes0,当cnt等于101时变为1.The problem here isThere are no latches for bothB码的P标志时,cnt也会变为101,这样bcodeflag也会变为1,也即utcTime also counts,这个就比较麻烦了.

第四章:1PPS怎么输出

1PPS的上升沿和2个PThe rising edge of the second pulse width in the flag coincides,So two must be judgedP帧之后,在下一个1s中的时候,第2个BThe pulse is output at the rising edge of the pulse width of the code.Two options are now considered:

(1)方案1:判断2个P标志之后,定时器开启,在995ms的时候输出1个flag,然后1005ms时输出0flag,然后将Bcode signal with thisflag与一下,That is the output pulse1PPS的上升沿.

(2)方案2:判断2个P标志之后,在1sBThe next one after the code1s的第一个P标志之后,输出1个flag,Then output a certain widthflag,然后将Bcode signal with thisflag与一下,You can also output the corresponding 1PPS脉冲的上升沿.

Don't consider other passed parameters,仅仅考虑utc时间的话,在600msCan solve the specificutc时间,所以在下一个1pps之前,There's nothing wrong with being prepared.

The following problems occur to be solved:

(1)B码在2个PThere is a problem with the signal after the flag bit,BThe code disappears in the middle,之后Bcode continues to appear.

(2)B码在2个PThere is a problem with the signal after the flag bit,BThe code interval is fixed time,即之后的PThe frame is just right,Bcode appears again.

So it feels like it can be locked2个P帧是关键,之后无论BHow did the code disappear,Just on the next one2个Pwhen the frame arrives,Given high andBcode and that's it,所以选择第1The plan is relatively stable.

至于Bcode disappears,utcHow to solve time,This needs to be considered again.

So solve it according to the idea of the first solution1PPS的输出问题.

边栏推荐

猜你喜欢

随机推荐

D45_Camera assembly Camera

typescript61-泛型工具类型(pick)

邮件管理 过滤邮件

【FAQ】什么是 Canon CCAPI

防抖函数和节流函数

HelloWorld

VSCode编写OpenCV

七夕!专属于程序员的浪漫表白

LaTeX 图片加标题 文本分栏自动换行

【5】Docker中部署MySQL

Promise (三) async/await

利用将网页项目部署到阿里云上(ngnix)

(2022杭电多校六)1012-Loop(单调栈+思维)

typescript60-泛型工具类型(readonly)

一天学会从抓包到接口测试,通过智慧物业项目深度解析

技术分析模式(七)发挥差距

In-depth analysis if according to data authority @datascope (annotation + AOP + dynamic sql splicing) [step by step, with analysis process]

深夜小酌,50道经典SQL题,真香~

深入分析若依数据权限@datascope (注解+AOP+动态sql拼接) 【循序渐进,附分析过程】

MySQL表操作练习