当前位置:网站首页>Start from the bottom structure and learn the introduction of fpga---fifo IP core and its key parameters

Start from the bottom structure and learn the introduction of fpga---fifo IP core and its key parameters

2022-07-06 00:08:00 【Lonely single knife】

List of articles

2.3、FIFO IP Nuclear performance

2.6.1、 Programmable full signal Programmable Full

2.6.2、 Programmable null signal Programmable Empty

2.8、 Asymmetric read / write bit width

Series catalog and portal

《 Start with the underlying structure FPGA》 Directory and portal

1、FIFO brief introduction

FIFO The full name is First In First Out, First in, first out , It refers to a buffer with FIFO characteristics for data storage .FIFO And RAM and ROM The difference is that there is no external read-write address line , Write data sequentially , The way in which data is read out sequentially , It's easy to use , The disadvantage of this is that it can't be like RAM and ROM That can be done by Address line Decide to read or write to a specified address .

FIFO It is often used for data caching , Or the interaction of high-speed asynchronous data, that is, the so-called cross clock domain signal transmission , such as DDR Reading and writing data of . Or, Conversion of data with different bit widths , Such as writing 16 Bit wide data , Read again 8 Bit wide data .

According to reading 、 Whether the write operation uses the same clock can put FIFO There are two kinds of :

- Sync FIFO: The read-write clock is the same clock , Temporary simultaneous read and write operations occur at the edge of the clock . It is often used for data cache under synchronous clock .

- asynchronous FIFO: Reading and writing clocks are different , Read and write clocks are independent of each other . It is often used for data transmission in different clock domains , Because if the clock is different , Metastable state may occur during data acquisition , Cause data transmission error , Use asynchronous FIFO It can synchronize the data in different clock domains to the required clock domain , Make the data transmission stable .

asynchronous FIFO Due to the asynchronous clock used , So its interior is divided into Two clock domains -- Read clock field and write clock field . And synchronization FIFO Words , Then there is only one clock signal , So its IP There is only A clock field .

2、Xilinx FIFO IP nucleus

xilinx Of vivado Free... Is provided IP----FIFO Generate For our use , as follows :

2.1、 Interface

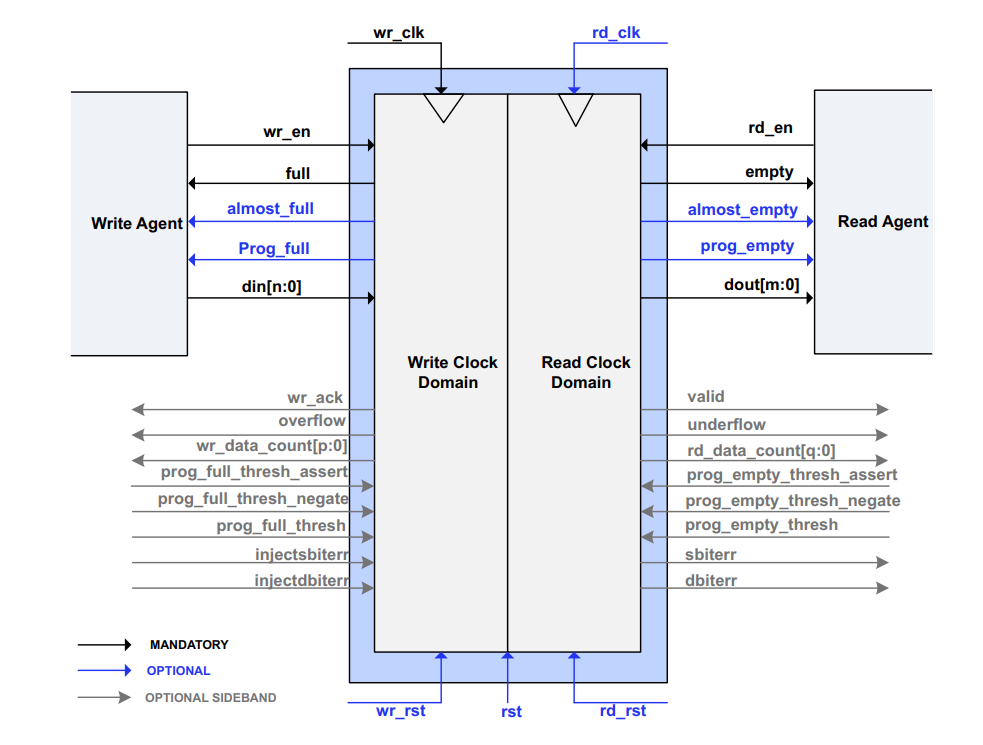

FIFO IP The core provides two external interfaces :

Native Interface : The original default interface , Including reading enable 、 Write enable , Input 、 Output , empty 、 Wait for a series of signals

AXI4 Interface : AXI4 The interface is actually Native Repackaging of interfaces , Can achieve AXI4,AXI3,AXI4-Lite and AXI4-Streaming. As you can see below ,AXI4 Interface FIFO In addition to writing data 、 Reading is a classic AXI4 Beyond the handshake agreement , Image space 、 The full signal is directly output . About AXI4 Interface , Let's not expand here , There will be a chance to update later .

2.2、 Realization way

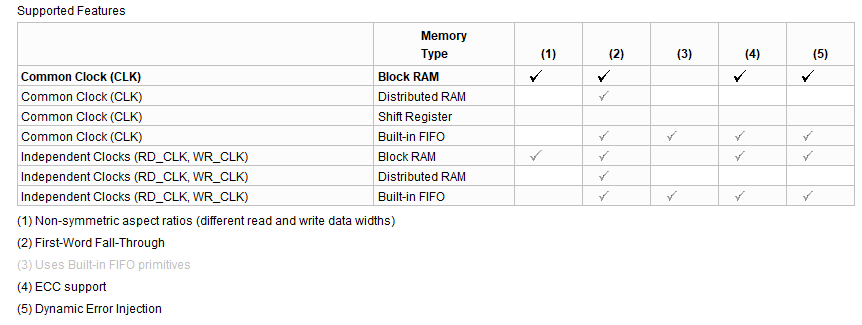

FPGA Rich internal resources , therefore FIFO IP The implementation of core can also adopt different resource forms :

- Block RAM:BRAM resources , This is a FPGA Storage resources embedded in the bottom , No matter it can be achieved FIFO, At the same time, it can also realize RAM、ROM

- Distributed RAM: Distributed RAM, The essence is the underlying logical resources LUT,

- Shift Register: shift register , The essence is still the underlying logical resources LUT,

- Built-in FIFO: The embedded FIFO, amount to BRAM Resources are externally encapsulated FIFO Associated interface

Although different resources can be used to achieve FIFO It provides us with great flexibility , But shortcomings also exist ---- Due to different implementation methods , Composed of different types FIFO The functions that can be realized are also inconsistent .

For example, the following table ( come from FIFO IP Core customization interface ) Medium Built-in FIF Asynchronous composition of resources FIFO, Can be real 2、3、4、5, But the function cannot be realized 1---- Read differently 、 Write data bit width .

2.3、FIFO IP Nuclear performance

FIFO IP We usually quantify the performance of a nuclear directly as The highest frequency that can run , According to the different implementation resources and use FPGA Different devices , Its performance varies greatly .

Limited to space , We won't give examples here , If you are interested, please check 《pg057-fifo-generator》 The first 2 Chapter Performance. The basic rule is ,Virtex-7 Device's FIFO>Kintex-7 Device's FIFO>Artix-7 Device's FIFO.

2.4、 Write operations

To achieve FIFO Right Write operations You need to know the signals related to the write operation and the timing of the write . The following are the signals related to the write operation .

- wr_clk: Write clock signal

- wr_en: Write enable signal , High active

- din: To write FIFO The data of

- almost_full: Almost full of signals , High active , Valid means FIFO Write only The last data 了

- full: Full signal , High active , Valid means FIFO Is full , No more data can be written 了

- wr_ack: Write response signal , No choice , High level or low level can be configured to be effective ; When it is valid, it means that a successful write has been made FIFO operation

- overflow: Overflow signal , No choice , High level or low level can be configured to be effective ; Valid means in FIFO A write operation was performed when it was in the full state

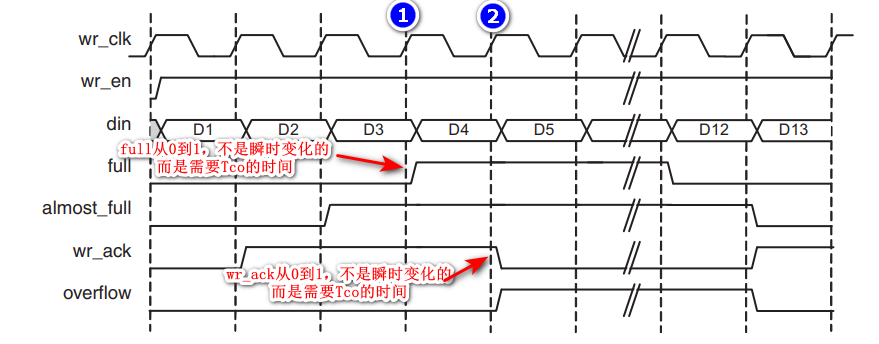

Before understanding the writing sequence , It is important to note that : The change of data is not Instantaneous , It takes time , This time is Tco. As shown in the picture below :

- In cycle ①, Have already put FIFO It's full. , therefore full The signal will change to 1, because Tco The existence of ,full The change of signal is not instantaneous , But in a slope , This takes time from 0 To 1 Later, I personally call it pull up .

- In cycle ②, Have already put FIFO It's full. , therefore wr_alkc The signal will no longer respond , Will turn into 0, because Tco The existence of ,wr_alkc The change of signal is not instantaneous , But in a slope , This takes time from 1 To 0 Later, I personally call it lowering .

After knowing these two points , Let's take a look at the sequence diagram of write operation : ( green Indicates that the write was successful , Red Indicates a write failure )

- ①: Write enable wr_en by 0, Input din No data

- ②: Write enable wr_en by 1, Input din by D1;wr_ack Be pulled high , Indicates write data D1 success

- ③: Write enable wr_en by 1, Input din by D2;wr_ack by 1, Indicates write data D2 success ;almost_full pull up , Express FIFO Almost full ( You can also write a data )

- ④: Write enable wr_en by 1, Input din by D3;wr_ack by 1, Indicates write data D3 success ;almost_full by 1, Express FIFO Almost full ;full pull up , Express FIFO Is full , You can't write data anymore

- ⑤: Write enable wr_en by 1, Input din by D4;wr_ack Pulled down , Indicates write data D4 You don't succeed ;almost_full by 1, Express FIFO Almost full ;full by 1, Express FIFO Is full ;overflow Be pulled high , Indicates that there is a write full ( stay FIFO Write when full ) operation

- ⑥: Write enable wr_en by 1, Input din by D5;wr_ack by 0, Indicates write data D5 You don't succeed ;almost_full by 1, Express FIFO Almost full ;full by 1, Express FIFO Is full ;overflow by 1, Indicates that there is a write full ( stay FIFO Write when full ) operation

- follow-up : Yes FIFO After reading , Repeat the write operation

2.5、 Read operations

To achieve FIFO Right Read operations You need to know the signals related to the reading operation and the reading timing . The following are the signals related to the read operation .

- rd_clk: Read the clock signal

- rd_en: Read enable signal , High active

- dout: from FIFO The data read out in

- almost_empty: Almost empty signal , High active , Valid means FIFO Can only Read out the last data 了

- empty: Empty signal , High active , Valid means FIFO It's empty , Can't read data anymore 了

- valid:

- The standard model : Effective signal , No choice , High level or low level can be configured to be effective ; When valid, it means the data read at this time dout It works , When an invalid read operation is performed ( Read when empty ) when , This signal will be pulled down

- Forward mode : Effective signal , No choice , High level or low level can be configured to be effective ; When valid, it means the data read at this time dout It works , as long as FIFO When there is at least one data readable in ,valid It's effective ; When FIFO If there is no data to read, it will be pulled down

- underflow: Underflow signal , No choice , High level or low level can be configured to be effective ; Valid means in FIFO A read operation was performed when it was empty

Reading operation is special , There are two modes : The standard model (Standard) and Forward mode (First-Word Fall-Through,FWFT).

The standard mode is the default mode , Issue a read command , The first data will be read after a certain delay . The forward mode is before issuing the read instruction , The next data that will be read out will be put on the output bus .

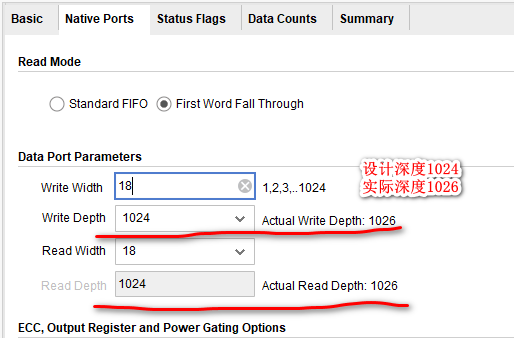

The front mode looks good , There is no delay in the output of data , But I suggest you don't use explicit mode , Because of the particularity of the explicit mode , It will be strange in many places , Very counterintuitive . For example, the actual depth of the front display mode will be more than the set , The accuracy of data counting will also deteriorate .

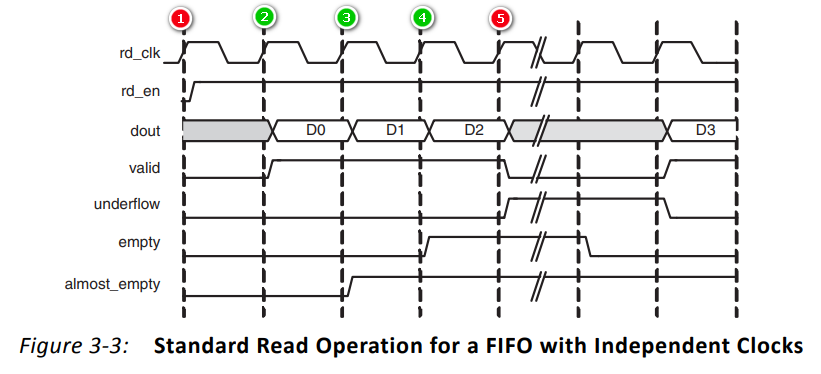

(1) The standard model ( green Indicates that the read was successful , Red Indicates a read failure )

- ①: Reading enable rd_en by 0, Output dout No data

- ②: Reading enable rd_en by 1, Output dout data D0;valid Be pulled high , Express dout The data of is valid data

- ③: Reading enable rd_en by 1, Output dout data D1;valid by 1, Express dout The data of is valid data ;almost_empty Be pulled high , Express FIFO Almost empty , There is only one data left

- ④: Reading enable rd_en by 1, Output dout data D2;valid by 1, Express dout The data of is valid data ;almost_empty by 1, Express FIFO Almost empty ;empty Be pulled high , Express FIFO empty , All the data has been read

- ⑤: Reading enable rd_en by 1, Output dout No data ;valid Pulled down , Express dout The data of is invalid ;almost_empty by 1, Express FIFO Almost empty ;empty by 1, Express FIFO empty ;underflow Be pulled high , It means to FIFO Read operation is performed

- follow-up : Yes FIFO Write after operation , Repeat the read operation

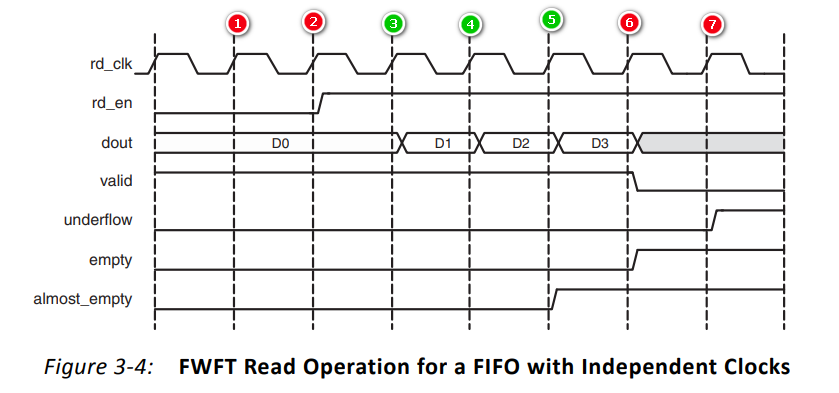

(2) Forward mode ( green Indicates that the read was successful , Red Indicates a read failure )

- ①: Reading enable rd_en by 0, Output dout data D0;valid by 1, Express dout The data of is valid data

- ②: Reading enable rd_en by 0, Output dout data D0;valid by 1, Express dout The data of is valid data

- ③: Reading enable rd_en by 1, Output dout data D1;valid by 1, Express dout The data of is valid data

- ④: Reading enable rd_en by 1, Output dout data D2;valid by 1, Express dout The data of is valid data

- ⑤: Reading enable rd_en by 1, Output dout data D3;valid by 1, Express dout The data of is valid data ;almost_empty Be pulled high , Express FIFO Almost empty , Only the last data

- ⑥: Reading enable rd_en by 1, Output dout No data ;valid Pulled down , Express dout The data of is invalid ;almost_empty by 1, Express FIFO Almost empty ;empty Be pulled high , Express FIFO empty , There is no data

- ⑦: Reading enable rd_en by 1, Output dout No data ;valid by 0, Express dout The data of is invalid ;almost_empty by 1, Express FIFO Almost empty ;empty position 1, Express FIFO empty ;underflow Be pulled high , It means that FIFO Read operation in empty state

- follow-up : Yes FIFO Write after operation , Repeat the read operation

It should be noted that , Different from the standard mode , The null signal in the front display mode will lag behind the last data by one clock cycle ( In standard mode , cycle ④ Read the last data , At the same time, the spatiotemporal signal is also pulled up ; And in the front mode , cycle ⑤ Read the last data , But the empty signal is periodic ⑥ Be pulled high , One clock cycle behind ).

Because of the particularity of the null signal timing of the front-end mode , Make it The actual depth will be more than the design depth 2.

The last thing to note is this , Forward mode empty The signal will be pulled down two clock cycles after the first data is written .

2.6、 Programmable signal

reading 、 Writing the operation chapter, we learned that it is almost empty 、 Almost full 、 empty 、 Fill these four instructions FIFO Signal of medium data volume , But in practical applications , Sometimes we need to get it at a specific time FIFO Information about . For example, I designed a depth of 100 Of FIFO, Hope to be in FIFO The amount of data in is 10 It will be output to the later stage , While the data volume is not enough 10 when , I hope not FIFO Read operation . This is the time FIFO Programmable null ( full ) Signals come in handy .

- Programmable full (prog_full): Can be used to indicate the current FIFO The programmable full threshold set by the user has been reached . For example, set the programmable full threshold to 80,FIFO Depth is 100, Then when FIFO The data in is greater than or equal to 80 After a ,prog_full The signal will be pulled up , until FIFO The number of data in is less than 80 Will pull down .

- Programmable null (prog_empty) : Can be used to indicate the current FIFO The programmable empty threshold set by the user has been reached . For example, set the programmable null threshold to 20,FIFO Depth is 100, Then when FIFO The data in is less than or equal to 20 After a ,prog_empty The signal will be pulled up , until FIFO The number of data in is greater than 20 Will pull down .

When FIFO When the amount of data in reaches the programmable threshold , Can still be right FIFO Keep reading and writing , These signals are only used as a Indicating signal To instruct the user to respond to FIFO To operate .

Be careful :prog_full There will be 1 Clock cycles delay , and prog_full The release of is delayed longer , It depends on the read-write clock relationship .

2.6.1、 Programmable full signal Programmable Full

Programmable full signal Programmable Full Provides 4 Class setting mode For our use :

- ①:Single threshold constant:

- Users can directly access the IP The kernel generation interface specifies a threshold , Once specified, it cannot be changed , Unless you regenerate FIFO IP nucleus . This method is relative to ②, Less resource consumption , When flexibility is poor .

- ② :Single threshold with dedicated input port:

- User pass prog_full_thresh Signal to specify a threshold , This threshold can be in FIFO Change on reset . This method is relative to ①, More resources are consumed , But it gains more flexibility .

- ③ :Assert and negate threshold constants (provides hysteresis)

- Users can directly access the IP The kernel generation interface specifies 2 Thresholds ( A set , The other one failed ), Once specified, it cannot be changed , Unless you regenerate FIFO IP nucleus . This method is relative to ④, Less resource consumption , When flexibility is poor .

- ④ :Assert and negate thresholds with dedicated input ports (provides hysteresis)

- User pass prog_full_thresh_assert Signal to specify the set threshold , adopt prog_full_thresh_negate Signal to specify the failure threshold . this 2 The threshold can be FIFO Change on reset . This method is relative to ③, More resources are consumed , But it gains more flexibility .

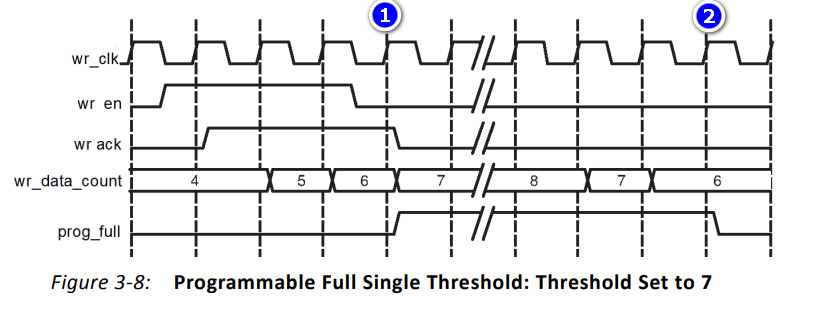

The following figure shows that only Single programmable null threshold Sequence diagram :

- ①: stay FIFO The amount of data is 6 when , The actual amount of data reaches the threshold 7, Programmable full signal prog_full Be pulled high ; then FIFO The data is always greater than or equal to the threshold 7, therefore prog_full Continued as 1

- ②:FIFO The data is less than the threshold 7, Programmable full signal prog_full Pulled down

- Be careful :wr_data_count The counting quantity has a periodic delay , When it is 6 when ,FIFO The actual amount of data in is 7, So for 6 when prog_full Will be pulled up . The following article will not be repeated

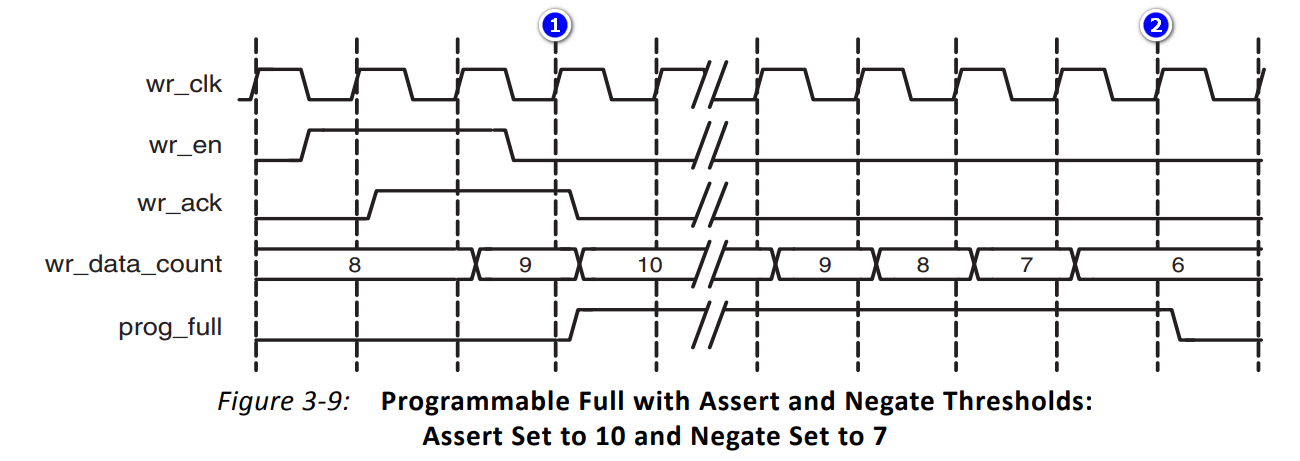

The following figure shows that Programmable vacancy threshold and failure threshold Sequence diagram :

- ①: stay FIFO The amount of data is 9 when , Set threshold reached 10, Programmable full signal prog_full Be pulled high ;

- ②:FIFO The data is less than the failure threshold 7, Programmable full signal prog_full Pulled down

- Be careful : The full set value must be greater than the full failure value .

2.6.2、 Programmable null signal Programmable Empty

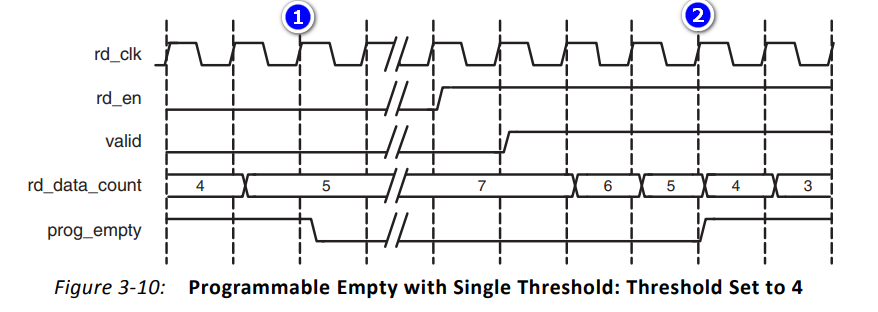

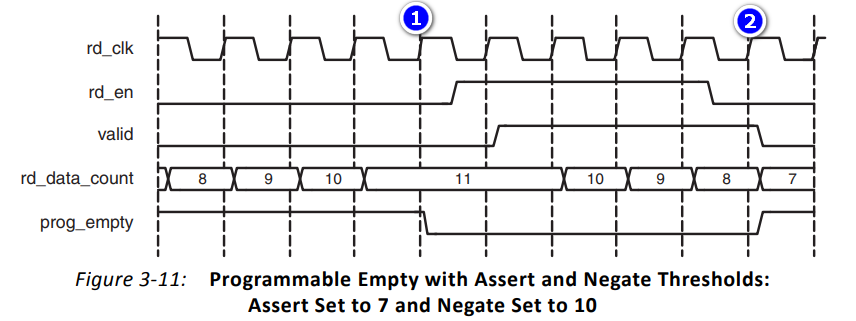

Programmable null signal Programmable Empty The use method of is basically consistent with the programmable full signal , So I won't introduce it in detail , Just look at two sequence diagrams :

- ①: In cycle ① Before ,FIFO The amount of data is 4, Equal to the threshold of programmable null 4, therefore prog_empty Always high . To cycle ①FIFO The medium quantity is from 4 Turn into 5, The programmable null condition is no longer satisfied ,prog_empty Pulled down

- ②: At present FIFO The amount of data in is 5, And a read operation is performed , So touch the threshold of programmable null 4,prog_empty Be pulled high

- ①: In cycle ① Before ,FIFO The amount of data is greater than the set threshold 7, therefore prog_empty Always high . To cycle ①FIFO The amount of data becomes 11, Meet the failure threshold 10, therefore prog_empty Pulled down

- ②: At present FIFO The amount of data in is 8, And a read operation is performed , So touch the programmable null set threshold 7,prog_empty Be pulled high

- Be careful : The vacancy value must be less than the null failure value .

2.7、 Data count

In some application scenarios , We may wish we could Real time tracking FIFO Number of data in . It should be noted that :

- Sync FIFO The data count of is accurate , The reading and writing clocks should be the same , There is no need to synchronize across clocks .

- asynchronous FIFO The count value of is Not accurate enough , This is a FIFO The implementation method of , Because it takes time for the data count under the read-write clock domain to synchronize to the other clock domain . So asynchronous FIFO Count of Precise use is not recommended , It can only be judged roughly , For example, half empty 、 half-full 、1/4 empty 、1/4 Man et al .

Although the data count in the asynchronous clock domain is inaccurate , But it is It won't be right FIFO Function . Because read count and write count are conservative counts , The purpose of this is to prevent reading empty and writing full , Thus causing read and write errors .

- The data count of the write clock will conservatively report the write FIFO The amount of data in , It will not be less than the actual amount of data , That is to say, the data may be larger than the actual , To ensure that users will not be right FIFO Write empty . for instance FIFO depth 100, Write the clock count value as 100, At this time, users will think FIFO Is full and stops checking FIFO Write operation . The actual amount of data may be 98, Although in the end 2 Space will not be used , lost 2% Performance of , But it will not affect FIFO The function of . So writing counts is conservative .

- The data count of the read clock will conservatively report the read FIFO The amount of data in , It will not be greater than the actual amount of data , That is to say, the data may be smaller than the actual , To ensure that users will not be right FIFO Read empty . for instance FIFO depth 100, The reading clock count value is 0, At this time, users will think FIFO It is empty, so stop checking FIFO Read it . The actual amount of data may be 2, Although in the end 2 Space will not be used , lost 2% Performance of , But it will not affect FIFO The function of . So reading count is conservative .

About asynchrony FIFO The design principle of this part can be referred to : About asynchrony FIFO Design , this 7 You have to find out

2.8、 Asymmetric read / write bit width

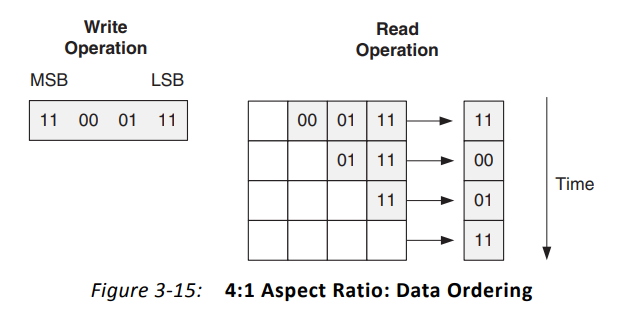

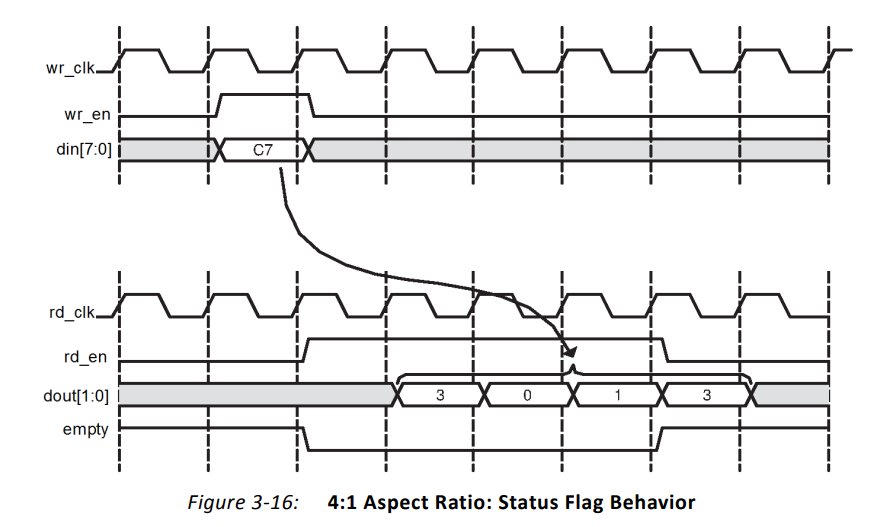

The conversion read-write bit width is also FIFO It has an important function , We can write at one time 16bit The data of , And only read at a time 4bit The data of . read 、 The bit width of writing data can be different , But it must meet the proportional relationship :1:8, 1:4, 1:2, 1:1, 2:1, 4:1, 8:1.

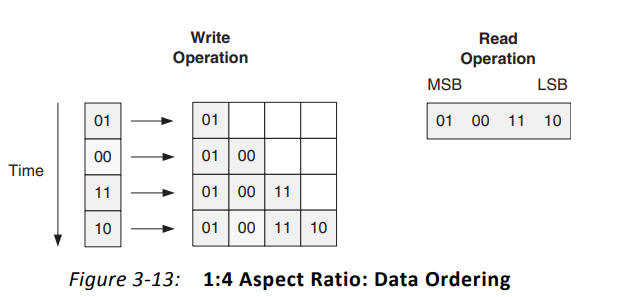

In the case of asymmetric read-write bit width , One thing that must be made clear is the sorting of data .

(1) Write bit width > Read bit width

If write bit width 8, Read bit width 2, When the data I write is 00011011, Then the first data read out is 11 still 00?

The following figure shows writing 8bit, Read 2bit Data sorting of , The result is that the reading is from high to MSB Down to the bottom LSB Of , write in 11000111, branch 4 Read it for times 11--00--01--11.

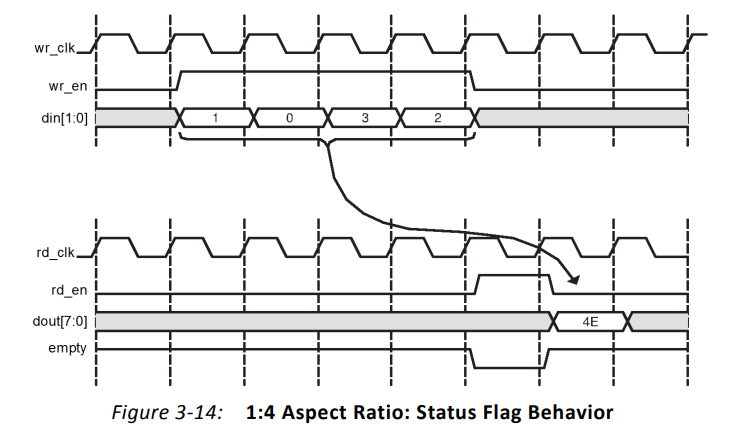

And the behavior of empty signal is also related to the whole FIFO Is linked to the amount of data . as follows , write in 8bit After the data ,empty I.e. failure , At present FIFO Not empty . Dangfen 4 Time , Read once 2bit, Co read 8bit After the data ,FIFO Empty again .

(2) Write bit width < Read bit width

alike , If write bit width 2, Read bit width 8, When I write data in four times, they are 01 00 11 10, Then the first data read out is 01001110 still 10110001?

The following figure shows writing 2bit, Read 8bit Data sorting of , The result is the data written for the first time 01 It will be in the highest reading position MSB, And the first 4 Data written for times 10 Will be in the lowest bit of the read LSB.

And the behavior of empty signal is also related to the whole FIFO Is linked to the amount of data . as follows , branch 4 Write... Times in total 8bit After the data ,empty I.e. failure , At present FIFO Not empty . When reading once 8bit After the data ,FIFO Empty again .

2.9、 Reset

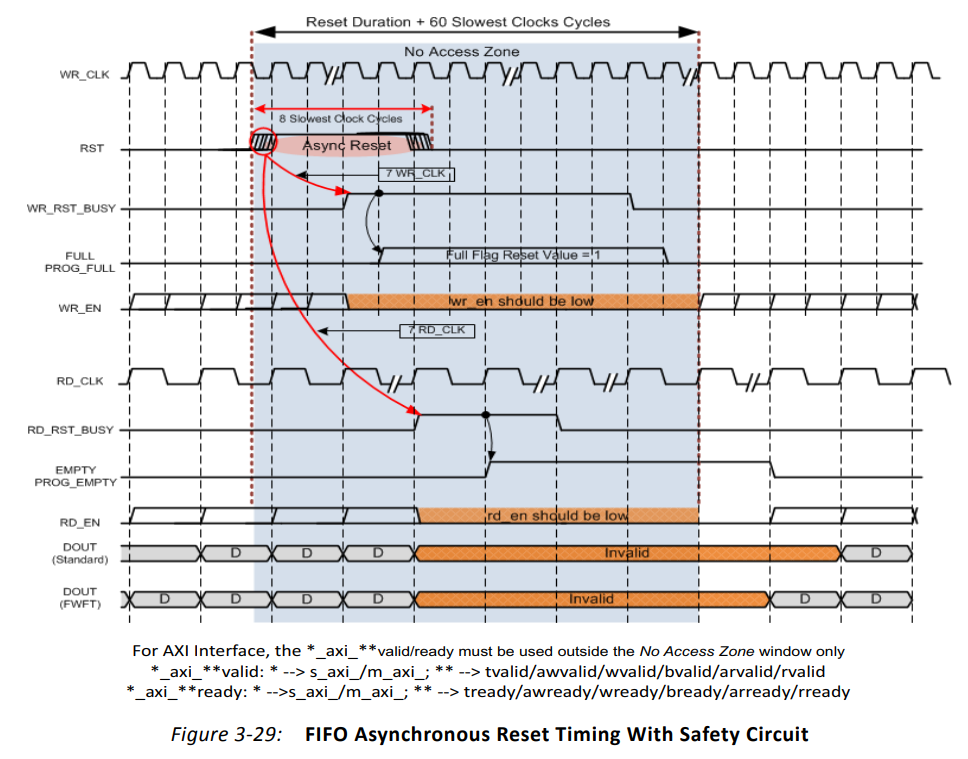

stay FPGA To configure IP Postnuclear , In the face of FIFO Before operation , It must be reset . So don't use it immediately after power on FIFO, It should be reset now , And it will not be used until several cycles after reset FIFO. The clock signal must work normally during reset .

shift register FIFO and built-in FIFO The reset signal of is not optional , That is, there must be . about shift register FIFO and 7 Series of built-in FIFO,Xilinx Only asynchronous reset is provided ; And for UltraScale, Reset is a synchronous reset signal , But provided w_rst_busy and rd_rst_busy The output signal indicates FIFO Whether the reset has been completed .

Block RAM FIFO and Distributed RAM FIFO The reset signal of is optional . For those who share a clock FIFO, The difference between selecting synchronous reset and asynchronous reset mainly lies in whether the reset signal is synchronized with the common clock ; When asynchronous reset is selected , Sure Enable Safety Circuit, As the name suggests, it is to make the circuit safer , That is, complete the signal through reset wr_rst_busy and rd_rst_busy To indicate whether or not FIFO Reset completed .

The following figure shows an asynchronous reset sequence with a safety circuit , We usually use FIFO This sequence should be observed when :

2.10、 Actual depth

One particular thing to note is , Due to different implementation methods , The design of the FIFO The actual depth of may be different from the expected value , We can do it in Vivado FIFO IP Customize the interface of the core to obtain the actual depth information :

- Blog home page :wuzhikai.blog.csdn.net

- This paper is written by Lonely single blade original , First appeared in CSDN platform

- The article is still being updated , Do you have any questions , You can communicate with me in the comment area !

- It's not easy to create , Your support is the biggest driving force for me to continuously update ! If this article helps you , Please give me more praise 、 Reviews and collections !

边栏推荐

- wx.getLocation(Object object)申请方法,最新版

- 剖面测量之提取剖面数据

- 零犀科技携手集智俱乐部:“因果派”论坛成功举办,“因果革命”带来下一代可信AI

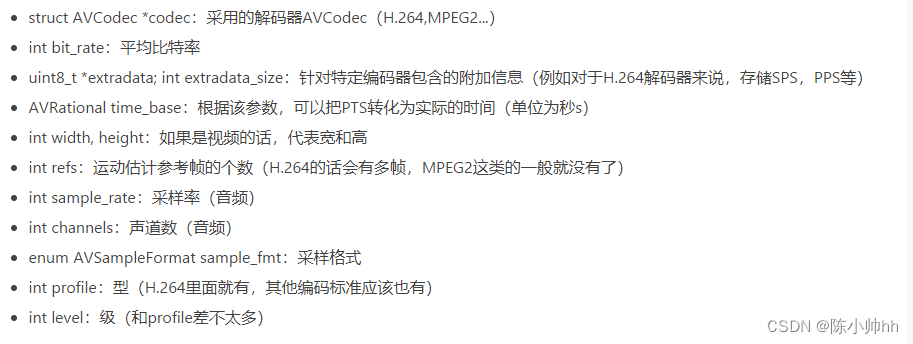

- Key structure of ffmpeg - avframe

- [designmode] adapter pattern

- Permission problem: source bash_ profile permission denied

- What if the C disk is not enough? Let's see how I can clean up 25g of temp disk space after I haven't redone the system for 4 years?

- 选择致敬持续奋斗背后的精神——对话威尔价值观【第四期】

- FFMPEG关键结构体——AVCodecContext

- Initialize your vector & initializer with a list_ List introduction

猜你喜欢

Mysql - CRUD

After summarizing more than 800 kubectl aliases, I'm no longer afraid that I can't remember commands!

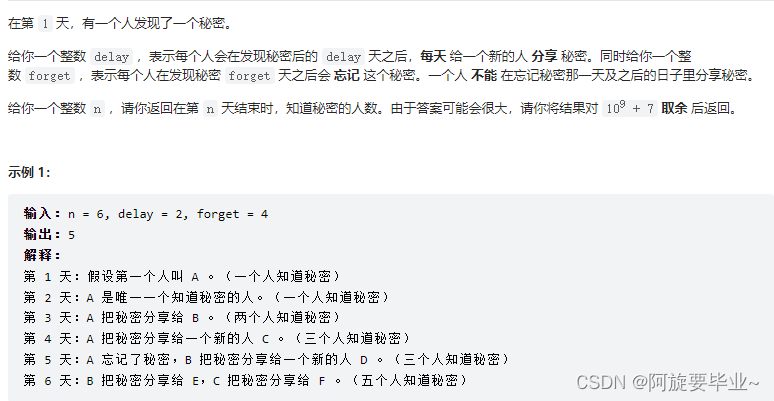

20220703 周赛:知道秘密的人数-动规(题解)

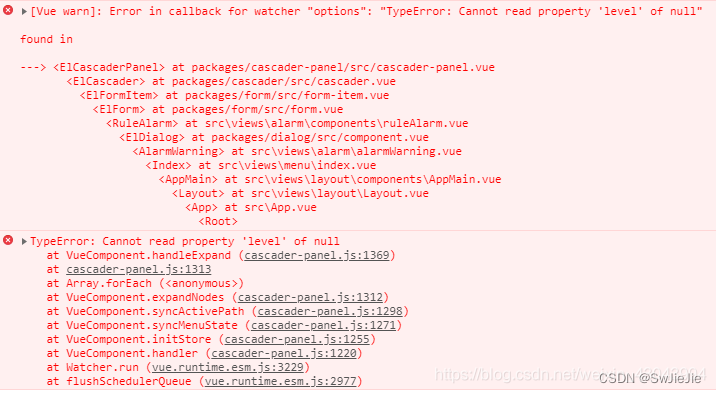

The use of El cascader and the solution of error reporting

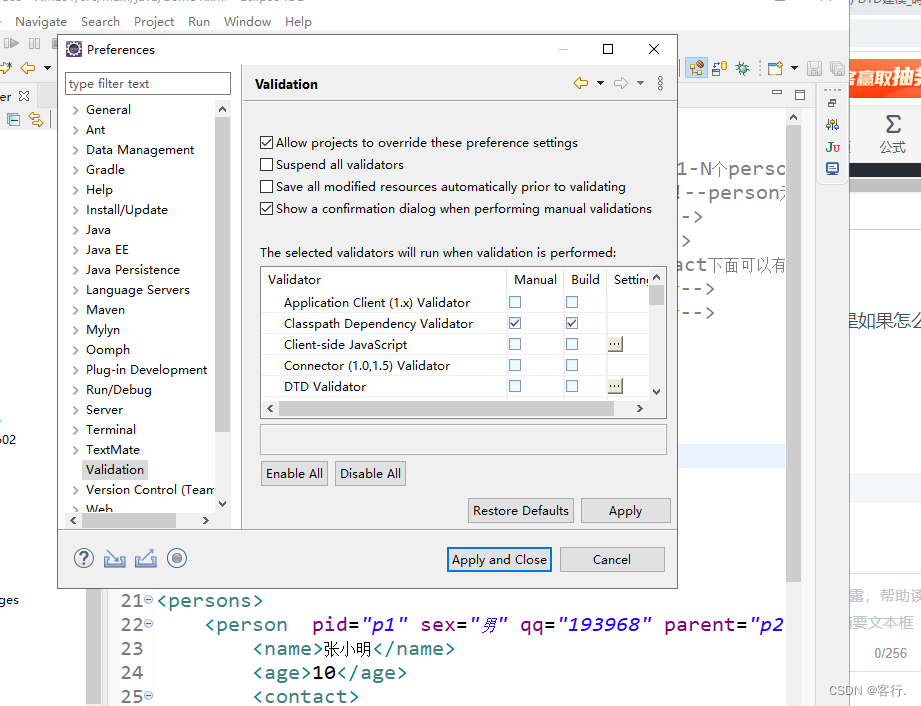

XML配置文件(DTD详细讲解)

![[noi simulation] Anaid's tree (Mobius inversion, exponential generating function, Ehrlich sieve, virtual tree)](/img/d6/c3128e26d7e629b7f128c551cd03a7.png)

[noi simulation] Anaid's tree (Mobius inversion, exponential generating function, Ehrlich sieve, virtual tree)

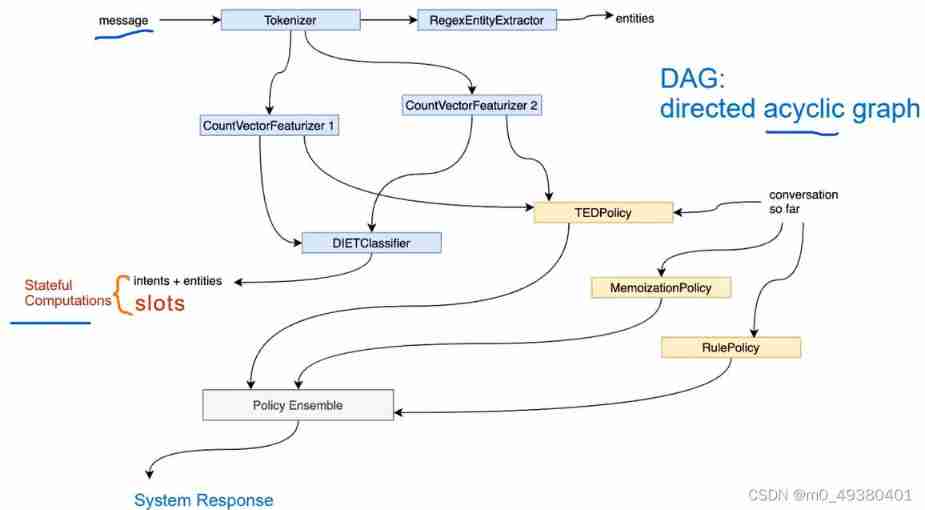

Gavin teacher's perception of transformer live class - rasa project actual combat e-commerce retail customer service intelligent business dialogue robot system behavior analysis and project summary (4

Single merchant v4.4 has the same original intention and strength!

![[online chat] the original wechat applet can also reply to Facebook homepage messages!](/img/d2/1fd4de4bfd433ed397c236ddb97a66.png)

[online chat] the original wechat applet can also reply to Facebook homepage messages!

Key structure of ffmpeg -- AVCodecContext

随机推荐

微信小程序---WXML 模板语法(附带笔记文档)

认识提取与显示梅尔谱图的小实验(观察不同y_axis和x_axis的区别)

JVM details

Tips for using pads router

2022.7.5-----leetcode.729

Configuring OSPF GR features for Huawei devices

Key structure of ffmpeg -- AVCodecContext

零犀科技携手集智俱乐部:“因果派”论坛成功举办,“因果革命”带来下一代可信AI

Zhongjun group launched electronic contracts to accelerate the digital development of real estate enterprises

【在线聊天】原来微信小程序也能回复Facebook主页消息!

PADS ROUTER 使用技巧小记

[designmode] composite mode

Cloudcompare & PCL point cloud randomly adds noise

Use mapper: --- tkmapper

7.5 simulation summary

JS 这次真的可以禁止常量修改了!

MySQL functions

【EF Core】EF Core与C# 数据类型映射关系

Knowledge about the memory size occupied by the structure

[gym 102832h] [template] combination lock (bipartite game)