当前位置:网站首页>1. Mx6u-alpha development board (main frequency and clock configuration experiment)

1. Mx6u-alpha development board (main frequency and clock configuration experiment)

2022-07-26 04:09:00 【*Ruthless*】

List of articles

One 、 Hardware schematic analysis

1、32.768khz The crystal of , Co payment RTC Use .

2、 stay 6U Of T16 and T17 these two items. IO The last one was 24MHz The crystal of .

Two 、I.MX6U System clock analysis

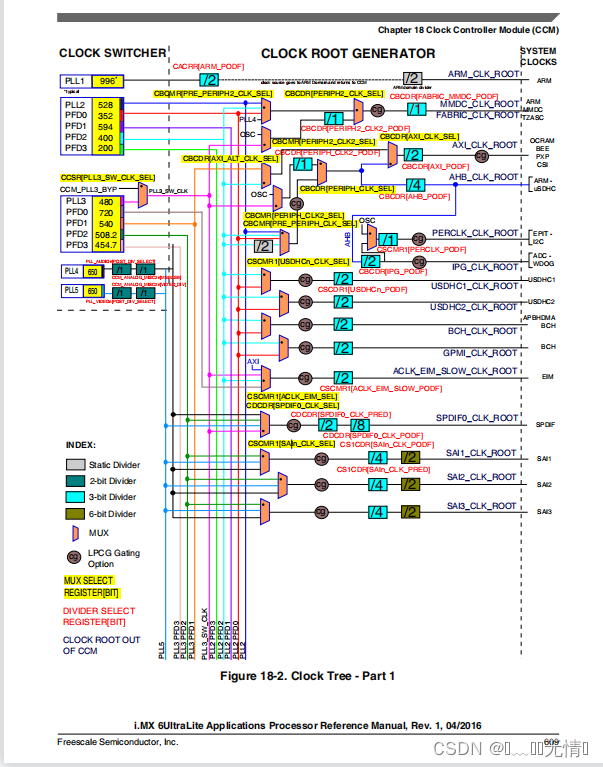

1、7 road PLL

In order to facilitate the generation of clock ,6 from 24MHz The crystal oscillator comes out 7 road PLL. this 7 road PLL Some of them are born again PFD.

PLL1:ARM PLL supply ARM kernel .

PLL2:system PLL,528MHz,528_PLL, This road PLL It's divided 4 road PFD, Respectively PLL2_PFD0~PFD3

PLL3: USB1 PLL,480MHz 480_PLL, This road PLL It's divided 4 road PFD, Respectively PLL3_PFD0~PFD3.

PLL4: Audio PLL, It is mainly used for audio .

PLL5: Video PLL, Main video peripherals , such as RGB LCD Interface , Peripherals related to image processing .

PLL6:ENET PLL, Main supply network peripherals .

PLL7: USB2_PLL ,480MHz, nothing PFD.

2、 All the way PLL Separated PFD

3、 Clock tree

4、 How do peripherals choose the right clock

such as ESAI Clock source selection :

PLL4、PLL3_PFD2、PLL5、PLL3.

5、 To initialize PLL and PFD

PLL1,

PLL2, as well as PLL2_PFD0~PFD3.

PLL3 as well as PLL3_PFD0~PFD3.

Generally, it is set according to the value in the clock tree .

3、 ... and 、I.MX6U The system configuration

1、 Configuration of system main frequency

①、 To set up ARM The dominant frequency of the kernel is 528MHz, Set up CACRR The register of ARM_PODF Position as 2 frequency division , Then set the PLL1=1056MHz that will do .CACRR Of bit3 ~ 0 by ARM_PODF position , Can be set up 0 ~ 7, They correspond to each other 1~8 frequency division . Should be set CACRR The register of ARM_PODF=1.

②、 Set up PLL1=1056MHz.PLL1=pll1_sw_clk.pll1_sw_clk There are two options , Respectively pll1_main_clk, and step_clk, adopt CCSR The register of pll1_sw_clk_sel position (bit2) Choose . by 0 When to choose pll1_main_clk, by 1 When to choose step_clk.

③、 In the revision PLL1 When , That is, when setting the system clock, you need to give 6ULL A temporary clock , That is to say step_clk. In the revision PLL1 When it comes to pll1_sw_clk Switch to step_clk On .

③、 Set up step_clk.Step_clk There are also two sources , from CCSR Of step_sel position (bit8) To set up , by 0 When setting step_clk by osc=24MHz. by 1 It doesn't matter when , no need .

④、 After the clock switch is successful, it can be modified PLL1 Value .

⑤、 adopt CCM_ANALOG_PLL_ARM The register of DIV_SELECT position (bit6~0) To set up PLL1 The frequency of , Formula bit :

Output = fref * DIV_SEL/2 1056=24*DIV_SEL/2=>DIEV_SEL=88.

Set up CCM_ANALOG_PLL_ARM The register of DIV_SELECT position =88 that will do .PLL1=1056MHz

Also set CCM_ANALOG_PLL_ARM The register of ENABLE position (bit13) by 1, That is, enable output .

⑥、 Switching back to PLL1 Before , Set up CACRR The register of ARM_PODF=1!! Bear in mind .

2、 each PLL Clock configuration

PLL2 and PLL3.PLL2 Fixed for 528MHz,PLL3 Fixed for 480MHz.

①、 initialization PLL2_PFD0~PFD3. register CCM_ANALOG_PFD_528 Used for setting up 4 road PFD The clock of . such as PFD0= 52818/PFD0_FRAC. Set up PFD0_FRAC Who can . such as PLL2_PFD0=352M=52818/PFD0_FRAC, therefore FPD0_FRAC=27.

②、 initialization PLL3_PFD0~PFD3

3、 Clock source configuration of other peripherals

AHB_CLK_ROOT、PERCLK_CLK_ROOT as well as IPG_CLK_ROOT.

because PERCLK_CLK_ROOT and IPG_CLK_ROOT Want to use AHB_CLK_ROOT, So we need to initialize AHB_CLK_ROOT.

①、AHB_CLK_ROOT The initialization .

AHB_CLK_ROOT=132MHz.

Set up CBCMR The register of PRE_PERIPH_CLK_SEL position , Set up CBCDR The register of PERIPH_CLK_SEL position 0. Set up CBCDR The register of AHB_PODF Position as 2, That is to say 3 frequency division , therefore 396/3=132MHz.

②、IPG_CLK_ROOT initialization

Set up CBCDR register IPG_PODF=1, That is to say 2 frequency division .

③、PERCLK_CLK_ROOT initialization

Set up CSCMR1 The register of PERCLK_CLK_SEL Position as 0, Express PERCLK The clock source of is IPG.

//bsp_clk.h

#include "imx6ul.h"

/* Function declaration */

void clk_enable(void);

void imx6u_clkinit(void);

#endif

//bsp_clk.c

#include "bsp_clk.h"

void clk_enable(void)

{

CCM->CCGR0 = 0XFFFFFFFF;

CCM->CCGR1 = 0XFFFFFFFF;

CCM->CCGR2 = 0XFFFFFFFF;

CCM->CCGR3 = 0XFFFFFFFF;

CCM->CCGR4 = 0XFFFFFFFF;

CCM->CCGR5 = 0XFFFFFFFF;

CCM->CCGR6 = 0XFFFFFFFF;

}

// Initialize the system clock , Set the system clock to 792Mhz, And set up PLL2 and PLL3 each PFD The clock , All clock frequencies follow I.MX6U The value recommended by the official manual .

void imx6u_clkinit(void)

{

unsigned int reg = 0;

/* 1、 Set up ARM The kernel clock is 792MHz 1.1、 Judge the present ARM The kernel is started by the clock source used , Under normal circumstances ARM The kernel is made up of pll1_sw_clk Driven , and pll1_sw_clk There are two sources :pll1_main_clk and tep_clk. If we want to let ARM The kernel runs 792M You must choose pll1_main_clk As pll1 The clock source of . If we want to modify pll1_main_clk If you clock, you must first set pll1_sw_clk from pll1_main_clk Switch to step_clk, When the modification is finished pll1_main_clk In the future pll1_sw_clk Switch back to the pll1_main_clk. and step_clk You can choose the clock source on the board 24MHz Crystal oscillator . */

if((((CCM->CCSR) >> 2) & 0x1 ) == 0) /* At present pll1_sw_clk The use of pll1_main_clk*/

{

CCM->CCSR &= ~(1 << 8); /* To configure step_clk The clock source is 24MH OSC */

CCM->CCSR |= (1 << 2); /* To configure pll1_sw_clk The clock source is step_clk */

}

/* 1.2、 Set up pll1_main_clk by 792MHz * because pll1_sw_clk Into the ARM The kernel will be divided into two frequencies ! * To configure CCM_ANLOG->PLL_ARM register * bit13: 1 Enable clock output * bit[6:0]: 66, By formula :Fout = Fin * div_select / 2.0,792=24*div_select/2.0, * obtain :div_select= 66 */

CCM_ANALOG->PLL_ARM = (1 << 13) | ((66 << 0) & 0X7F); /* To configure pll1_main_clk=792MHz */

CCM->CCSR &= ~(1 << 2); /* take pll_sw_clk The clock switches back to pll1_main_clk */

CCM->CACRR = 0; /* ARM The kernel clock is pll1_sw_clk/1=792/1=792Mhz */

/* 2、 Set up PLL2(SYS PLL) each PFD */

reg = CCM_ANALOG->PFD_528;

reg &= ~(0X3F3F3F3F); /* Clear the original settings */

reg |= 32<<24; /* PLL2_PFD3=528*18/32=297Mhz */

reg |= 24<<16; /* PLL2_PFD2=528*18/24=396Mhz(DDR The clock used , Maximum 400Mhz) */

reg |= 16<<8; /* PLL2_PFD1=528*18/16=594Mhz */

reg |= 27<<0; /* PLL2_PFD0=528*18/27=352Mhz */

CCM_ANALOG->PFD_528=reg; /* Set up PLL2_PFD0~3 */

/* 3、 Set up PLL3(USB1) each PFD */

reg = 0; /* Zero clearing */

reg = CCM_ANALOG->PFD_480;

reg &= ~(0X3F3F3F3F); /* Clear the original settings */

reg |= 19<<24; /* PLL3_PFD3=480*18/19=454.74Mhz */

reg |= 17<<16; /* PLL3_PFD2=480*18/17=508.24Mhz */

reg |= 16<<8; /* PLL3_PFD1=480*18/16=540Mhz */

reg |= 12<<0; /* PLL3_PFD0=480*18/12=720Mhz */

CCM_ANALOG->PFD_480=reg; /* Set up PLL3_PFD0~3 */

/* 4、 Set up AHB The clock Minimum 6Mhz, Maximum 132Mhz (boot rom It can be set automatically without setting )*/

CCM->CBCMR &= ~(3 << 18); /* Clear settings */

CCM->CBCMR |= (1 << 18); /* pre_periph_clk=PLL2_PFD2=396MHz */

CCM->CBCDR &= ~(1 << 25); /* periph_clk=pre_periph_clk=396MHz */

while(CCM->CDHIPR & (1 << 5));/* Wait for the handshake to complete */

/* modify AHB_PODF It is necessary to prohibit AHB_CLK_ROOT Output , however * I didn't find the closure AHB_CLK_ROOT Output register , So you can't set . * Set below AHB_PODF The code is for learning reference only and cannot be used directly !! * Inside boot rom take AHB_PODF Set up in order to 3 frequency division , Even if we don't set AHB_PODF, * AHB_ROOT_CLK Still equal to 396/3=132Mhz. */

#if 0

/* Shut down first AHB_ROOT_CLK Output , Otherwise, the clock setting will be wrong */

CCM->CBCDR &= ~(7 << 10); /* CBCDR Of AHB_PODF Zero clearing */

CCM->CBCDR |= 2 << 10; /* AHB_PODF 3 frequency division ,AHB_CLK_ROOT=132MHz */

while(CCM->CDHIPR & (1 << 1));/

* Wait for the handshake to complete */

#endif

/* 5、 Set up IPG_CLK_ROOT Minimum 3Mhz, Maximum 66Mhz (boot rom It can be set automatically without setting )*/

CCM->CBCDR &= ~(3 << 8); /* CBCDR Of IPG_PODF Zero clearing */

CCM->CBCDR |= 1 << 8; /* IPG_PODF 2 frequency division ,IPG_CLK_ROOT=66MHz */

/* 6、 Set up PERCLK_CLK_ROOT The clock */

CCM->CSCMR1 &= ~(1 << 6); /* PERCLK_CLK_ROOT The clock source is IPG */

CCM->CSCMR1 &= ~(7 << 0); /* PERCLK_PODF A reset , namely 1 frequency division */

}

边栏推荐

- Go plus security: an indispensable security ecological infrastructure for build Web3

- 华为高层谈 35 岁危机,程序员如何破年龄之忧?

- 【读书笔记->数据分析】01 数据分析导论

- (翻译)网站流程图和用户流程图的使用时机

- php中可以使用取绝对值函数 abs() 将负数转成正数

- General test case writing specification

- Write a paper for help, how to write the discussion part?

- Dracoo Master天龙卡牌大师

- 2022杭电多校 Bowcraft

- CPU and GPU are out of date, and the era of NPU and APU begins

猜你喜欢

Pathmatchingresourcepatternresolver parsing configuration file resource file

Pat class a 1039 course list for student

MySQL index failure scenarios and Solutions

Luoda Development -- the context of sidetone configuration

firewall 命令简单操作

Opencv learning notes -- Hough transform

零售连锁门店收银系统源码管理商品分类的功能逻辑分享

《opencv学习笔记》-- 边缘检测和canny算子、sobel算子、LapIacian 算子、scharr滤波器

【SVN】一直出现 Please execute the ‘Cleanup‘ command,cleanup以后没有反应的解决办法

Share | 2022 big data white paper of digital security industry (PDF attached)

随机推荐

当你尝试删除程序中所有烂代码时 | 每日趣闻

laravel8 实现接口鉴权封装使用JWT

Method of test case design -- move combination, causal judgment

Implementation of distributed lock

PHP 对象转换数组

VM虚拟机 没有未桥接的主机网络适配器 无法还原默认配置

How engineers treat open source -- the heartfelt words of an old engineer

Where does international crude oil open an account, a formal, safe and secure platform

在 Istio 服务网格内连接外部 MySQL 数据库

软模拟光栅化渲染器

Linear basis property function code to achieve 3000 words detailed explanation, with examples

雅迪高端之后开始变慢

`Oi problem solving ` ` leetcode '2040. The k-th minor product of two ordered arrays

PHP save array to var file_ export、serialize

Pathmatchingresourcepatternresolver parsing configuration file resource file

1311_ Hardware design_ Summary of ICT concept, application, advantages and disadvantages

Laravel8 implements interface authentication encapsulation using JWT

电商运营小白,如何快速入门学习数据分析?

【SVN】一直出现 Please execute the ‘Cleanup‘ command,cleanup以后没有反应的解决办法

[question 019: what is the understanding of spherecastcommand in unity?]