当前位置:网站首页>[digital ic/fpga] detect the position of the last matching sequence

[digital ic/fpga] detect the position of the last matching sequence

2022-06-27 23:52:00 【FPGA silicon agriculture】

Title Description

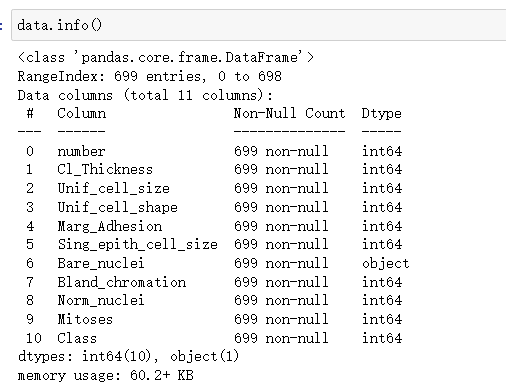

Write a module , Enter a 64 Bit stream of bits , Identify and match out 101101 The last position of , And output position information .

Code

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/06/21 10:34:41

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module top(

input logic clk,

input logic rst,

input logic valid,

input logic din,

output logic done,

output logic [5:0] pos

);

//101101

logic [5:0] shift_reg;

logic [5:0] cnt;

//cnt

[email protected](posedge clk,posedge rst)

if(rst)

cnt<=0;

else if(valid)

begin

if(cnt==64-1)

cnt<=0;

else

cnt<=cnt+1;

end

//shift_reg

[email protected](posedge clk,posedge rst)

if(rst)

shift_reg<=0;

else if(valid)

shift_reg<={

shift_reg[4:0],din}; // High order input first

//pos

[email protected](posedge clk,posedge rst)

if(rst)

begin

pos<=64;

end

else if(shift_reg==6'b101101)

begin

pos<=cnt-6;

end

//done

[email protected](posedge clk,posedge rst)

if(rst)

done<=0;

else

done<=(cnt==64-1&&valid)?1:0;

endmodule

Test platform

module test;

logic clk;

logic rst;

logic valid;

logic din;

logic done;

logic [5:0] cnt;

logic [5:0] pos;

logic [63:0] data;

//

initial

begin

//data={12'b101101101101,52'd0};

data={

20'd0,12'b101101101101,32'd0};

end

//clk

initial

begin

clk=0;

forever

#5 clk=~clk;

end

//rst

initial

begin

rst=1;

#100

rst=0;

end

//valid,din

initial

begin

valid<=0;

cnt<=0;

wait(rst==1'b0);

@(posedge clk);

repeat(64)

begin

valid<=1;

din<=data[63-cnt];

cnt<=cnt+1;

@(posedge clk);

end

valid<=0;

end

top U(.*);

/* input logic clk, input logic rst, input logic valid, input logic din, output logic done, output logic [5:0] pos ); */

endmodule

result

Input bitstream is data={20’d0,12’b101101101101,32’d0}, therefore , The position of the last matching sequence should be 20+6=26, In line with expectations .

边栏推荐

- 【AI应用】Jetson Xavier NX的详情参数

- 解决新版chrome跨域问题:cookie丢失以及samesite属性问题「建议收藏」

- 未能加载文件或程序集“CefSharp.Core.Runtime.dll”或它的某一个依赖项。 不是有效的 Win32 应用程序。 (异常来自 HRESULT:0x800700C1)

- 零基础自学SQL课程 | SQL基本函数大全

- go日志包 log的使用

- 抓出那些重复的基因

- Golang uses Mongo driver operation -- Query (array related)

- SQL中IS NOT NULL与!=NULL的区别

- [PCL self study: pclplotter] pclplotter draws data analysis chart

- 刚开始看英文文献,想问一下各位,最初应该怎么看进去?

猜你喜欢

ASP. Net warehouse purchase, sales and inventory ERP management system source code ERP applet source code

Prediction of benign / malignant breast tumors (logistic regression classifier)

What if Fiddler fails to listen to the interface

【PCL自学:Segmentation3】基于PCL的点云分割:区域增长分割

Online JSON to plaintext tool

Discuz small fish game wind shadow legend business gbk+utf8 version template /dz game website template

Vivado FFT IP的使用说明

【tinyriscv verilator】分支移植到正点原子达芬奇开发板

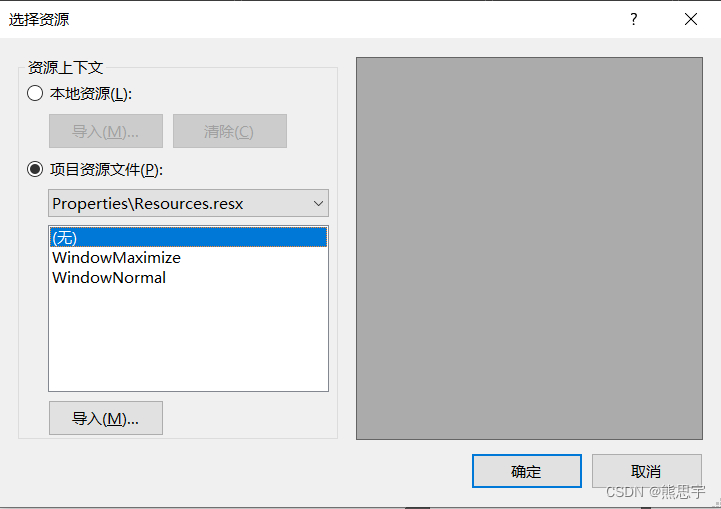

C# Winform 读取Resources图片

![[sword finger offer] 47 Maximum value of gifts](/img/bc/1aff1223b1672c4089151dc56c4d4e.png)

[sword finger offer] 47 Maximum value of gifts

随机推荐

ICML 2022:ufrgs | optimistic linear support and subsequent features as the basis for optimal strategy transfer

文献综述如何挑选文献进行阅读,比如我的检索结果有200多篇根本看不完,如何进行文献挑选呢?...

Small chip chiplet Technology

Excel print settings public header

【Vim】使用教程,常用命令,高效使用Vim编辑器

virtualbox扩展动态磁盘大小的坑

[AI application] detailed parameters of NVIDIA Tesla v100s-pcie-32gb

How to solve the problem that the browser developed with CeF3 does not support flash

Webserver flow chart -- understand the calling relationship between webserver modules

Zero foundation self-study SQL course | complete collection of SQL basic functions

[PCL self study: pclvisualizer] point cloud visualization tool pclvisualizer

十大券商注册账户安全吗,会有风险吗?

解决新版chrome跨域问题:cookie丢失以及samesite属性问题「建议收藏」

【剑指Offer】47. 礼物的最大价值

Although the TCGA database has 33 cancers

【剑指Offer】48. 最长不含重复字符的子字符串

How to use the apipost script - global variables

【数字IC/FPGA】检测最后一个匹配序列的位置

零基础自学SQL课程 | SQL中的日期函数大全

go日志包 log的使用