当前位置:网站首页>Understand chisel language thoroughly 10. Chisel project construction, operation and testing (II) -- Verilog code generation in chisel & chisel development process

Understand chisel language thoroughly 10. Chisel project construction, operation and testing (II) -- Verilog code generation in chisel & chisel development process

2022-07-04 14:09:00 【github-3rr0r】

Chisel The project build 、 Run and test ( Two )——Chisel In the middle of Verilog Code &Chisel Development process

In the last article, we mentioned how to use sbt structure Chisel Project and run Chisel Code , But after all, it still runs on the computer . In practice , We wrote Chisel The code should eventually be integrated into FPGA or ASIC On , So we must put Chisel Translate to a hardware description language that an integrated tool can handle , such as Verilog. How to use it? Chisel Code generation Verilog What about code? ?Chisel What is the development process of ? Let's learn from this article .

Chisel Generate Verilog Code

Chisel It can generate and synthesize Verilog Code , The generation Verilog Just put your code in an application entry . This application portal is a Scala object , It's from App Extended , As mentioned in the previous section , It will implicitly generate the main function when the program starts . There is only one line of code in this application entry , It creates a new Hello object , And pass it to Chisel Of emitVerilog() function , It will generate Hello The module corresponds to Verilog file Hello.v. The code is as follows :

object Hello extends App {

emitVerilog(new Hello())

}

But this call emitVerilog The method of writing will put the generated file into the project root directory by default , Which is running sbt Path to command . If you want to put the generated files in the specified folder , You need to emitVerilog() Specify the options . The build options can be set to emitVerilog() Second parameter of , The parameter type is an array of strings . The last article said Chisel The project directory structure mentioned , It is recommended to put the generated file into generated Under the folder , The following code can realize this requirement :

object HelloOption extends App {

emitVerilog(new Hello(), Array("--target-dir", "generated"))

}

If we don't want to Verilog The code is output as a file , I just want to regard it as Scala If the string is output on the command line , Just use getVerilogString() Function :

object HelloString extends App {

val s = getVerilogString(new Hello())

println(s)

}

This generation method is used in small Chisel It is easy to use in projects , For example, on this web page Led Examples of flashing lights Hello World - Scastie (scala-lang.org), use getVerilogString Function outputs the corresponding Verilog Code .

And this one Scastie It's actually online Scala development environment , If there is no local environment, we can also use this online environment for simple Chisel Development , It can avoid the trouble of matching the environment .

Chisel Tool flow development process

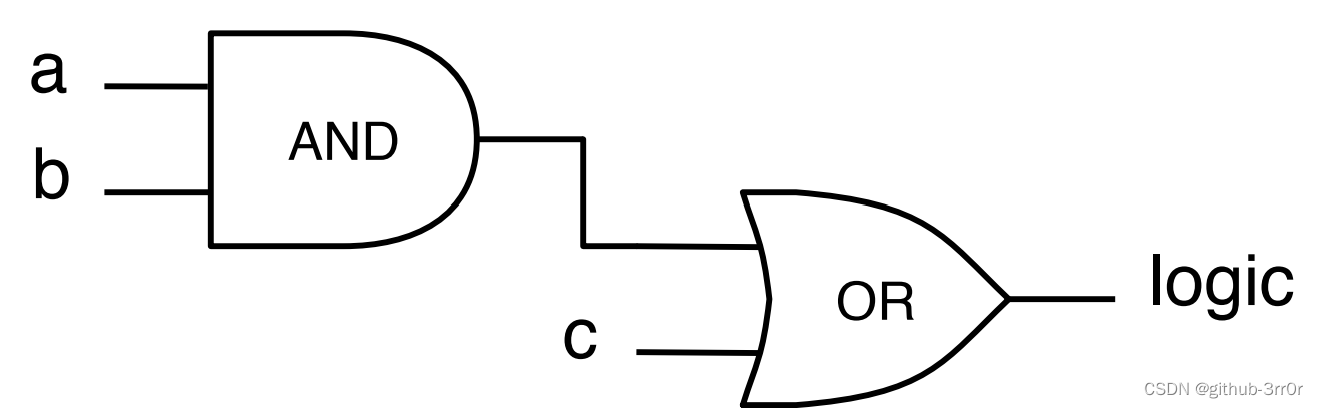

Let's run a simple but complete build Verilog Example , The corresponding circuit is a direct four bit signed input connected to a four bit signed output :

package my.hello

import chisel3._

class ModuleSample extends Module {

val io = IO(new Bundle {

val in_a = Input(SInt(4.W))

val out_b = Output(SInt(4.W))

})

io.out_b := io.in_a

}

object MyModule extends App {

emitVerilog(new ModuleSample(), Array("--target-dir", "generated"))

}

But we can be surprised to see ,generated Except for *.v Of Verilog file , also *.fir Document and *.anno.json file :

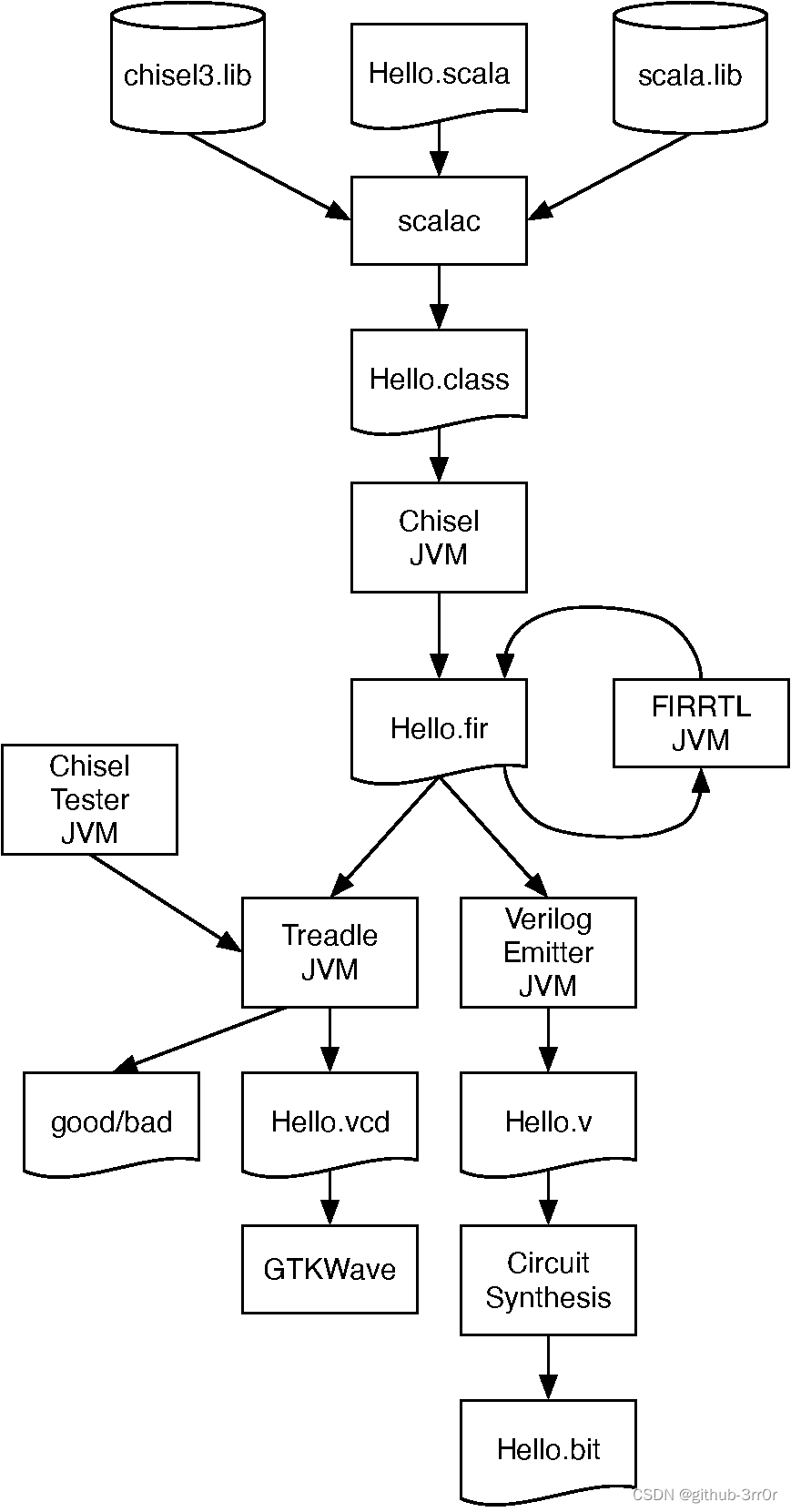

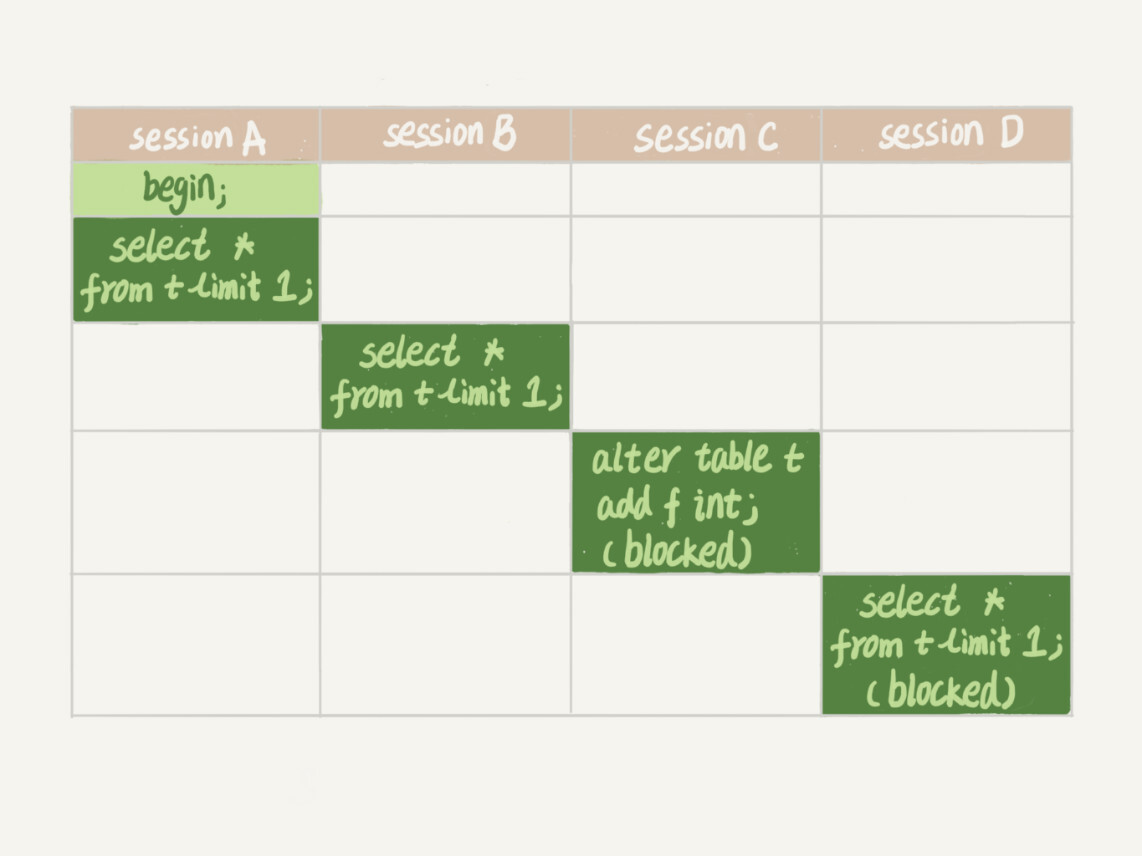

That is, it is not only generated Verilog Code , Other files are also generated , When it comes to the reason, it involves Chisel Our tools are flowing .Chisel The tool flow of is shown in the figure below :

The digital circuit we write is actually Chisel Class , That's what this is Hello.scala, The essence is Scala Source code . but Chisel The difference in Scala The reason is that it is not only used when compiling Scala The library of scala.lib, Also used. Chisel The library of chisel3.lib.

With Chisel Source code ,Scala The compiler of is based on Chisel、Scala Our library generates our code Java Class file Hello.class, That is, bytecode file . Such documents can be found in the standard JVM(Java Virtual Machine,Java virtual machine ) Directly executed on .

use Chisel When the driver executes this bytecode file, it will generate FIRRTL file Hello.fir. This FIRRTL Its full name is Flexible Intermediate Representation for RTL, namely RTL Variable intermediate representation of , Is the middle representation of a digital circuit .FIRRTL The compiler can perform some transformations on the circuit , yes Chisel A key bridge to other hardware description languages , If you want to understand higher order Chisel The content of is even Chisel Open source code to contribute , Then we need to study deeply FIRRTL 了 .

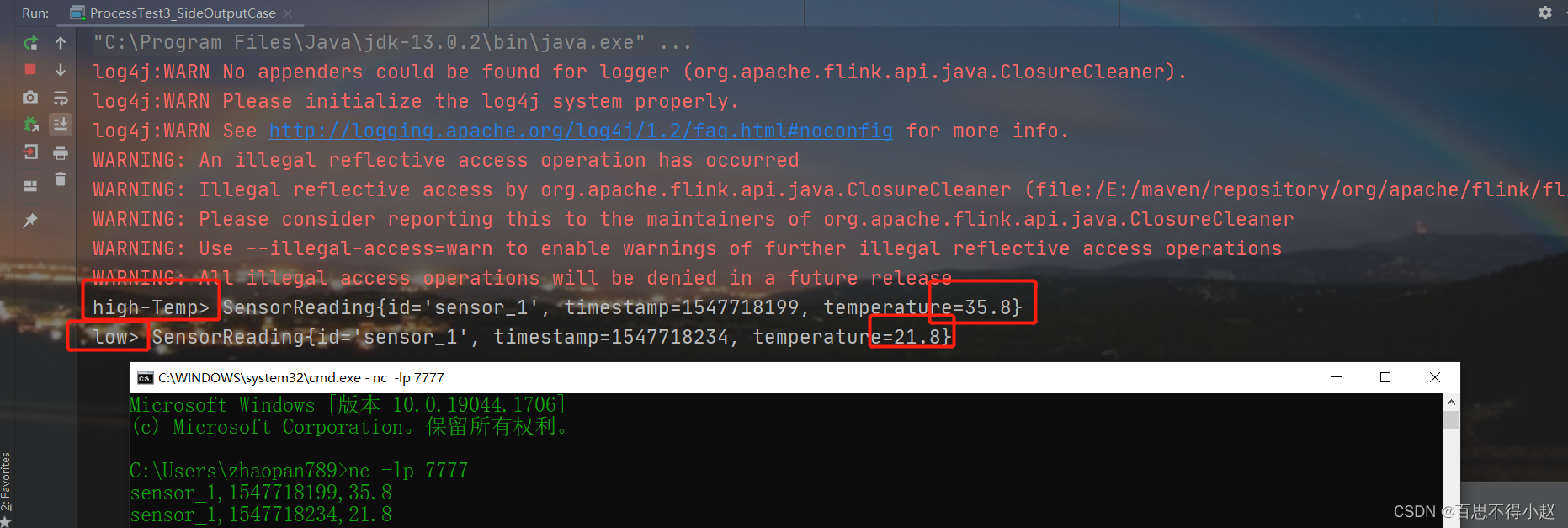

Down again Treadle It's a FIRRTL Interpreter , For circuit simulation . coordination Chisel Tester , It can be used for debugging and testing Chisel circuit . According to the output assertion information, we can get the test results .Treadle You can also generate waveform files , namely Hello.vcd, This waveform file can be viewed with the waveform viewer , For example, you can GTKWare or Modelsim Wait and see .

go back to FIRRTL Compiler part ,Verilog Emitter It's also FIRRTL Transform one , It can be used Hello.fir Generate integrable Verilog Code Hello.v. Then we can use a circuit synthesis tool ( such as Intel Of Quartus,Xilinx Of Vivado Or something else ASIC Tools ) To integrate circuits . stay FPGA Design workflow , The integrated tool will generate FPGA Bitstreams are used to configure FPGA, namely Hello.bit.

Conclusion

Now we have learned how to Chisel In the middle of Verilog Code , Also useful Chisel Have a basic understanding of the tool flow for development . Learned how to compile 、 How to run , Next, you have to learn how to test . We can't try and make mistakes every time we debug , For example, it is generated every time the code is modified FPGA Test the bit stream , In this way, we can't find the error , Second, it takes too long . So it has to be in Chisel Test at stage , This is true for small modules , For larger scale digital circuits, we have to do better testing . The following articles will talk about several Chisel How to use the testing framework , How to write the test code .

边栏推荐

- 吃透Chisel语言.04.Chisel基础(一)——信号类型和常量

- How to choose a technology stack for web applications in 2022

- Basic mode of service mesh

- find命令报错: paths must precede expression(转)

- 奇妙秘境 码蹄集

- Dgraph: large scale dynamic graph dataset

- Apple 5g chip research and development failure: continue to rely on Qualcomm, but also worry about being prosecuted?

- 字节面试算法题

- Ws2811 m is a special circuit for three channel LED drive and control, and the development of color light strip scheme

- Qt如何实现打包,实现EXE分享

猜你喜欢

如何在 2022 年为 Web 应用程序选择技术堆栈

Understanding and difference between viewbinding and databinding

2022 Shandong Province safety officer C certificate examination question bank and online simulation examination

吃透Chisel语言.05.Chisel基础(二)——组合电路与运算符

华昊中天冲刺科创板:年亏2.8亿拟募资15亿 贝达药业是股东

结合案例:Flink框架中的最底层API(ProcessFunction)用法

MySQL 45 lecture - learn the actual combat notes of MySQL in Geek time 45 lecture - 06 | global lock and table lock_ Why are there so many obstacles in adding a field to the table

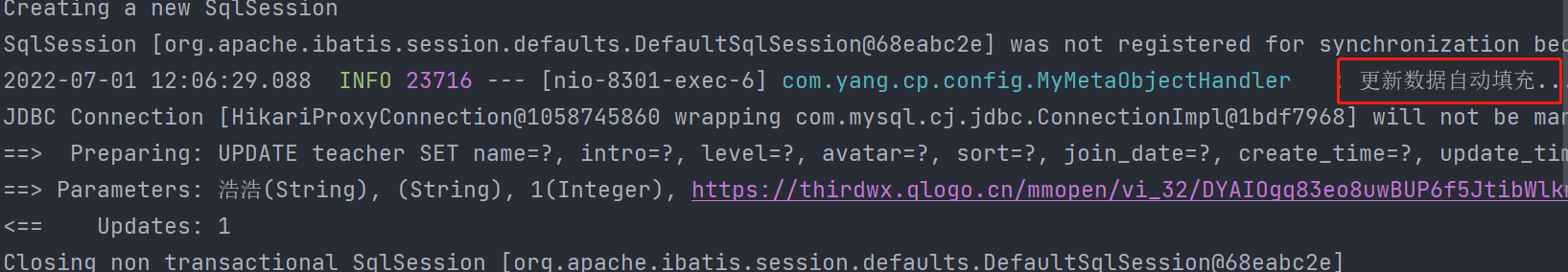

Automatic filling of database public fields

. Net delay queue

德明利深交所上市:市值31亿 为李虎与田华夫妻档

随机推荐

中邮科技冲刺科创板:年营收20.58亿 邮政集团是大股东

Detailed explanation of Fisher information quantity detection countermeasure sample code

2022 Shandong Province safety officer C certificate examination question bank and online simulation examination

Source code compilation and installation of MySQL

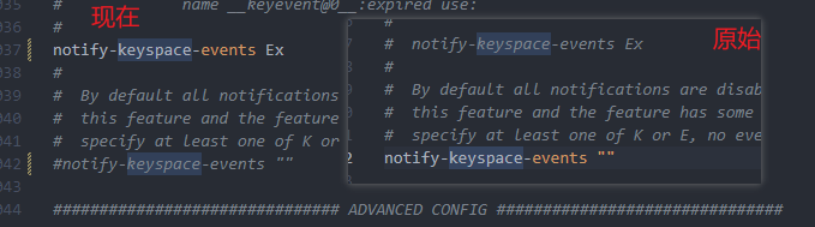

mac redis安装与使用,连接远程服务器 redis

Go 语言入门很简单:Go 实现凯撒密码

【Antd】Antd 如何在 Form.Item 中有 Input.Gourp 时获取 Input.Gourp 的每一个 Input 的value

One of the solutions for unity not recognizing riders

Fs7867s is a voltage detection chip used for power supply voltage monitoring of digital system

392. 判断子序列

【R语言数据科学】:交叉验证再回首

Doctoral application | West Lake University Learning and reasoning system laboratory recruits postdoctoral / doctoral / research internship, etc

2022g3 boiler water treatment examination question simulation examination question bank and simulation examination

Hardware Basics - diode Basics

Install Trinity and solve error reporting

常见 content-type对应表

Product identification of intelligent retail cabinet based on paddlex

Deming Lee listed on Shenzhen Stock Exchange: the market value is 3.1 billion, which is the husband and wife of Li Hu and Tian Hua

Redis —— How To Install Redis And Configuration(如何快速在 Ubuntu18.04 与 CentOS7.6 Linux 系统上安装 Redis)

BLOB,TEXT GEOMETRY or JSON column 'xxx' can't have a default value query 问题