当前位置:网站首页>基于FPGA的VGA协议实现

基于FPGA的VGA协议实现

2022-07-07 01:35:00 【山妖的阶梯】

基于FPGA的VGA协议实现

一、VGA简述

1.VCG接口

VGA(Video Graphics Array)视频图形阵列是IBM于1987年提出的一个使用模拟信号的电脑显示标准。VGA接口即电脑采用VGA标准输出数据的专用接口。VGA接口共有15针,分成3排,每排5个孔,显卡上应用最为广泛的接口类型,绝大多数显卡都带有此种接口。它传输红、绿、蓝模拟信号以及同步信号(水平和垂直信号)。

2.原理

常见接口之色差VGA接口(D-Sub接口)

说到VGA接口,相信很多朋友都不会陌生,因为这种接口是电脑显示器上最主要的接口,从块头巨大的CRT显示器时代开始,VGA接口就被使用,并且一直沿用至今,另外VGA接口还被称为D-Sub接口。

很多人觉得只有HDMI接口才能进行高清信号的传输,但这是一个大家很容易进入的误区,因为通过VGA的连接同样可以显示1080P的图像,甚至分辨率可以达到更高,所以用它连接显示设备观看高清视频是没有问题的,而且虽然它是种模拟接口,但是由于VGA将视频信号分解为R、G、B三原色和HV行场信号进行传输,所以在传输中的损耗还是相当小的 。

VGA接口产生原因: 显卡所处理的信息最终都要输出到显示器上,显卡的输出接口就是电脑与显示器之间的桥梁,它负责向显示器输出相应的图像信号。CRT显示器因为设计制造上的原因,只能接受模拟信号输入,这就需要显卡能输出模拟信号。VGA接口就是显卡上输出模拟信号的接口,VGA(Video Graphics Array)接口,也叫D-Sub接口。虽然液晶显示器可以直接接收数字信号,但很多低端产品为了与VGA接口显卡相匹配,因而采用VGA接口

3.显示器扫描

逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

行(场)同步信号:电视信号发送端为了使接收端的行扫描与场扫描规律与其同步,在行(场)扫描正常结束后,向接收机发出一个脉冲信号,表示这一行(场)已经结束,这个脉冲信号就是行(场)同步信号。

行场消隐信号:电子枪所发出的电子 束从屏幕的左上角开始向右扫描,一行扫完需将电子束从右边移到左边以便扫描第二行。在移动期间就必须有一个信号加到电路上,使得电子束不能发出。不然这个扫线会破坏屏幕图像的。这个阻止扫线产生的信号就叫作消隐信号场信号的消隐也是一个道理。

扫描时间:完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,144Hz等等。

显示带宽:带宽指的显示器可以处理的频率范围。如果是60Hz刷新频率的VGA,其带宽达640x480x60=18.4MHz

4.VGA时序分析

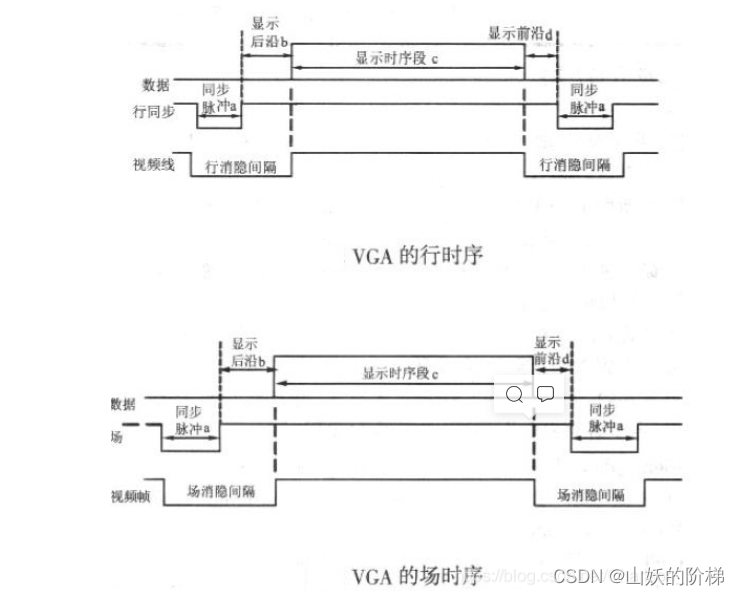

VESA中定义行时序和场时序都需要同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四部分。【同步脉冲要求是负脉冲】

消隐间隔就是上一个时序的显示前沿+本时序的同步脉冲+本时序的显示后沿。

每一行都有一个负极性行同步脉冲(Sync a),是数据行的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿(Back porch b),在显示时序段(Display interval c)显示器为亮的过程,RGB数据驱动一行上的每一个像素点,从而显示一行。在一行的最后为显示前沿(Front porch d)。在显示时间段(Display interval c)之外没有图像投射到屏幕是插入消隐信号。同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)都是在行消隐间隔内(Horizontal Blanking Interval),当消隐有效时,RGB信号无效,屏幕不显示数据

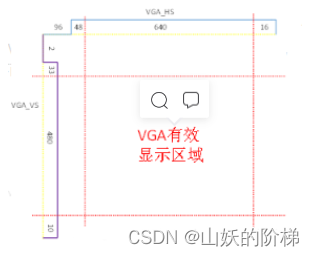

VGA_HS(行同步):在一个周期内,VGA_HS的低电平时间为96个VGA_CLK信号周期,高电平时间为704个VGA_CLK信号周期。VGA的数据信号在VGA_HS高电平的第49个VGA_CLK信号周期开始有效,一直持续到VGA_HS高电平的第688个VGA_CLK信号周期。

其中,96个Hsync脉冲低电平:Sync_pulse = 96;704个周期的Hsync的高电平由分为:Front Porch= 16周期,和BackFront Porch =48周期,剩余的704-16-48=640即为一行的有效数据周期(一个像素周期传送一个像素)

VGA_VS(场同步):在一个周期内,VGA_VS的低电平时间为2个VGA_HS信号周期,高电平时间为523个VGA_HS信号周期。VGA的数据信号在VGA_VS高电平的第34个VGA_HS信号周期开始有效,一直持续到高电平的第513个VGA_HS信号周期。

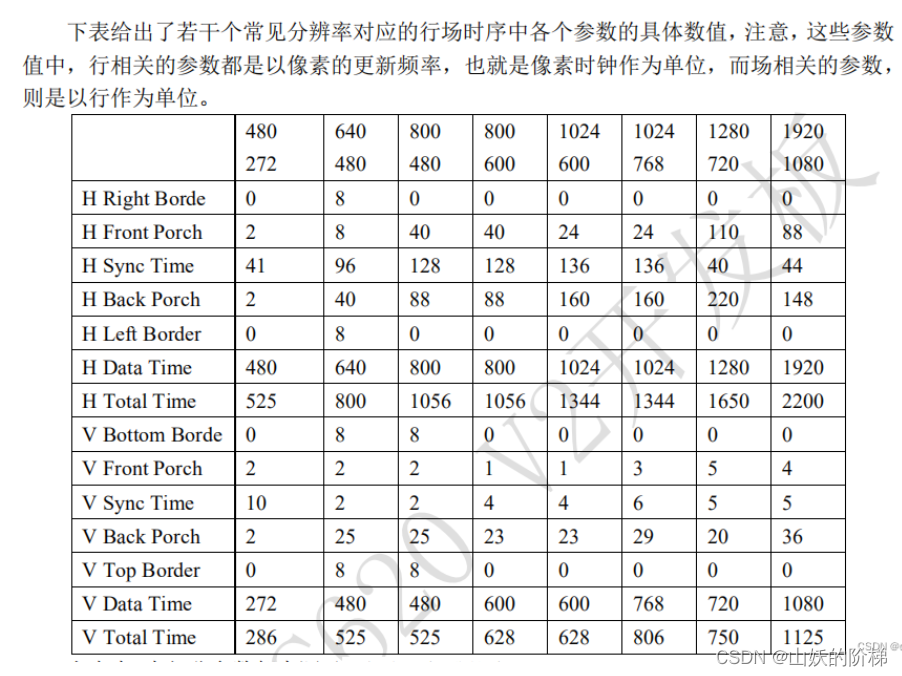

5.VGA时钟计算

对于640* [email protected]即一帧图像的分辨率为640* 480,每秒60的频率帧刷新,则一帧的传输的全部像素个数为800* 525(注意分辨率640* 480指的是有效显示数据的分辨率,而计算时候需要用全分辨率),即

VGA_CLK=HS_total×VS_total×FPS。

6.不同分辨率的VGA参数

二、显示彩条

1.色彩原理

三基⾊是指通过其他颜⾊的混合⽆法得到的“基本⾊”由于⼈的⾁眼有感知红、绿、蓝三种不同颜⾊的锥体细胞,因此⾊彩空间通常可以由三种基本⾊来表达。这是⾊度学的最基本原理,即 三基⾊原理。三种基⾊是相互独⽴的,任何⼀种基⾊都不能有其它两种颜⾊合成。红绿蓝是三基⾊,这三种颜⾊合成的颜⾊范围最为⼴泛。我们的RGB信号真是三基⾊的运⽤,对这三个信号赋予不同的数值,混合起来便是不同的⾊彩。

设计RGB信号时,既可以R信号、G信号和B信号独⽴的赋值,最后连到端⼝上,也可以直接⽤RGB当做⼀个整体信号,RGB信号在使⽤时的位宽有三种常见格式:

- RGB_8,R:G:B = 3:3:2,即RGB332 RGB_16,

- R:G:B = 5:6:5,即RGB565

- RGB_24,R:G:B = 8:8:8,即RGB888

2.彩条输出

参数定义

`define vga_640_480 //`define vga_800_600

`ifdef vga_640_480 `define h_right_border 8

`define h_front_porch 8 `define h_sync_time 96

`define h_back_porch 40 `define h_left_border 8

`define h_data_time 640 `define h_total_time 800

`define v_bottom_border 8 `define v_front_porch 2

`define v_sync_time 2 `define v_back_porch 25

`define v_top_border 8 `define v_data_time 480

`define v_total_time 525 `elsif vga_1280_720

`define h_right_border 0 `define h_front_porch 110

`define h_sync_time 40 `define h_back_porch 220

`define h_left_border 0 `define h_data_time 1280

`define h_total_time 1650 `define v_bottom_border 0

`define v_front_porch 5 `define v_sync_time 5

`define v_back_porch 20 `define v_top_border 0

`define v_data_time 720 `define v_total_time 750

`elsif vga_1920_1080 `define h_right_border 0

`define h_front_porch 88 `define h_sync_time 44

`define h_back_porch 148 `define h_left_border 0

`define h_data_time 1920 `define h_total_time 2200

`define v_bottom_border 0 `define v_front_porch 4

`define v_sync_time 5 `define v_back_porch 36

`define v_top_border 0 `define v_data_time 1080

`define v_total_time 1125 `elsif vga_800_600

`define h_right_border 0 `define h_front_porch 40

`define h_sync_time 128 `define h_back_porch 88

`define h_left_border 0 `define h_data_time 800

`define h_total_time 1056 `define v_bottom_border 0

`define v_front_porch 1 `define v_sync_time 4

`define v_back_porch 23 `define v_top_border 0

`define v_data_time 600 `define v_total_time 628

`endif

VGA驱动

`include "vga_par.v" module vga_ctrl( input wire clk ,//VGA时钟25.2MHz input wire rst_n ,//复位信号 input wire [23:00] data_dis ,// output reg [10:00] h_addr ,//数据有效显示区域行地址 output reg [10:00] v_addr ,//数据有效显示区域场地址 output reg hsync ,// output reg vsync ,// output reg [07:00] vga_r ,// output reg [07:00] vga_g ,// output reg [07:00] vga_b , // output reg vga_blk ,//vga消隐信号 output wire vga_clk // ); //参数定义 parameter h_sync_sta = 1, h_sync_sto = `h_sync_time,

h_data_sta = `h_left_border + `h_front_porch +`h_sync_time, h_data_sto = `h_left_border + `h_front_porch +`h_sync_time + `h_data_time, v_sync_sta = 1, v_sync_sto = `v_sync_time,

v_data_sta = `v_top_border + `v_back_porch +`v_sync_time, v_data_sto = `v_top_border + `v_back_porch +`v_sync_time + `v_data_time; //信号定义 reg [11:0] cnt_h_addr;//行地址计数器 wire add_h_addr; wire end_h_addr; reg [11:0] cnt_v_addr;//场地址计数器 wire add_v_addr; wire end_v_addr; // always @(posedge clk or negedge rst_n) begin if (!rst_n) begin cnt_h_addr <= 12'd0; end else if (add_h_addr) begin if (end_h_addr) begin cnt_h_addr <= 12'd0; end else begin cnt_h_addr <= cnt_h_addr + 12'd1; end end else begin cnt_h_addr <= cnt_h_addr; end end assign add_h_addr = 1'b1; assign end_h_addr = add_h_addr && cnt_h_addr >= `h_total_time - 1;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt_v_addr <= 12'd0; end else if (add_v_addr) begin if (end_v_addr) begin cnt_v_addr <= 12'd0;

end

else begin

cnt_v_addr <= cnt_v_addr + 12'd1; end end else begin cnt_v_addr <= cnt_v_addr; end end assign add_v_addr = end_h_addr; assign end_v_addr = add_v_addr && cnt_v_addr >= `v_total_time - 1; //行场同步信号 always @(posedge clk or negedge rst_n) begin if (!rst_n) begin hsync <= 1'b1;

end

else if(cnt_h_addr == h_sync_sta -1) begin

hsync <= 1'd0; end else if(cnt_h_addr == h_sync_sto -1)begin hsync <= 1'b1;

end

else begin

hsync <= hsync;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

vsync <= 1'b1; end else if(cnt_v_addr == v_sync_sta -1) begin vsync <= 1'd0;

end

else if(cnt_v_addr == v_sync_sto -1)begin

vsync <= 1'b1; end else begin vsync <= vsync; end end assign vga_clk = ~clk; //数据有效显示区域定义 always @(posedge clk or negedge rst_n) begin if (!rst_n) begin h_addr <= 11'd0;

end

else if((cnt_h_addr >= h_data_sta ) && (cnt_h_addr <= h_data_sto) )begin h_addr <= cnt_h_addr - h_data_sta; end else begin h_addr <= 11'd0; end end always @(posedge clk or negedge rst_n) begin if (!rst_n) begin v_addr <= 11'd0; end else if((cnt_v_addr >= v_data_sta ) && (cnt_v_addr <= v_data_sto))begin

v_addr <= cnt_v_addr - v_data_sta;

end

else begin

v_addr <= 11'd0; end end //显示数据 always @(posedge clk or negedge rst_n) begin if (!rst_n) begin vga_r <= 8'd0;

vga_g <= 8'd0; vga_b <= 8'd0;

vga_blk <= 1'b0; end else if((cnt_h_addr >= h_data_sta -1 ) && (cnt_h_addr <= h_data_sto -1 ) && (cnt_v_addr >= v_data_sta -1 ) && (cnt_v_addr <= v_data_sto -1 ))begin vga_r <= data_dis[23-:08]; vga_g <= data_dis[15-:08]; vga_b <= data_dis[07-:08]; vga_blk <= 1'b1;

end

else begin

vga_r <= 8'd0; vga_g <= 8'd0;

vga_b <= 8'd0; vga_blk <= 1'b0;

end

end

//assign sync = 1'b0;

endmodule

顶层文件

module vga_top(

input wire clk ,

input wire rst_n ,

output wire hsync ,//

output wire vsync ,

output wire [07:00] vga_r ,//

output wire [07:00] vga_g ,//

output wire [07:00] vga_b ,//

output wire vga_blk ,

output wire vga_clk //

);

wire [10:00] h_addr ;

wire [10:00] v_addr ;

wire [23:00] data_dis ;

pll1 pll1_inst (

.areset ( ~rst_n ),

.inclk0 ( clk ),

.c0 ( vga_clk ),

.c1 ( clk1 )

);

data_gen u_data_gen(

.clk (vga_clk ),//VGA时钟25.2MHz

.rst_n (rst_n ),//复位信号

.h_addr (h_addr ),//数据有效显示区域行地址

.v_addr (v_addr ),//数据有效显示区域场地址

.vga_blk (vga_blk ),

.data_dis (data_dis )//

);

vga_ctrl u_vga_ctrl(

.clk (vga_clk ),//VGA时钟25.2MHz

.rst_n (rst_n ),//复位信号

.data_dis (data_dis ),//

.h_addr (h_addr ),//数据有效显示区域行地址

.v_addr (v_addr ),//数据有效显示区域场地址

.hsync (hsync ),//

.vsync (vsync ),//

.vga_r (vga_r ),//

.vga_g (vga_g ),//

.vga_b (vga_b ), //

.vga_blk (vga_blk )

);

endmodule

彩条输出

module data_gen(

input wire clk ,//VGA时钟25.2MHz

input wire rst_n ,//复位信号

input wire [10:00] h_addr ,//数据有效显示区域行地址

input wire [10:00] v_addr ,//数据有效显示区域场地址

input wire vga_blk ,

output reg [23:00] data_dis //

);

parameter

BLACK = 24'H000000, RED = 24'HFF0000,

GREEN = 24'H00FF00, BLUE = 24'H0000FF,

YELLOW = 24'HFFFF00, SKY_BULE = 24'H00FFFF,

PURPLE = 24'HFF00FF, GRAY = 24'HC0C0C0,

WHITE = 24'HFFFFFF;

parameter

h_vld = 640,

v_vld = 480,

pic_w =272,

pic_h =16,

x_start = (h_vld - pic_w >>1 ) -1,

y_start = (v_vld - pic_h >>1 ) -1;

reg [10:00] pix_x,pix_y;

reg [ 271:0 ] char_line[ 15:0 ]; //272*16

reg [15:00] rom_address;

//彩条

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

data_dis <= WHITE;

end

else begin

case (h_addr)

0 : data_dis <= BLACK ;

80 : data_dis <= RED ;

160 : data_dis <= GREEN ;

240 : data_dis <= BLUE ;

320 : data_dis <= YELLOW ;

400 : data_dis <= SKY_BULE;

480 : data_dis <= PURPLE ;

560 : data_dis <= GRAY ;

default : data_dis <= data_dis;

endcase

end

end

endmodule

配置 USB-Blaster 驱动:https://blog.csdn.net/ssj925319/article/details/115333028

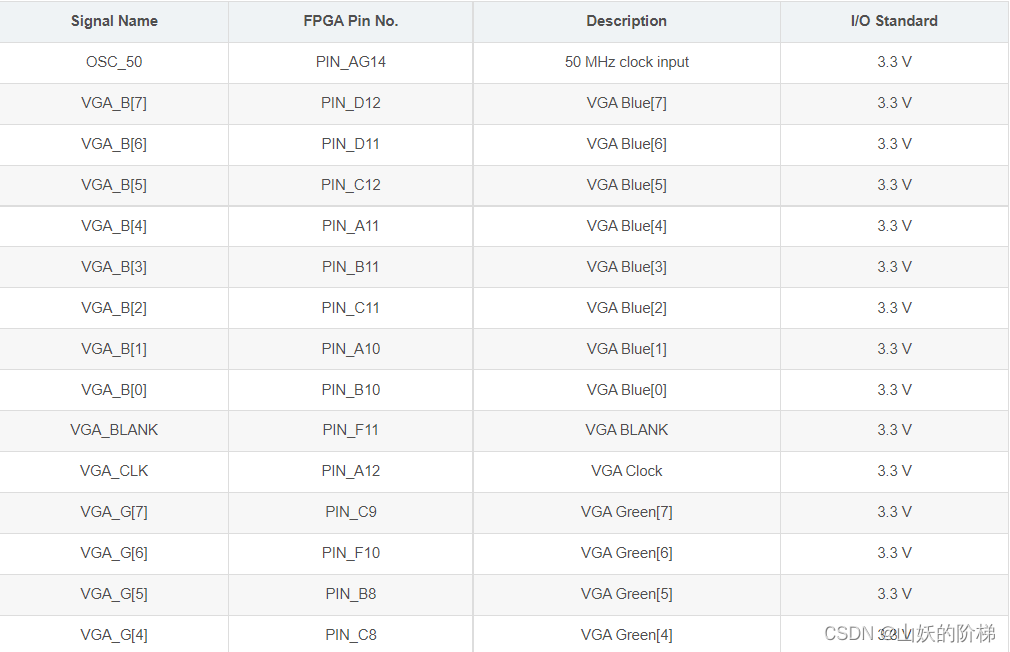

引脚配置

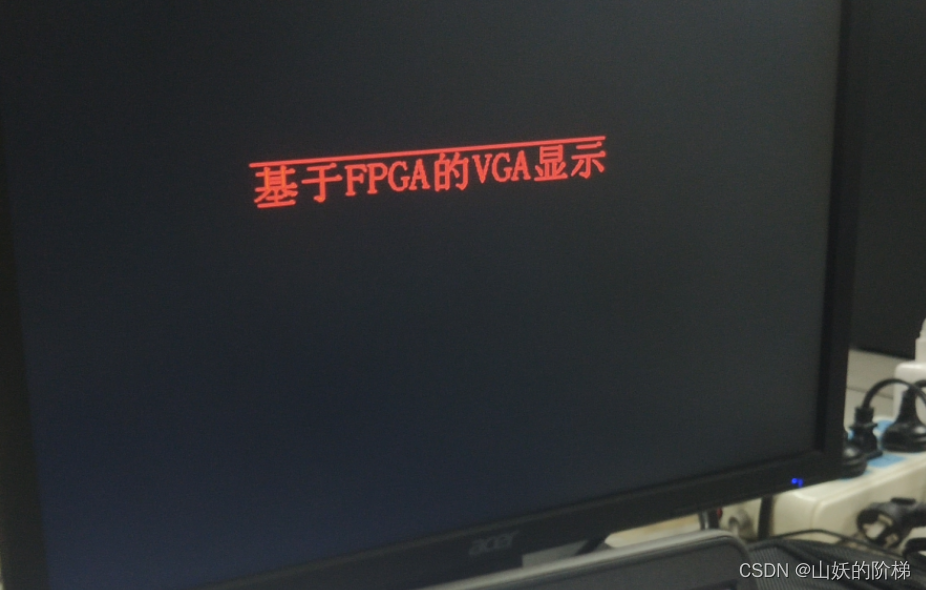

烧录运行结果

修改分辨率为800*600 时钟改为40MHz:

三、VGA显示字符

module VGA_test(

OSC_50, //原CLK2_50时钟信号

VGA_CLK, //VGA自时钟

VGA_HS, //行同步信号

VGA_VS, //场同步信号

VGA_BLANK, //复合空白信号控制信号 当BLANK为低电平时模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略

VGA_SYNC, //符合同步控制信号 行时序和场时序都要产生同步脉冲

VGA_R, //VGA绿色

VGA_B, //VGA蓝色

VGA_G); //VGA绿色

input OSC_50; //外部时钟信号CLK2_50

output VGA_CLK,VGA_HS,VGA_VS,VGA_BLANK,VGA_SYNC;

output [7:0] VGA_R,VGA_B,VGA_G;

parameter H_FRONT = 16; //行同步前沿信号周期长

parameter H_SYNC = 96; //行同步信号周期长

parameter H_BACK = 48; //行同步后沿信号周期长

parameter H_ACT = 640; //行显示周期长

parameter H_BLANK = H_FRONT+H_SYNC+H_BACK; //行空白信号总周期长

parameter H_TOTAL = H_FRONT+H_SYNC+H_BACK+H_ACT; //行总周期长耗时

parameter V_FRONT = 11; //场同步前沿信号周期长

parameter V_SYNC = 2; //场同步信号周期长

parameter V_BACK = 31; //场同步后沿信号周期长

parameter V_ACT = 480; //场显示周期长

parameter V_BLANK = V_FRONT+V_SYNC+V_BACK; //场空白信号总周期长

parameter V_TOTAL = V_FRONT+V_SYNC+V_BACK+V_ACT; //场总周期长耗时

reg [10:0] H_Cont; //行周期计数器

reg [10:0] V_Cont; //场周期计数器

wire [7:0] VGA_R; //VGA红色控制线

wire [7:0] VGA_G; //VGA绿色控制线

wire [7:0] VGA_B; //VGA蓝色控制线

reg VGA_HS;

reg VGA_VS;

reg [10:0] X; //当前行第几个像素点

reg [10:0] Y; //当前场第几行

reg CLK_25;

[email protected](posedge OSC_50)

begin

CLK_25=~CLK_25; //时钟

end

assign VGA_SYNC = 1'b0; //同步信号低电平 assign VGA_BLANK = ~((H_Cont<H_BLANK)||(V_Cont<V_BLANK)); //当行计数器小于行空白总长或场计数器小于场空白总长时,空白信号低电平 assign VGA_CLK = ~CLK_to_DAC; //VGA时钟等于CLK_25取反 assign CLK_to_DAC = CLK_25; [email protected](posedge CLK_to_DAC) begin if(H_Cont<H_TOTAL) //如果行计数器小于行总时长 H_Cont<=H_Cont+1'b1; //行计数器+1

else H_Cont<=0; //否则行计数器清零

if(H_Cont==H_FRONT-1) //如果行计数器等于行前沿空白时间-1

VGA_HS<=1'b0; //行同步信号置0 if(H_Cont==H_FRONT+H_SYNC-1) //如果行计数器等于行前沿+行同步-1 VGA_HS<=1'b1; //行同步信号置1

if(H_Cont>=H_BLANK) //如果行计数器大于等于行空白总时长

X<=H_Cont-H_BLANK; //X等于行计数器-行空白总时长 (X为当前行第几个像素点)

else X<=0; //否则X为0

end

[email protected](posedge VGA_HS)

begin

if(V_Cont<V_TOTAL) //如果场计数器小于行总时长

V_Cont<=V_Cont+1'b1; //场计数器+1 else V_Cont<=0; //否则场计数器清零 if(V_Cont==V_FRONT-1) //如果场计数器等于场前沿空白时间-1 VGA_VS<=1'b0; //场同步信号置0

if(V_Cont==V_FRONT+V_SYNC-1) //如果场计数器等于行前沿+场同步-1

VGA_VS<=1'b1; //场同步信号置1 if(V_Cont>=V_BLANK) //如果场计数器大于等于场空白总时长 Y<=V_Cont-V_BLANK; //Y等于场计数器-场空白总时长 (Y为当前场第几行) else Y<=0; //否则Y为0 end reg valid_yr; [email protected](posedge CLK_to_DAC) if(V_Cont == 10'd32) //场计数器=32时

valid_yr<=1'b1; //行输入激活 else if(V_Cont==10'd512) //场计数器=512时

valid_yr<=1'b0; //行输入冻结 wire valid_y=valid_yr; //连线 reg valid_r; [email protected](posedge CLK_to_DAC) if((H_Cont == 10'd32)&&valid_y) //行计数器=32时

valid_r<=1'b1; //像素输入激活 else if((H_Cont==10'd512)&&valid_y) //行计数器=512时

valid_r<=1'b0; //像素输入冻结 wire valid = valid_r; //连线 wire[10:0] x_dis; //像素显示控制信号 wire[10:0] y_dis; //行显示控制信号 assign x_dis=X; //连线X assign y_dis=Y; //连线Y parameter //点阵字模:每一行char_lineXX是显示的一行,共272列 char_line00=272'hFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF, //第1行

char_line01=272'h00000000000000000000000000000000000000000000000000000000000000000000, //第2行 char_line02=272'h00400C0000000000000000000000000000C008000000000000000000000000000000, //第3行

char_line03=272'h00700E0000000180000000000000000000E00C0000000000000000800180000000C0, //第4行 char_line04=272'h00600C00000003C0000000000000000000C01C0000000000000000FFFF80000001E0, //第5行

char_line05=272'h00600C3003FFFC000000000000000080008018000000000000800080018003FFFE00, //第6行 char_line06=272'h1FFFFFF8000180007FFE7FF003C80380008018007C1F03C803800080018000000000, //第7行

char_line07=272'h00600C0000018000180E18180E3803800104301018040E3803800080018000000000, //第8行 char_line08=272'h00600C00000180001802180C080803800FFE30381804080803800080018000000000, //第9行

char_line09=272'h00600C000001800018031806180802800C0C7FF818041808028000FFFF8000000000, //第10行 char_line0a=272'h007FFC000001800018011806300406C00C0C60300C08300406C00080018000000000, //第11行

char_line0b=272'h00600C000001800018001806300404C00C0CC0300C08300404C00080018000000018, //第12行 char_line0c=272'h00600C000001801018081806200004C00C0C80300C08200004C0008001800000003C, //第13行

char_line0d=272'h007FFC000001803818081806600004C00C0D00300C08600004C0008001803FFFFFFE, //第14行 char_line0e=272'h00600C003FFFFFFC1818180C60000C600C0D4030061060000C6000FFFF8000018000, //第15行

char_line0f=272'h00600C10000180001FF81818600008600C0E20300610600008600080010000018000, //第16行 char_line10=272'h00600C380001800018181FF0600008600C0C10300610600008600008200000418000, //第17行

char_line11=272'h3FFFFFFC0001800018081800600008600FFC1830073060000860000C382000718800, //第18行 char_line12=272'h003208000001800018081800603F1FF00C0C18300320603F1FF0080C307000E18600, //第19行

char_line13=272'h00618C000001800018001800600C10300C0C0C300320600C10300C0C307000C18300, //第20行 char_line14=272'h00C106000001800018001800600C10300C0C08300320600C1030060C30C001818180, //第21行

char_line15=272'h018101C00001800018001800300C10300C0C003001C0300C1030030C30C0038180C0, //第22行 char_line16=272'h030104FC0001800018001800300C30300C0C003001C0300C3030038C318003018060, //第23行

char_line17=272'h0C010E380001800018001800180C20180C0C003001C0180C2018018C330006018070, //第24行 char_line18=272'h187FF0000001800018001800180C20180C0C003001C0180C2018018C36000C018038, //第25行

char_line19=272'h6001000000018000180018000C1060180C0C003000800C106018008C380018018038, //第26行 char_line1a=272'h00010000000180007E007E0003E0F83E0C0C0030008003E0F83E000C301010018010, //第27行

char_line1b=272'h00010000003F800000000000000000000FFC0C60000000000000000C303820738000, //第28行 char_line1c=272'h00010060000F800000000000000000000C0C03E00000000000001FFFFFFC001F8000, //第29行

char_line1d=272'h1FFFFFF00007000000000000000000000C0801C00000000000000000000000070000, //第30行 char_line1e=272'h00000000000000000000000000000000000000800000000000000000000000020000, //第31行

char_line1f=272'h00000000000000000000000000000000000000000000000000000000000000000000; //第32行 reg[8:0] char_bit; [email protected](posedge CLK_to_DAC) if(X==10'd144)char_bit<=9'd272; //当显示到144像素时准备开始输出图像数据 else if(X>10'd144&&X<10'd416) //左边距屏幕144像素到416像素时 416=144+272(图像宽度) char_bit<=char_bit-1'b1; //倒着输出图像信息

reg[29:0] vga_rgb; //定义颜色缓存

[email protected](posedge CLK_to_DAC)

if(X>10'd144&&X<10'd416) //X控制图像的横向显示边界:左边距屏幕左边144像素 右边界距屏幕左边界416像素

begin case(Y) //Y控制图像的纵向显示边界:从距离屏幕顶部160像素开始显示第一行数据

10'd160: if(char_line00[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; //如果该行有数据 则颜色为红色

else vga_rgb<=30'b0000000000_0000000000_0000000000; //否则为黑色 10'd162:

if(char_line01[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd163: if(char_line02[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd164:

if(char_line03[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd165: if(char_line04[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd166:

if(char_line05[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd167: if(char_line06[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd168:

if(char_line07[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd169: if(char_line08[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd170:

if(char_line09[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd171: if(char_line0a[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd172:

if(char_line0b[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd173: if(char_line0c[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd174:

if(char_line0d[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd175: if(char_line0e[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd176:

if(char_line0f[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd177: if(char_line10[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd178:

if(char_line11[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd179: if(char_line12[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd180:

if(char_line13[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd181: if(char_line14[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd182:

if(char_line15[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd183: if(char_line16[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd184:

if(char_line17[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd185: if(char_line18[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd186:

if(char_line19[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd187: if(char_line1a[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd188:

if(char_line1b[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd189: if(char_line1c[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd190:

if(char_line1d[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd191: if(char_line1e[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd192:

if(char_line1f[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000;

default:vga_rgb<=30'h0000000000; //默认颜色黑色 endcase end else vga_rgb<=30'h000000000; //否则黑色

assign VGA_R=vga_rgb[23:16];

assign VGA_G=vga_rgb[15:8];

assign VGA_B=vga_rgb[7:0];

endmodule

烧录运行

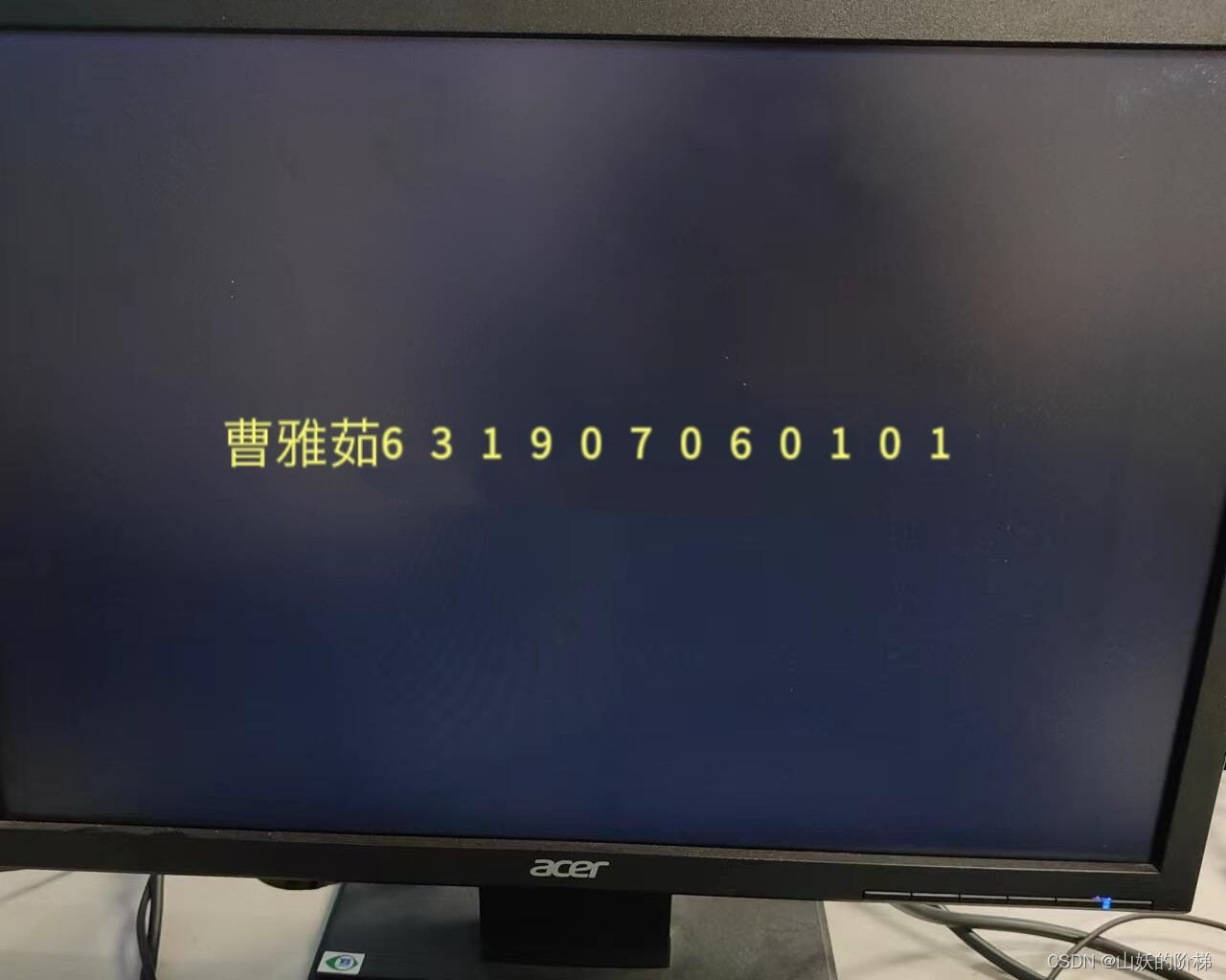

四、自定义字符显示

//初始化显示文字

[email protected]( posedge clk or negedge rst_n ) begin

if ( !rst_n ) begin

char_line[ 0 ] = 272'h010010010000000000000000000000000000000000000000000000000000; char_line[ 1 ] = 272'h010021000804000000000000000000000000000000000000000000000000;

char_line[ 2 ] = 272'h028011fc7f78000000000000000000000000000000000000000000000000; char_line[ 3 ] = 272'h04401200004018003c000800380018007e0018001800180008003c007e00;

char_line[ 4 ] = 272'h082085f82240240042003800440024004200240024002400380042004200; char_line[ 5 ] = 272'h101041081440400042000800420042000400420040004200080042000400;

char_line[ 6 ] = 272'h2fe84948ff7e400002000800420042000400420040004200080042000400; char_line[ 7 ] = 272'hc106092808485c000400080042004200080042005c004200080002000800;

char_line[ 8 ] = 272'h010017fe0848620018000800460042000800420062004200080004000800; char_line[ 9 ] = 272'h3ff811087f484200040008003a0042001000420042004200080008001000;

char_line[ 10 ] = 272'h0100e2480848420002000800020042001000420042004200080010001000; char_line[ 11 ] = 272'h111022282a48420042000800020042001000420042004200080020001000;

char_line[ 12 ] = 272'h110823fc4948220042000800240024001000240022002400080042001000; char_line[ 13 ] = 272'h2104200888881c003c003e0018001800100018001c0018003e007e001000;

char_line[ 14 ] = 272'h450420502888000000000000000000000000000000000000000000000000; char_line[ 15 ] = 272'h020000201108000000000000000000000000000000000000000000000000;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

pix_x <= 11'd0; pix_y <= 11'd0;

end

else if ((h_addr >= x_start && h_addr < x_start +pic_w) &&(v_addr >= y_start && v_addr < y_start + pic_h)) begin

pix_x <= h_addr - x_start;

pix_y <= v_addr - y_start;

end

else begin

pix_x <= 11'h7ff; pix_y <= 11'h7ff;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

data_dis <= BLACK;

end

else if (pix_x != 11'h7FF && pix_y != 11'h7FF) begin

if(char_line[pix_y][271 - pix_x]== 1'b1)begin

data_dis <= WHITE;

end

else begin

data_dis <= BLUE;

end

end

else begin

data_dis <= data_dis;

end

end

五、总结

参考链接

https://blog.csdn.net/qq_61682562/article/details/125171347?spm=1001.2014.3001.5502

https://wenku.baidu.com/view/cea418180a12a21614791711cc7931b765ce7bb7.html

https://wenku.baidu.com/view/df4ad0ccadaad1f34693daef5ef7ba0d4a736dea.html

边栏推荐

- Introduction to the extension implementation of SAP Spartacus checkout process

- jmeter 函数助手 — — 随机值、随机字符串、 固定值随机提取

- Bbox regression loss function in target detection -l2, smooth L1, IOU, giou, Diou, ciou, focal eiou, alpha IOU, Siou

- Classic questions about data storage

- Red hat install kernel header file

- Financial risk control practice - decision tree rule mining template

- Introduction to yarn (one article is enough)

- SubGHz, LoRaWAN, NB-IoT, 物联网

- 【GNN】图解GNN: A gentle introduction(含视频)

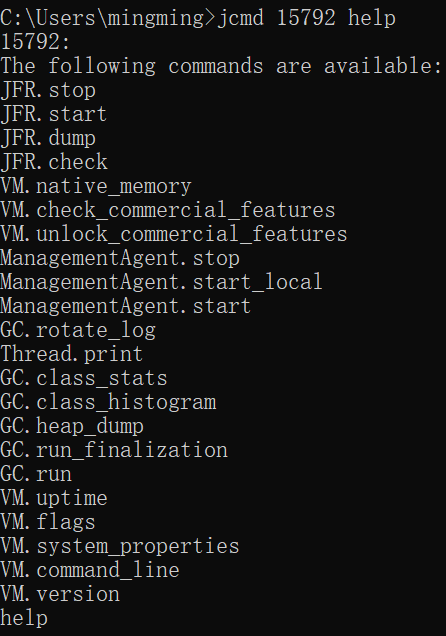

- jvm命令之 jcmd:多功能命令行

猜你喜欢

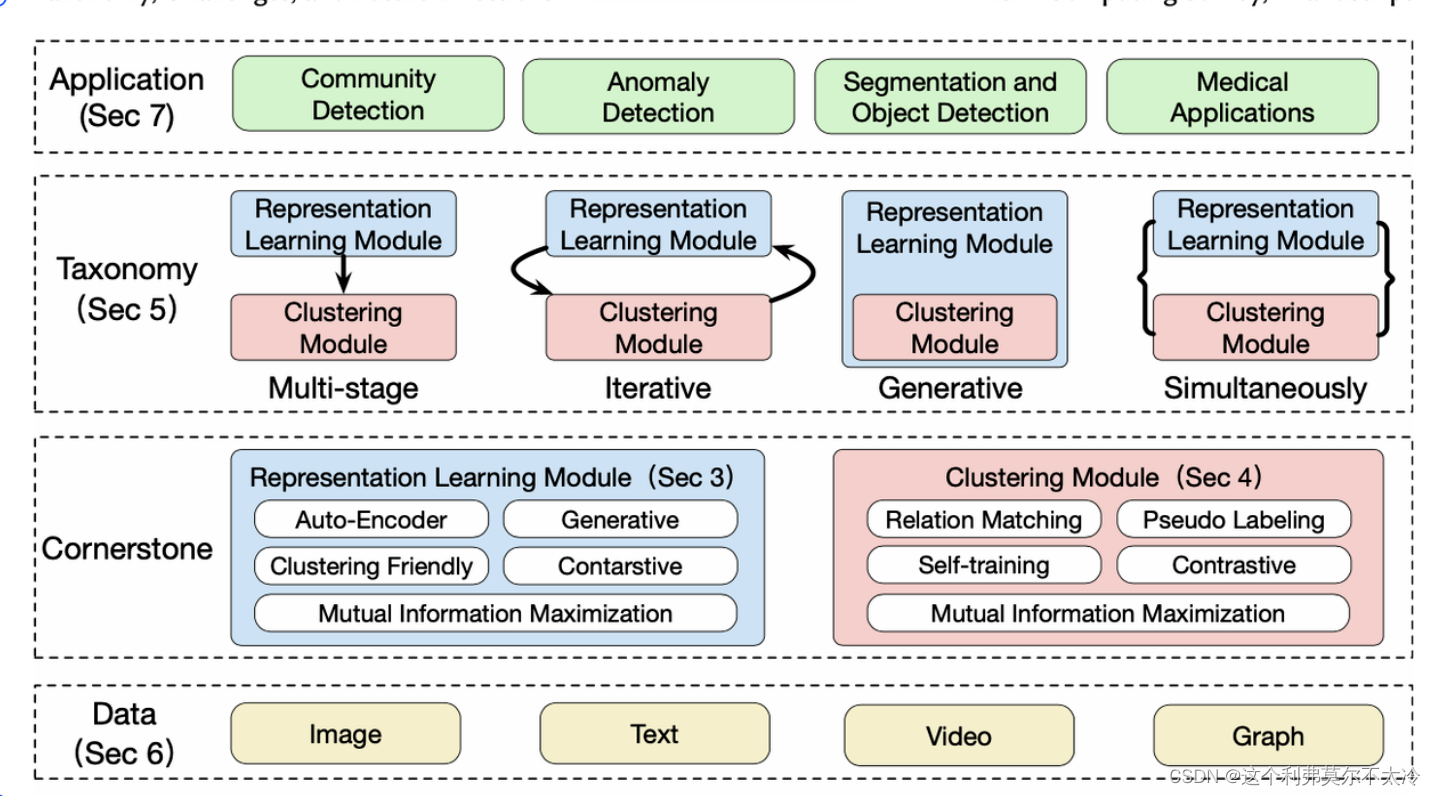

Deep clustering: joint optimization of depth representation learning and clustering

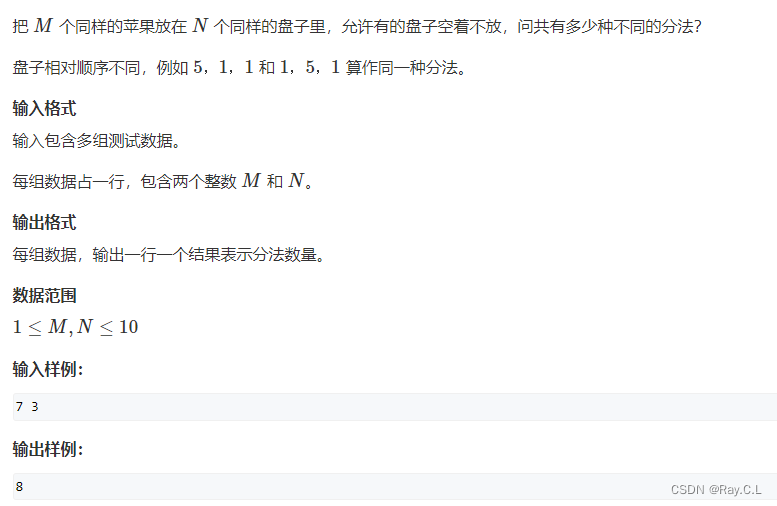

3428. 放苹果

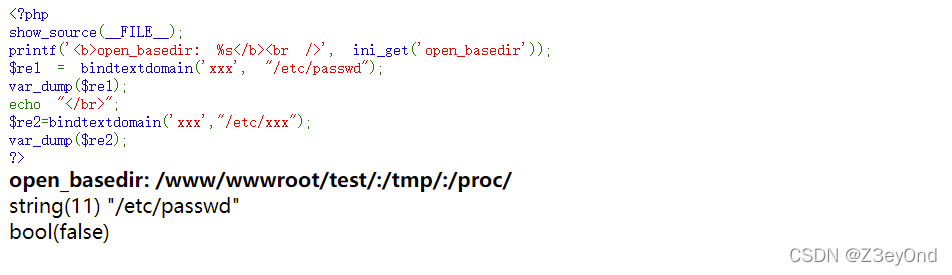

绕过open_basedir

Convert numbers to string strings (to_string()) convert strings to int sharp tools stoi();

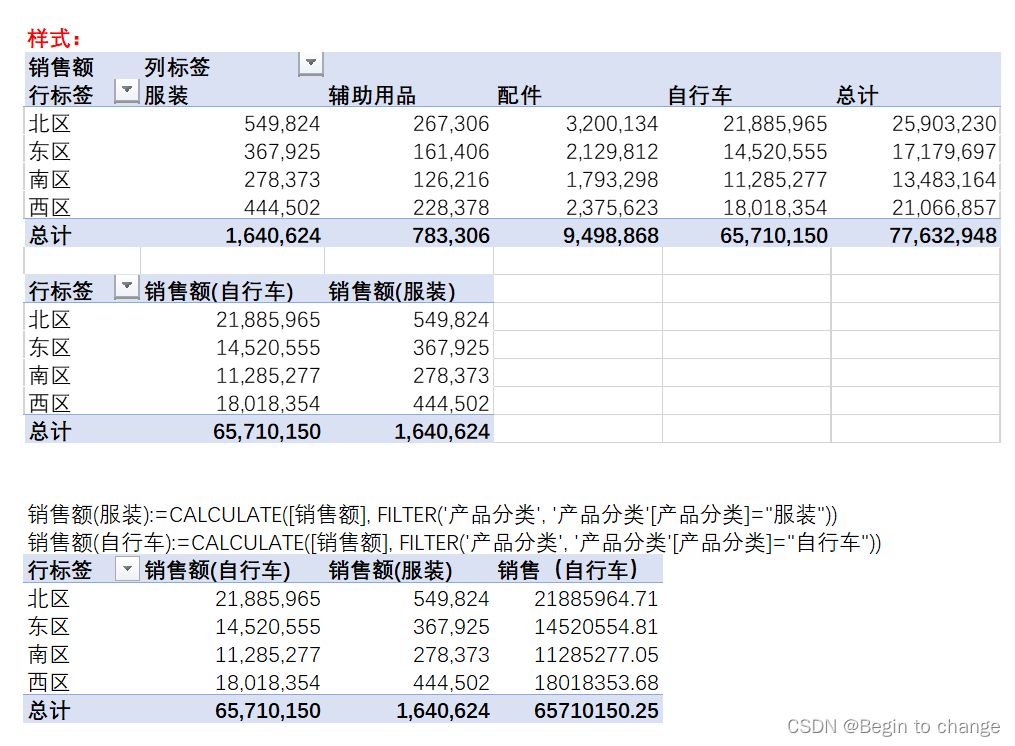

PowerPivot - DAX (function)

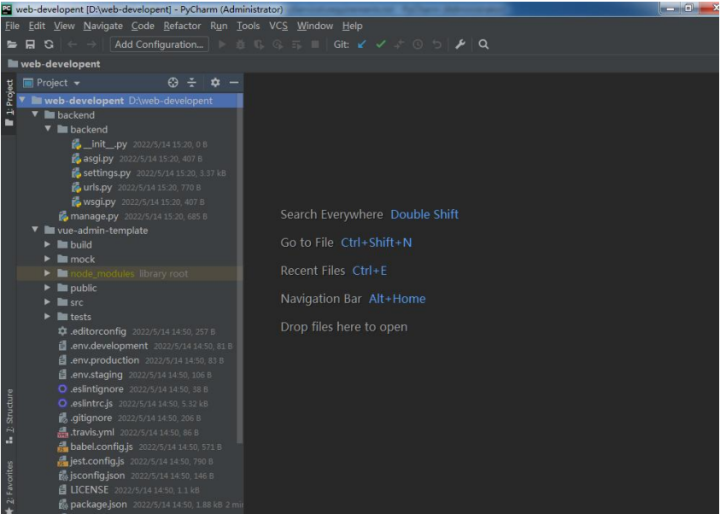

测试开发基础,教你做一个完整功能的Web平台之环境准备

Interview skills of software testing

Jstack of JVM command: print thread snapshots in JVM

外设驱动库开发笔记43:GPIO模拟SPI驱动

jvm命令之 jcmd:多功能命令行

随机推荐

PowerPivot - DAX (function)

Apple CMS V10 template /mxone Pro adaptive film and television website template

对称的二叉树【树的遍历】

Nvisual network visualization

You don't know the complete collection of recruitment slang of Internet companies

高并发大流量秒杀方案思路

苹果cms V10模板/MXone Pro自适应影视电影网站模板

JVM命令之 jstat:查看JVM統計信息

[云原生]微服务架构是什么?

如何在Touch Designer 2022版中设置解决Leap Motion不识别的问题?

一名普通学生的大一总结【不知我等是愚是狂,唯知一路向前奔驰】

PTA ladder game exercise set l2-002 linked list de duplication

Go语学习笔记 - gorm使用 - 原生sql、命名参数、Rows、ToSQL | Web框架Gin(九)

MySQL performance_ Schema common performance diagnosis query

yarn入门(一篇就够了)

为不同类型设备构建应用的三大更新 | 2022 I/O 重点回顾

Storage of dental stem cells (to be continued)

Deep clustering: joint optimization of depth representation learning and clustering

Career experience feedback to novice programmers

如果不知道这4种缓存模式,敢说懂缓存吗?