当前位置:网站首页>I2C read / write process

I2C read / write process

2022-06-11 23:27:00 【Do you want to buy vegetables!】

I2C Data communication consists of data lines (SDA) And a clock line (SCL) form First pair I2C initialization : Main mode 、 Interrupt vector IRQ interrupt 、 Bus rate Data reading and writing process :

1、 The main equipment sends a start signal (Start)

Start signal (Start): Clock line (SCL) During high level , cable (SDA) From high to low , It is a start signal .

2、 The main device sends out 1 Bytes of slave address information

The lowest bit is the read / write control code (0 For writing ,1 For reading ), high 7 Bit is the slave address code .

Such as AT24C256 Address :

3、 Send an approval signal from the device

Answer signal (Ack): That is, the approval signal , There are two cases :

(a)、 The master device writes to the slave device , Every time you write correctly 1 Bytes of data , The slave device will connect the data line in the next clock cycle (SDA) Pull it down , It is a reply signal .

(b)、 The master device reads the slave device , After each correct reading 1 Bytes of data , The master device will connect the data line in the next clock cycle (SDA) Pull it down , It is a reply signal . notes : When reading from a slave device , The master device does not send a response signal after the last byte of data is received , Instead, it sends an end signal directly .

4、 The master device starts reading and writing to the slave device

If it is Read operations , Then every read 1 byte , The master device will send a reply signal (Ack) To the slave device , If it is Write operations , Then every time 1 byte , The slave device will send a reply signal (Ack) To main equipment .

5、 The main equipment sends an end signal (Stop)

Clock line (SCL) During high level , cable (SDA) From low to high , It is an end signal . in other words ,I2C The bus is in the communication process , All data read and write operations must be on the clock line (SCL) For low level , And on the clock line (SCL) Data lines must be maintained for high power levels (SDA) Signal stability , Anything that happens on the clock line (SCL) Data line during high level (SDA) All level changes on the are considered as start or end signals .

边栏推荐

- [Day8 literature extensive reading] space and time in the child's mind: evidence for a cross dimensional symmetry

- The top ten trends of 2022 industrial Internet security was officially released

- Data visualization platform based on template configuration

- 2022年安全员-A证考题模拟考试平台操作

- Google搜索为什么不能无限分页?

- A new product with advanced product power, the new third generation Roewe rx5 blind subscription is opened

- Small program startup performance optimization practice

- Lake Shore—SuperVariTemp 低温恒温器

- Common problems of Converged Communication published in February | Yunxin small class

- The latest "capsule Network Overview" paper of imperial technology, etc., 29 pages of PDF, expounds the concept, method and application of capsule

猜你喜欢

One to one correspondence of multiple schematic diagrams and PCB diagrams under Altium designer project

【Day11-12 文献精读】On magnitudes in memory: An internal clock account of space-time interaction

2022高压电工考试题模拟考试题库及在线模拟考试

商品热销排行【项目 商城】

The top ten trends of 2022 industrial Internet security was officially released

Altium designer工程下多个原理图和PCB图的一一对应

Application of Lora wireless communication module Lora technology in smart home light control

2022 low voltage electrician certificate and online simulation examination

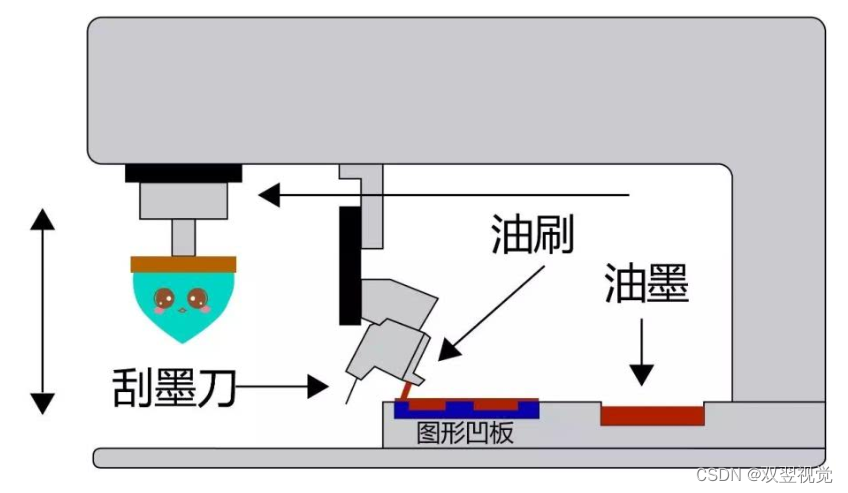

Pad printing process flow and application precautions

Jetpack架构组件学习(3)——Activity Results API使用

随机推荐

Jetpack架构组件学习(3)——Activity Results API使用

Queue (C language)

JS to add an attribute to an array object

2022 safety officer-b certificate theoretical question bank and simulation test

How to do investment analysis in the real estate industry? This article tells you

Lake Shore—SuperTran 连续流低温恒温器系统

Data visualization platform based on template configuration

[day13-14 intensive literature reading] cross dimensional magnetic interactions arise from memory interference

Teacher lihongyi, NTU -- tips for DNN regulation

The second bullet of in-depth dialogue with the container service ack distribution: how to build a hybrid cloud unified network plane with the help of hybridnet

04 automatic learning rate - learning notes - lihongyi's in-depth learning 2021

Google搜索為什麼不能無限分頁?

Pad printing process flow and application precautions

【Day1/5 文献精读】Speed Constancy or Only Slowness: What Drives the Kappa Effect

Altium designer工程下多个原理图和PCB图的一一对应

How to construct PostgreSQL error codes

Introduction to Solr Basics

The top ten trends of 2022 industrial Internet security was officially released

Simulated examination question bank and simulated examination of 2022 crane driver (limited to bridge crane)

[Day2 intensive literature reading] time in the mind: using space to think about time