当前位置:网站首页>verilog REG 寄存器、向量、整数、实数、时间寄存器

verilog REG 寄存器、向量、整数、实数、时间寄存器

2022-07-02 03:02:00 【嗒曦】

寄存器(reg)

寄存器(reg)用来表示存储单元,它会保持数据原有的值,直到被改写。声明举例如下:

实例

reg clk_temp;

reg flag1, flag2 ;

例如在 always 块中,寄存器可能被综合成边沿触发器,在组合逻辑中可能被综合成 wire 型变量。寄存器不需要驱动源,也不一定需要时钟信号。在仿真时,寄存器的值可在任意时刻通过赋值操作进行改写。例如:

实例

reg rstn ;

initial begin

rstn = 1'b0 ;

#100 ;

rstn = 1'b1 ;

end

向量

当位宽大于 1 时,wire 或 reg 即可声明为向量的形式。例如:

实例

reg [3:0] counter ; //声明4bit位宽的寄存器counter

wire [32-1:0] gpio_data; //声明32bit位宽的线型变量gpio_data

wire [8:2] addr ; //声明7bit位宽的线型变量addr,位宽范围为8:2

reg [0:31] data ; //声明32bit位宽的寄存器变量data, 最高有效位为0

对于上面的向量,我们可以指定某一位或若干相邻位,作为其他逻辑使用。例如:

实例

wire [9:0] data_low = data[0:9] ;

addr_temp[3:2] = addr[8:7] + 1'b1 ;

Verilog 支持可变的向量域选择,例如:

实例

reg [31:0] data1 ;

reg [7:0] byte1 [3:0];

integer j ;

[email protected]* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 : j*8];

//把data1[7:0]…data1[31:24]依次赋值给byte1[0][7:0]…byte[3][7:0]

end

end

Verillog 还支持指定 bit 位后固定位宽的向量域选择访问。

- [bit+: width] : 从起始 bit 位开始递增,位宽为 width。

- [bit-: width] : 从起始 bit 位开始递减,位宽为 width。

实例

//下面 2 种赋值是等效的

A = data1[31-: 8] ;

A = data1[31:24] ;

//下面 2 种赋值是等效的

B = data1[0+ : 8] ;

B = data1[0:7] ;

对信号重新进行组合成新的向量时,需要借助大括号。例如:

实例

wire [31:0] temp1, temp2 ;

assign temp1 = {byte1[0][7:0], data1[31:8]}; //数据拼接

assign temp2 = {32{1'b0}}; //赋值32位的数值0

整数,实数,时间寄存器变量

整数,实数,时间等数据类型实际也属于寄存器类型。

整数(integer)

整数类型用关键字 integer 来声明。声明时不用指明位宽,位宽和编译器有关,一般为32 bit。reg 型变量为无符号数,而 integer 型变量为有符号数。例如:

实例

reg [31:0] data1 ;

reg [3:0] byte1 [7:0]; //数组变量,后续介绍

integer j ; //整型变量,用来辅助生成数字电路

[email protected]* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 : j*8];

//把data1[7:0]…data1[31:24]依次赋值给byte1[0][7:0]…byte[3][7:0]

end

end

此例中,integer 信号 j 作为辅助信号,将 data1 的数据依次赋值给数组 byte1。综合后实际电路里并没有 j 这个信号,j 只是辅助生成相应的硬件电路。

实数(real)

实数用关键字 real 来声明,可用十进制或科学计数法来表示。实数声明不能带有范围,默认值为 0。如果将一个实数赋值给一个整数,则只有实数的整数部分会赋值给整数。例如:

实例

real data1 ;

integer temp ;

initial begin

data1 = 2e3 ;

data1 = 3.75 ;

end

initial begin

temp = data1 ; //temp 值的大小为3

end

时间(time)

Verilog 使用特殊的时间寄存器 time 型变量,对仿真时间进行保存。其宽度一般为 64 bit,通过调用系统函数 $time 获取当前仿真时间。例如:

实例

time current_time ;

initial begin

#100 ;

current_time = $time ; //current_time 的大小为 100

end

边栏推荐

- Possible causes of runtime error

- Mongodb base de données non relationnelle

- Mathematics in Sinorgchem: computational geometry

- 2022-2028 global human internal visualization system industry research and trend analysis report

- buu_ re_ crackMe

- Jvm-01 (phased learning)

- 【无标题】

- tarjan2

- Feature query of hypergraph iserver rest Service

- How to develop digital collections? How to develop your own digital collections

猜你喜欢

![[learn C and fly] 4day Chapter 2 program in C language (exercise 2.5 generate power table and factorial table](/img/f4/298f64c4b4f8674eda4e8fb19a976a.png)

[learn C and fly] 4day Chapter 2 program in C language (exercise 2.5 generate power table and factorial table

buu_ re_ crackMe

Pychart creates new projects & loads faster & fonts larger & changes appearance

![[staff] the direction of the symbol stem and the connecting line (the symbol stem faces | the symbol stem below the third line faces upward | the symbol stem above the third line faces downward | the](/img/fe/d97b25f702bbc05f941d08147259e0.jpg)

[staff] the direction of the symbol stem and the connecting line (the symbol stem faces | the symbol stem below the third line faces upward | the symbol stem above the third line faces downward | the

Baohong industry | 6 financial management models at different stages of life

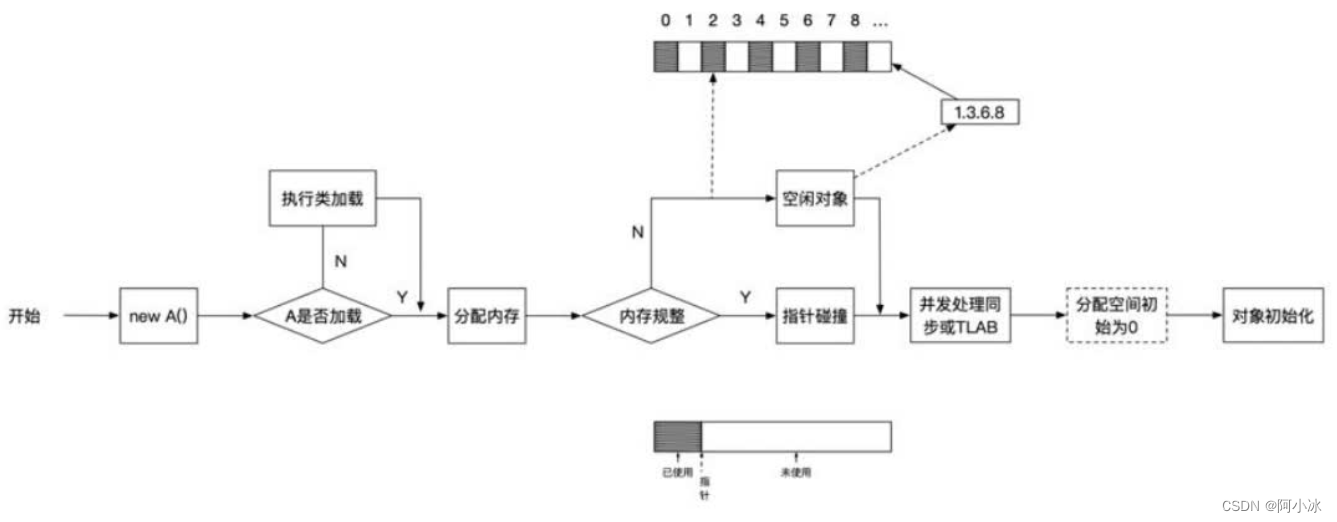

【JVM】创建对象的流程详解

![[staff] restore mark (Introduction to the use of restore mark | example analysis of Metaphone mark and restore mark)](/img/21/7bbf276b01f5a1056a22f5afc0af26.jpg)

[staff] restore mark (Introduction to the use of restore mark | example analysis of Metaphone mark and restore mark)

Just a few simple steps - start playing wechat applet

What kind of good and cost-effective Bluetooth sports headset to buy

Which brand of running headphones is good? How many professional running headphones are recommended

随机推荐

Actual battle of financial risk control - under Feature Engineering

2022-2028 global wood vacuum coating machine industry research and trend analysis report

[road of system analyst] collection of wrong topics in enterprise informatization chapter

Mongodb non relational database

The video number will not be allowed to be put on the shelves of "0 yuan goods" in the live broadcasting room?

Missing numbers from 0 to n-1 (simple difficulty)

[learn C and fly] day 5 chapter 2 program in C language (Exercise 2)

2022-2028 global encryption software industry research and trend analysis report

The number one malware in January 2022: lokibot returned to the list, and emotet returned to the top

Redis set command line operation (intersection, union and difference, random reading, etc.)

STM32__ 05 - PWM controlled DC motor

小米青年工程师,本来只是去打个酱油

Query word weight, search word weight calculation

2022 safety officer-c certificate examination questions and mock examination

How does proxy IP participate in the direct battle between web crawlers and anti crawlers

Xiaomi, a young engineer, was just going to make soy sauce

Render header usage of El table

Delphi xe10.4 installing alphacontrols15.12

结婚后

Mathematical calculation in real mode addressing