当前位置:网站首页>Write your own CPU Chapter 10 - learning notes

Write your own CPU Chapter 10 - learning notes

2022-07-06 09:55:00 【code_ master2020】

This chapter begins with MIPS32 Coprocessor in architecture , It explains the function of coprocessor . because OpenMIPS Plan to implement one of the coprocessors -CP0, therefore 10.2 Section special introduction CP0, And then in 10.3 Section implements coprocessor CP0, Its implementation is a little similar HI、LO Register implementation .10.4 Section describes coprocessor access instructions mfc0、mtc0 The format of 、 effect 、 usage .10.5 Section gives the implementation idea of coprocessor access instructions , And the modification of the system structure .10.6 Section modified OpenMIPS. Realize the coprocessor access instruction , Finally, write the test program , stay ModeSim Simulation verification is carried out in .

10.1 Introduction to coprocessor

The term coprocessor is often used to denote an optional component of a processor , Responsible for processing an extension of the instruction set , It has registers independent of the processor core .MIPS32 The architecture provides up to four coprocessors , Namely CP0~CP3, effect

As of this chapter , our OpenMIPS The processor implements many instructions , But these instructions are used for operations , The actual processor also supports a wide range of other operations , for example : Interrupt handling 、 Provide optional configurations 、 Observe and control the system cache or clock 、 Address translation, etc .MIPS32 Architecture defined coprocessor CP0 The role of is to help achieve the above wide range of operations .CP0 The main work is as follows :

-- To configure CPU Working state : accord with MIPS32 The hardware of the architecture is usually very flexible , You can read / Write one or some internal registers to change some very fundamental CPU characteristic ( Such as : Change the byte order from MSB Turn into LSB Or from LSB Turn into MSB).

-- Cache control : accord with MIPS32 Architecturally CPU Generally, the cache controller is integrated , Used to control 、 read 、 Write cache .

-- Abnormal control : The detection and handling of exceptions are carried out by CP0 Some control registers in to define and control .

-- Storage snap in control : Reasonably control the storage area of the system 、 Management and distribution , It's mainly about MMU、TLB Some configuration of 、 management 、 visit .

-- other : When you want to integrate additional functions into CPU in , But it is not convenient to access as a peripheral , Often in CP0 Add some modules to realize these functions . for example : The clock 、 Time counter 、 Parity error detection, etc .

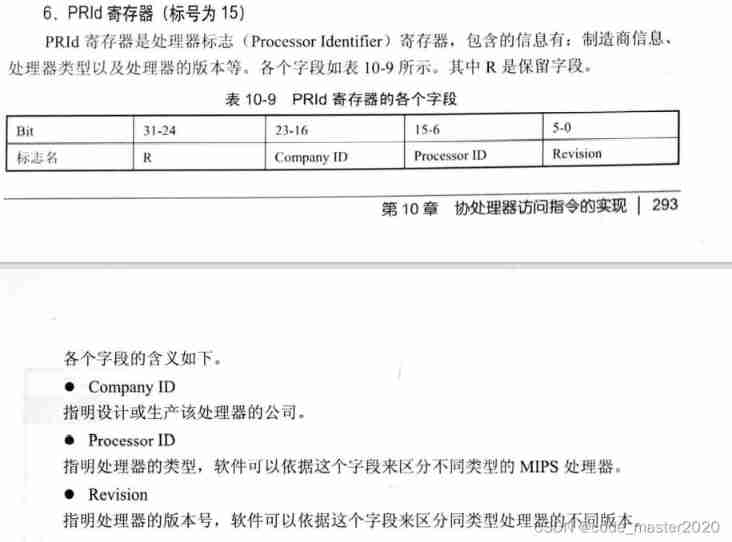

10.2 Coprocessor CP0 Register in

From the table, we can find that many registers are related to cache 、MMU、TLB、 Debugging related , and OpenMIPS The design goal of is a lightweight processor , It is not intended to implement caching 、MMU、TLB、 Debugging and other complex functions .

Let's introduce this in turn 7 Format of registers 、 effect .

1.Count register ( Label for 9)

Count Register is a non-stop counting 32 Bit register , The counting frequency is generally the same as CPU Same clock frequency , When the count reaches 32 When it is the upper limit of unsigned number , From 0 Start counting again .Count Register readable 、 Can write .

2.Compare register ( Label for 11)

Compare A register is a 32 Bit register , And Count Registers together complete the timing interrupt function . When Count The count value of the register and Compare When the values in the register are the same , A timed interrupt will occur . This interruption will remain , Know that data is written Compare register .Compare Register readable 、 Can write

3.Status register ( Label for 12)

Status Register is also a 32 position 、 Can be read 、 Writable registers , Used to control the operation mode of the processor 、 Interrupt enable and diagnostic status

CU3-CU0

Indicates whether the coprocessor is available , Control the coprocessor separately CP3、CP2、CP1、CP0. by 0 when , Indicates that the corresponding coprocessor is unavailable 1 when , Indicates that the corresponding coprocessor is available . about OpenMIPS In terms of processors , Only coprocessors CP0 Therefore, you can set this field to 4'b0001

RP

Indicates whether low power mode is enabled , But whether and how to implement it depends on the specific processor , such as : Some processors can reduce the working frequency 、 Working voltage , To achieve low power consumption ,OpenMIPS The processor does not implement these functions , So this sub paragraph has no effect .

4.Cause register ( Label for 13)

Cause The register mainly records the cause of the latest exception , Also controls software interrupt requests .Cause The fields of the register are shown in the figure , except IP[1:0]、IV and WP, The remaining fields are read-only .

10.3 Coprocessor CP0 The implementation of the

边栏推荐

- Several silly built-in functions about relative path / absolute path operation in CAPL script

- Regular expressions are actually very simple

- Zsh configuration file

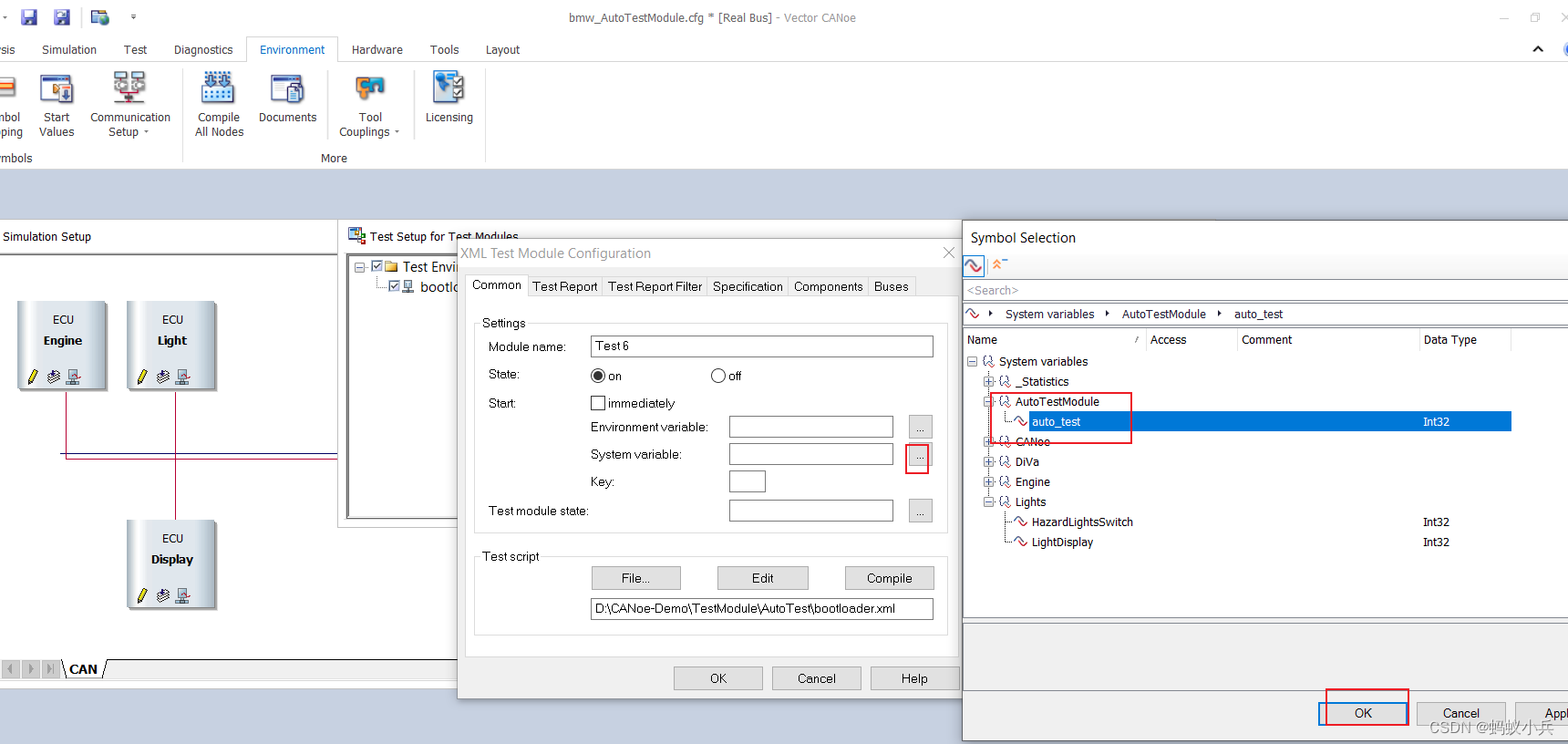

- Control the operation of the test module through the panel in canoe (primary)

- Canoe CAPL file operation directory collection

- 51单片机进修的一些感悟

- Hard core! One configuration center for 8 classes!

- VH6501学习系列文章

- May brush question 01 - array

- Contrôle de l'exécution du module d'essai par panneau dans Canoe (primaire)

猜你喜欢

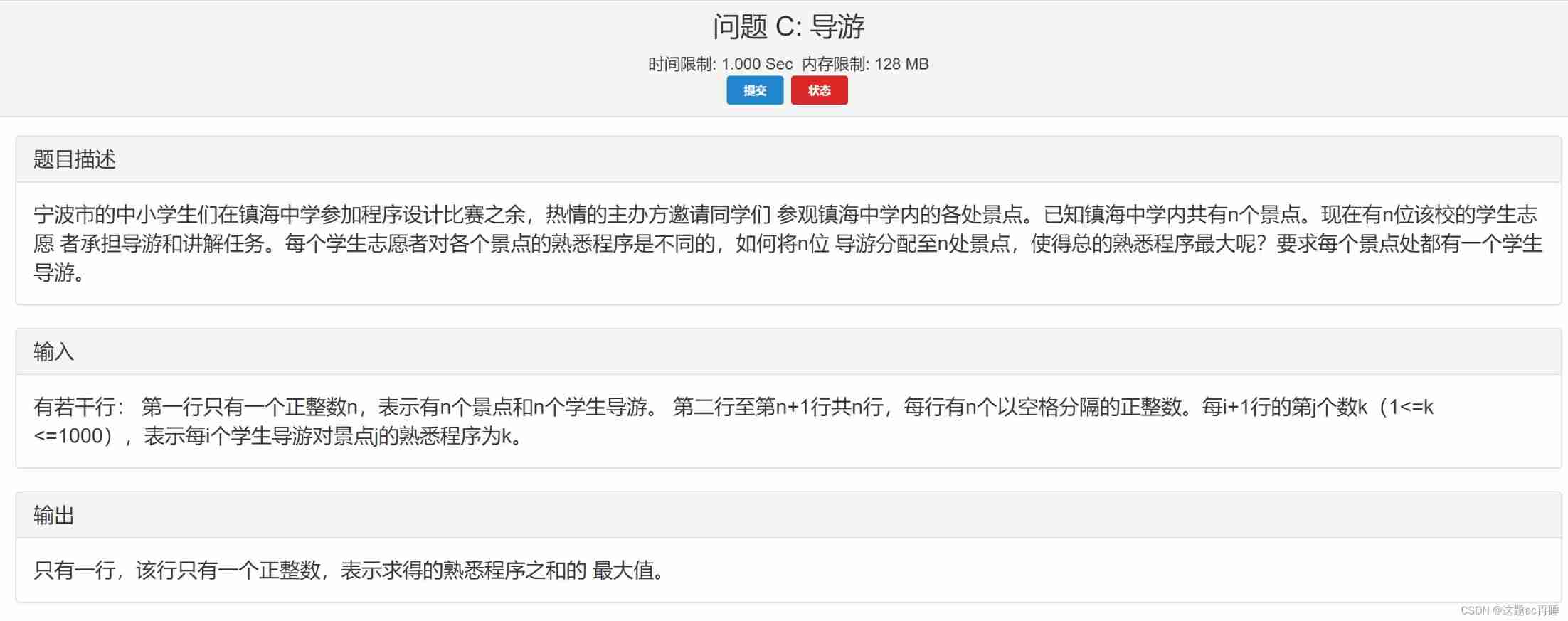

Contest3145 - the 37th game of 2021 freshman individual training match_ C: Tour guide

Listen to my advice and learn according to this embedded curriculum content and curriculum system

一大波開源小抄來襲

Mapreduce实例(四):自然排序

学习单片机对社会的帮助是很大的

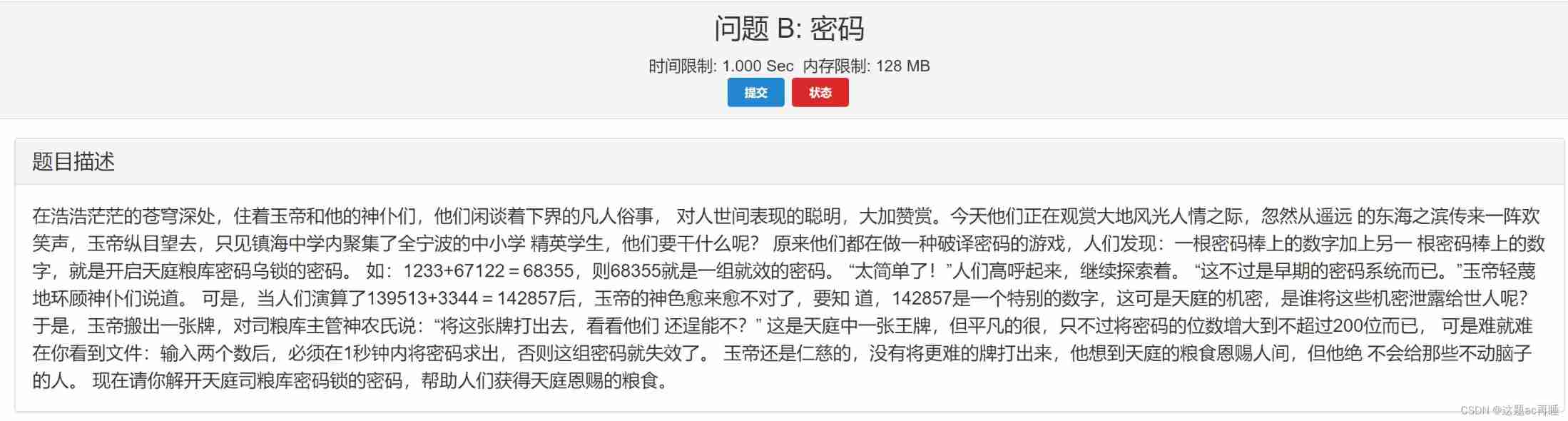

Contest3145 - the 37th game of 2021 freshman individual training match_ B: Password

Defensive C language programming in embedded development

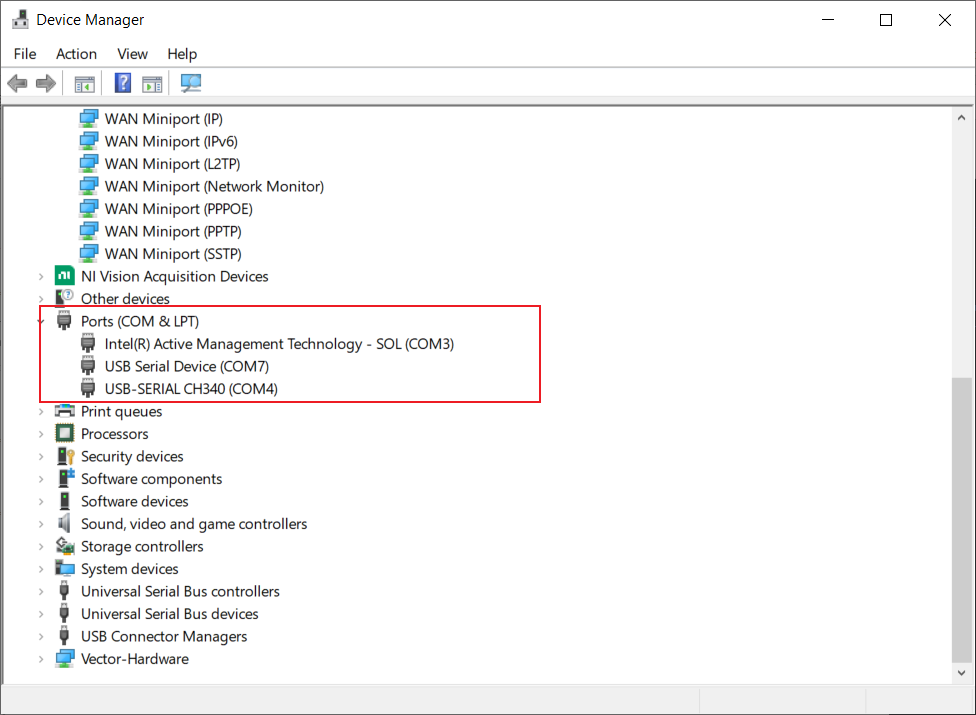

CANoe不能自动识别串口号?那就封装个DLL让它必须行

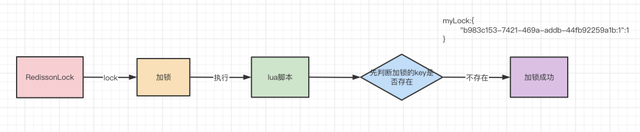

Redis distributed lock implementation redison 15 questions

Contrôle de l'exécution du module d'essai par panneau dans Canoe (primaire)

随机推荐

max-flow min-cut

单片机实现模块化编程:思维+实例+系统教程(实用程度令人发指)

Canoe CAPL file operation directory collection

华南技术栈CNN+Bilstm+Attention

单片机如何从上电复位执行到main函数?

MapReduce instance (IX): reduce end join

Hero League rotation map automatic rotation

C杂讲 文件 初讲

五月刷题01——数组

Function description of shell command parser

May brush question 27 - figure

在CANoe中通過Panel面板控制Test Module 運行(初級)

Research and implementation of hospital management inpatient system based on b/s (attached: source code paper SQL file)

[Yu Yue education] reference materials of power electronics technology of Jiangxi University of science and technology

Automation sequences of canoe simulation functions

Competition vscode Configuration Guide

NLP路线和资源

五月集训总结——来自阿光

Popularization of security knowledge - twelve moves to protect mobile phones from network attacks

五月刷题27——图