当前位置:网站首页>建立时间和保持时间的模型分析

建立时间和保持时间的模型分析

2022-07-06 00:16:00 【傻童:CPU】

建立时间和保持时间的模型分析

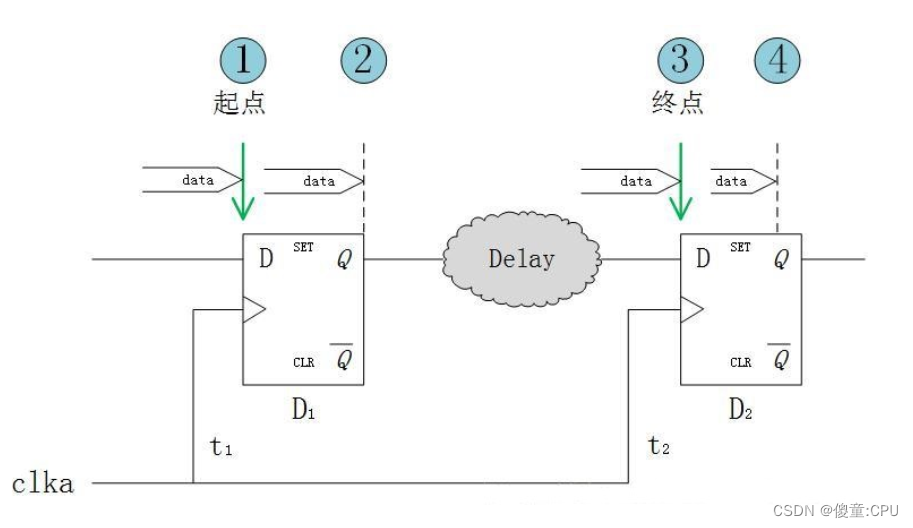

起点是源触发器D1的采样时刻,终点是目的触发器D2的采样时刻,假设起点已经满足了建立时间和保持时间要求,现在分析终点采样时刻是否同样满足要求。

其中

- Tco:数据正确采样后从D端到达Q端的延时,触发器固有属性,不可改变。

- TDelay:D1输出端到D2输入端的组合逻辑延时和布线延时。

- Tsu:触发器的建立时间,触发器的固有属性,不可改变。

- Th:触发器的保持时间,触发器的固有属性,不可改变。

- Tclk:时钟周期。

- t1:假设源时钟为clka,clka到达D1的延时。

- t2:clka到达D2的延时。

触发器的行为:时钟沿到来时采样数据D,将采到的数据寄存下来,并输出到Q端,所有如果没有新的时钟沿到来,则Q端输出的一直是上次采样的数据,每来一个时钟沿,采样一次数据D。

假设clk传输没有延时:则每一个时钟上升沿都会同时到达D1和D2。时间起点,第一个时钟沿D1的采样时刻,时间终点,第二个时钟沿D2的采样时刻。物理起点,D1的输入端,物理终点,D2的输入端。

建立时间满足(关注数据头):第一个时钟沿到来时,数据 data 的头部从起点①开始传输,经过 Tco 到达②,在经过 TDelay

边栏推荐

- FFmpeg学习——核心模块

- Teach you to run uni app with simulator on hbuilderx, conscience teaching!!!

- There is no network after configuring the agent by capturing packets with Fiddler mobile phones

- LeetCode 6005. The minimum operand to make an array an alternating array

- Choose to pay tribute to the spirit behind continuous struggle -- Dialogue will values [Issue 4]

- [gym 102832h] [template] combination lock (bipartite game)

- USB Interface USB protocol

- 关于slmgr命令的那些事

- LeetCode 6004. Get operands of 0

- Priority queue (heap)

猜你喜欢

Tools to improve work efficiency: the idea of SQL batch generation tools

![[designmode] composite mode](/img/9a/25c7628595c6516ac34ba06121e8fa.png)

[designmode] composite mode

Hudi of data Lake (1): introduction to Hudi

云呐|公司固定资产管理系统有哪些?

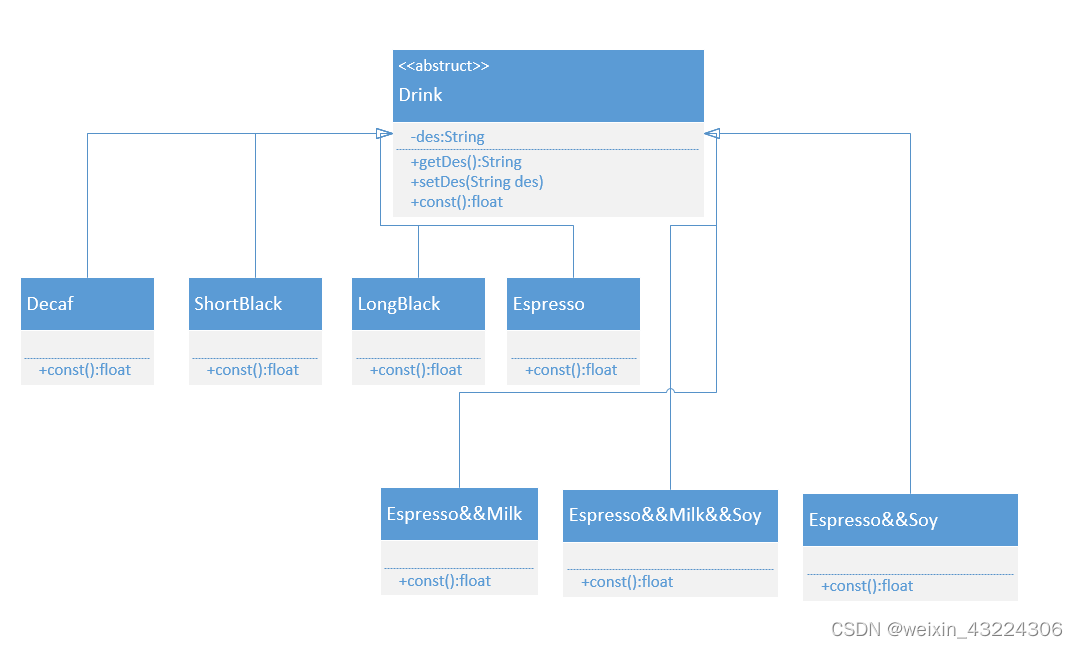

【DesignMode】装饰者模式(Decorator pattern)

Mathematical model Lotka Volterra

QT QPushButton details

Configuring OSPF load sharing for Huawei devices

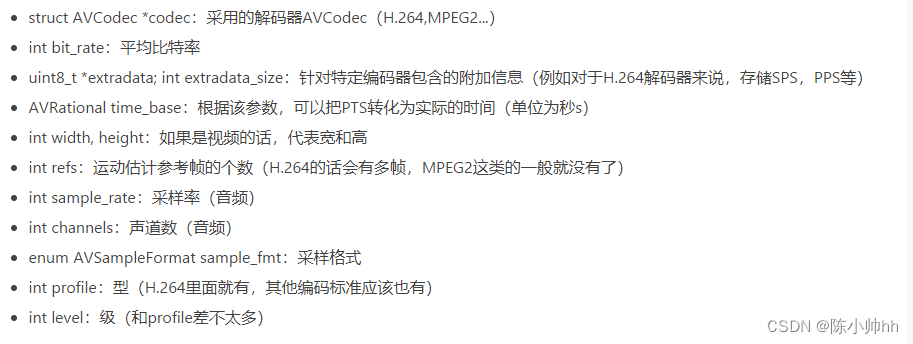

Key structure of ffmpeg -- AVCodecContext

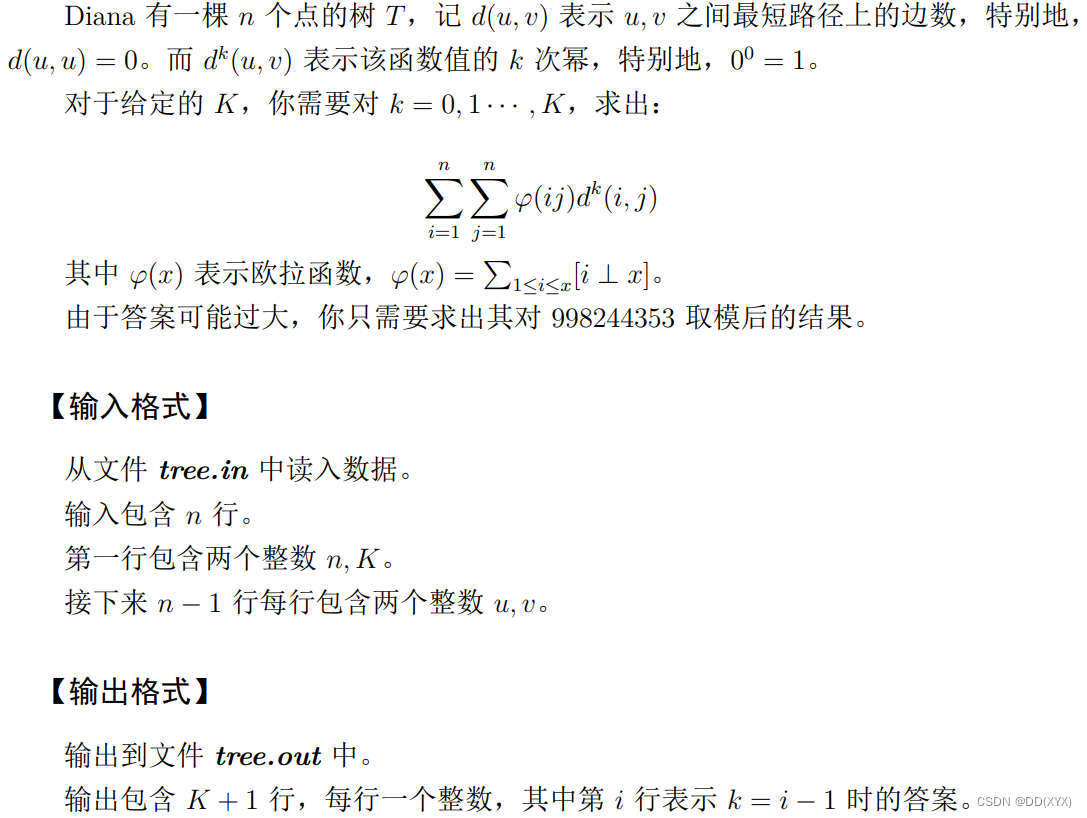

【NOI模拟赛】Anaid 的树(莫比乌斯反演,指数型生成函数,埃氏筛,虚树)

随机推荐

LeetCode 8. String conversion integer (ATOI)

【DesignMode】组合模式(composite mode)

Codeforces round 804 (Div. 2) [competition record]

[Luogu cf487e] tours (square tree) (tree chain dissection) (line segment tree)

VBA fast switching sheet

[designmode] composite mode

AtCoder Beginner Contest 254【VP记录】

How much do you know about the bank deposit business that software test engineers must know?

Effet Doppler (déplacement de fréquence Doppler)

FFMPEG关键结构体——AVFrame

【DesignMode】适配器模式(adapter pattern)

Mathematical model Lotka Volterra

FFmpeg学习——核心模块

LeetCode 6005. The minimum operand to make an array an alternating array

USB Interface USB protocol

Detailed explanation of APP functions of door-to-door appointment service

【二叉搜索树】增删改查功能代码实现

Atcoder beginer contest 258 [competition record]

The global and Chinese markets of dial indicator calipers 2022-2028: Research Report on technology, participants, trends, market size and share

Hudi of data Lake (2): Hudi compilation