当前位置:网站首页>HDL design peripheral tools to reduce errors and help you take off!

HDL design peripheral tools to reduce errors and help you take off!

2022-07-02 19:43:00 【Broken thoughts】

HDL Design peripheral tools , Reduce errors , Help you take off !

HDL Design is the foundation , After designing, it is necessary to use some tools to test your code , For example, simulation tools to verify the function of their own code . Today I will introduce several types of tools , All help HDL Design , These include : Code checker (Lint)、 Code coverage 、 Waveform design 、 State machine design and so on , Let's start !

Simulation

Simulation is HDL Modeling basis , All the hardware circuits that have been modeled need functional simulation first , First of all, let's introduce some simulation tools ( except EDA Simulation software other than those provided by the tool .)

NCVerilog

*http://www.cadence.com/

NC-Verilog by Cadence Company's Verilog Hardware description language simulator (simulator), Can help IC The designer verifies and simulates the design IC The function of . Use NC-Verilog software , Users must use Verilog The syntax of hardware description language is used to describe the circuit to be designed .

This is also the compiled simulator , Its running speed is similar to VCS As fast as , And still keep Verilog-XL Sign off function of . When it comes to gate level simulation , This simulator works well .

VCS

*http://www.synopsys.com/

This is the fastest simulator in the world , It's like NCverilog The same compiler emulator . The simulator is in RTL Faster simulation . Support SystemVerilog.

MPSim

*http://www.axiom-da.com/

Axiom Of MPSim It is an integrated verification environment , Automate the industry's fastest simulator and advanced test bench 、 Assertion based verification 、 Combining debugging with code coverage analysis . It's built-in with Vera Support .

Modelsim

*http://www.model.com/

This is the most popular simulator , It has a very good debugger , Support SystemC、Verilog、VHDL and SystemVerilog.

other

There are many relatively good simulation tools , But in the domestic environment ,VCS and Modelsim It's the majority , It's hard to change habits , So let's briefly introduce some others. See the table below :

Open source tools

There are relatively few open source applications , And it's open source , Poor maintenance and continuity , Also divided into Verilog and VHDL Version to introduce

Verilog edition

It's only recommended here Verilator(http://%20www.synapticad.com/)

VHDL edition

It's only recommended here GHDL

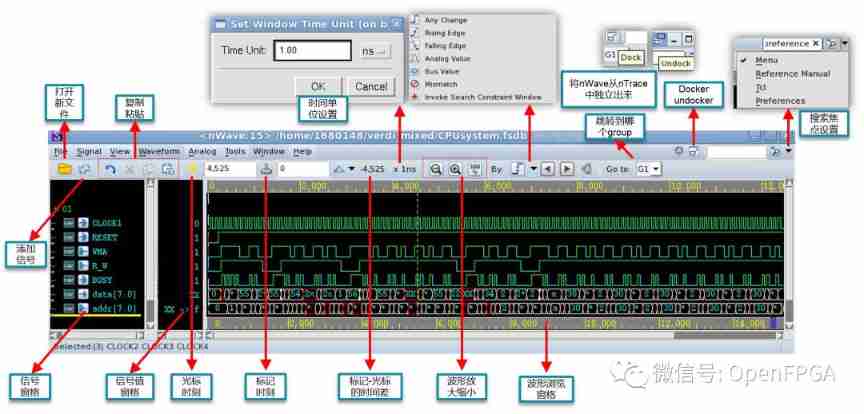

VCD Waveform viewer

nWave : first-class VCD One of the viewers , Support large VCD dump .

*http://www.springsoft.com/

Undertow:Undertow Waveform viewer .

*http://www.veritools-web.com/

GTKWave : Freeware VCD viewer , It seems to be more free than others VCD The viewer is much better .

*http://www.geocities.com/SiliconValley/Campus/3216/GTKWave/gtkwave-win32.html

Dinotrace : come from veritools The free VCD viewer

*http://www.veripool.com/

Code coverage

Verification Navigator

*http://www.transeda.com/

An integrated design verification environment , Can be managed through a powerful set of first-class tools HDL Verification process , So as to achieve consistency 、 Easy to use and efficient verification method . These tools include HDL Check 、 Coverage analysis 、 Test suite analysis and FSM analysis . The environment includes an extensible process manager , Used to easily merge custom validation processes .Verification Navigator Support Verilog、VHDL And mixed language design , And seamlessly integrate with all leading simulation environments .

SureCov

*http://www.verisity.com/

Design chips and semiconductors today IP The kernel engineering team needs to confidently understand how well the functional test suite performs the design .Verisity Of SureCov Measure with the lowest simulation overhead of any available tool FSM And code coverage , And there is no need to change the source design .SureSight The graphical user interface accurately shows which parts of the design have been covered , Which don't have .

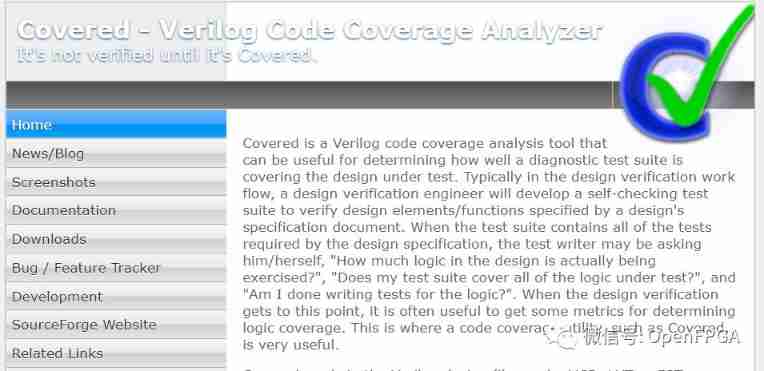

Code Coverage Tool

*http://covered.sourceforge.net/

Free software code coverage tool .Code Coverage Tool It's a kind of Verilog Code coverage analysis tool , It can be used to determine the coverage of test documents to the tested design .

Lint Code checker

Leda:

*http://www.synopsys.com/

Is a code checking tool , Suitable for use Verilog and VHDL Hardware description language (HDL) Designer .Leda Have the ability to analyze HDL The unique ability of code pre synthesis and pre simulation , And it is fully compatible with all popular synthesis and simulation tools and processes . Through the analysis of language grammar 、 Semantics and problematic synthesis / Simulation structure 500 Automation of multiple design checks ,Leda Detect common and subtle and difficult to find code defects , So that designers can focus on design .

HDLint

*http://www.veritools.com/

be used for VHDL and Verilog Powerful and complete linting Tools .

nLint

*http://www.springsoft.com/

nLint It's a comprehensive one HDL Design rule checker , And Debussy The commissioning system is fully integrated .

SureLint

*http://www.verisity.com/

Designers need tools to analyze and debug their designs , Then integrate with the rest of the project .SureLint Provide finite state machines (FSM) analysis 、 Competitive testing and many additional checks , It is the most complete in the market lint Tools .

Utilities

FSMDesigner

*http://mufasa.informatik.uni-mannheim.de/lsra/projects/fsmdes

FSMDesigner It's based on Java Finite state machines (FSM) Editor , It allows hardware designers to specify complex control circuits in a simple and comfortable way . Integrated hardware description language (HDL) generator , Use Simple-Moore FSM Pattern , Ensure efficient, fast and complex control flow , Provide a graphical design interface .

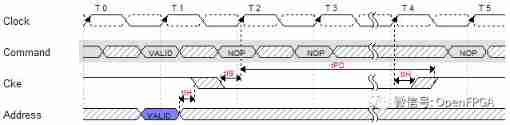

TimeGen

*http://www.xfusionsoftware.com/

TimeGen It is a kind of Engineering CAD Tools , It enables digital design engineers to draw digital sequence diagrams quickly and effectively . Waveforms can be easily exported to other Window Program , for example Microsoft Word, Used to write design specifications . Compared with other tools ,TimeGen It's cheaper .

Waveformer

*http://www.synapticad.com/

Tools for drawing waveforms , For documentation purposes .

Timing Tool

*http://www.timingtool.com/

TimingTool Is a free online sequence diagram editor . This tool provides a very good VHDL and Verilog Test platform , No need to download or install .

Perlilog

*https://opencores.org/projects/perlilog

Perlilog It is a design tool , Its main goal is for system on chip (SoC) Design easy integration Verilog IP kernel .Perilog The idea behind it is IP The core should be like a black box . Installing it for a specific purpose should be as easy as defining the required requirements . Connection core , Become a system , It should be as simple as drawing a frame .Perlilog Yes, it is Perl Compiling , Not yet GUI. Although the scripts included in the system are quite complex , But using its scripting function only requires simple Perl knowledge .

summary

Recommended some gadgets , It is convenient for everyone to write HDL Used to detect defects in code 、 Errors, etc , The tool will be continuously updated later , Especially like Linting(Verilog/SV Code checker -Lint Modeling rule checker and Verilator) This kind of tool used less in China , It's very powerful ( Follow up SystemVerilog I will introduce some hidden transformations of code , Hide case conversion and so on , These places will not be noticed in the design - Especially for beginners ), The main reason is that the tool will give the detailed location and cause of the error when checking the code , There are some FPGA The tool synthesis will not give so detailed error instructions , Some videos will be released later to introduce these tools , At the same time, the introduction of such tools will be added , I hope you will continue to pay attention .

Linux Next Vivado Installation tutorial

Verilog/SV Code checker -Lint Modeling rule checker and Verilator

边栏推荐

- AcWing 1137. Select the best line solution (the shortest circuit)

- 使用IDM下载百度网盘的文件(亲测有用)[通俗易懂]

- Implementation of 453 ATOI function

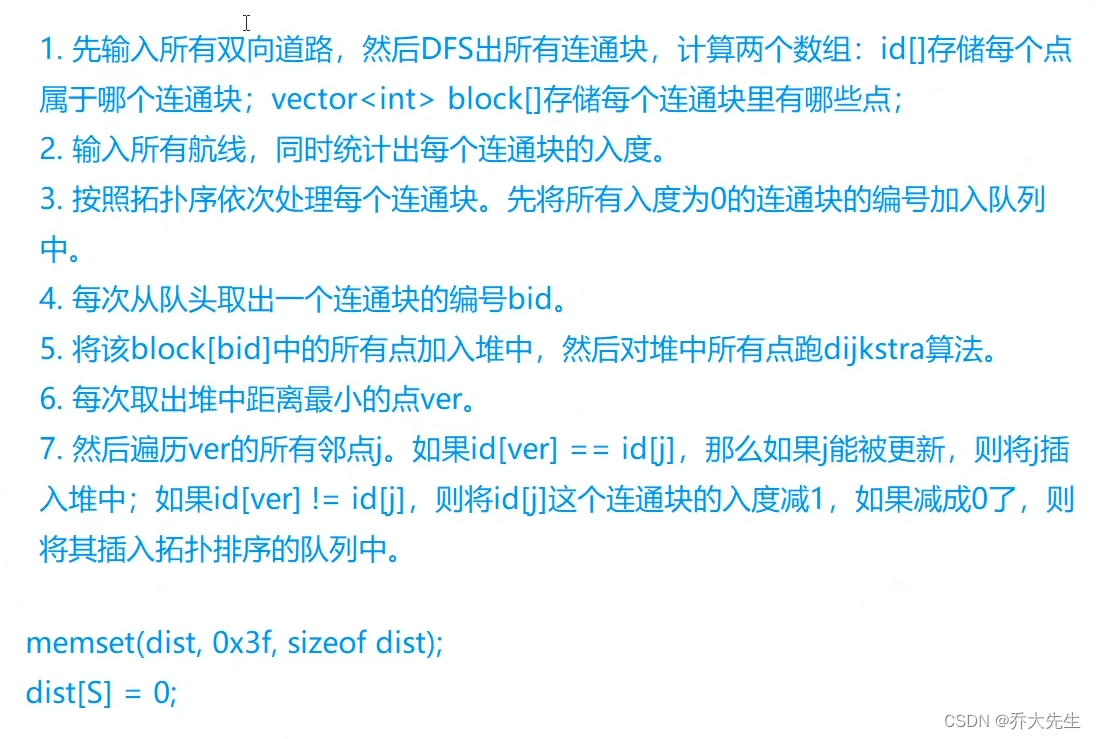

- AcWing 1137. 选择最佳线路 题解(最短路)

- Postman download and installation

- 高并发下如何避免产生重复数据?

- LeetCode 0871. Minimum refueling times - similar to poj2431 jungle adventure

- Which video recording software is better for the computer

- AcWing 383. Sightseeing problem solution (shortest circuit)

- VBScript详解(一)

猜你喜欢

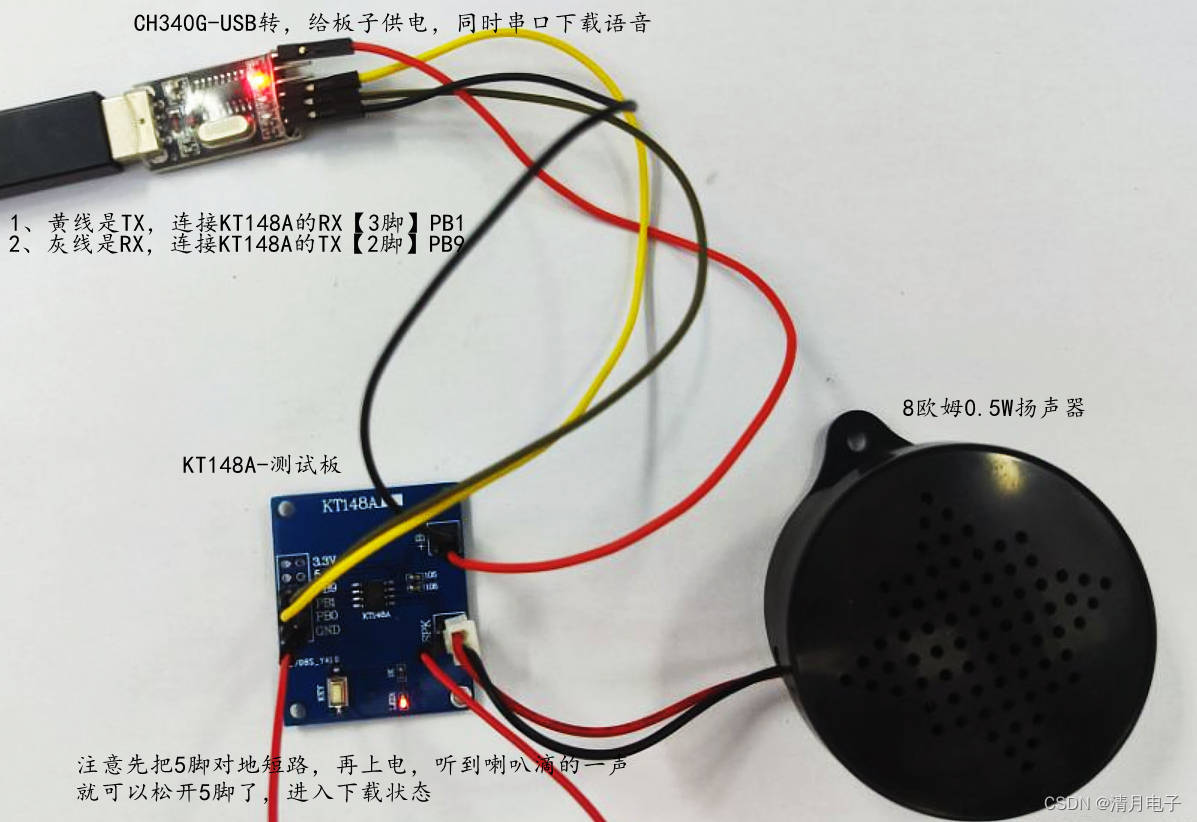

Kt148a voice chip IC user end self replacement voice method, upper computer

Registration opportunity of autowiredannotationbeanpostprocessor under annotation development mode

字典

Shardingsphere jdbc5.1.2 about select last_ INSERT_ ID () I found that there was still a routing problem

SQLite 3.39.0 release supports right external connection and all external connection

AcWing 342. Road and route problem solving (shortest path, topological sorting)

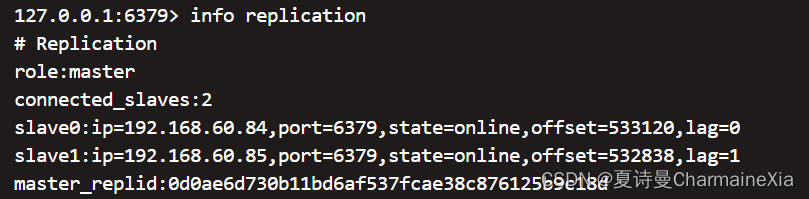

搭建哨兵模式reids、redis从节点脱离哨兵集群

Py之interpret:interpret的简介、安装、案例应用之详细攻略

《重构:改善既有代码的设计》读书笔记(上)

AcWing 1126. Minimum cost solution (shortest path Dijkstra)

随机推荐

搭建哨兵模式reids、redis从节点脱离哨兵集群

多端小程序开发有什么好处?覆盖百度小程序抖音小程序微信小程序开发,抢占多平台流量红利

Gamefi chain game system development (NFT chain game development function) NFT chain game system development (gamefi chain game development source code)

Istio部署:快速上手微服务,

冒泡排序数组

Notes on hardware design of kt148a voice chip IC

Golang:[]byte to string

AcWing 1126. 最小花费 题解(最短路—dijkstra)

AcWing 1134. 最短路计数 题解(最短路)

KT148A语音芯片ic的硬件设计注意事项

Workplace four quadrant rule: time management four quadrant and workplace communication four quadrant "suggestions collection"

RPD出品:Superpower Squad 保姆级攻略

简书自动阅读

高并发下如何避免产生重复数据?

Notes de lecture sur le code propre

AcWing 1131. Saving Private Ryan (the shortest way)

Is there any security guarantee for the ranking of stock and securities companies

Registration opportunity of autowiredannotationbeanpostprocessor under annotation development mode

AcWing 181. 回转游戏 题解(搜索—IDA*搜索)

从20s优化到500ms,我用了这三招