当前位置:网站首页>Xilinx Vivado set *.svh as SystemVerilog Header

Xilinx Vivado set *.svh as SystemVerilog Header

2022-07-02 11:21:00 【Ayka】

Xilinx Vivado does not support setting the file type of a file as SystemVerilog Header till now (version 2021.2.1). This article assumes using "Vivado" Syntax Checking for Xilinx Vivado Text Editor.

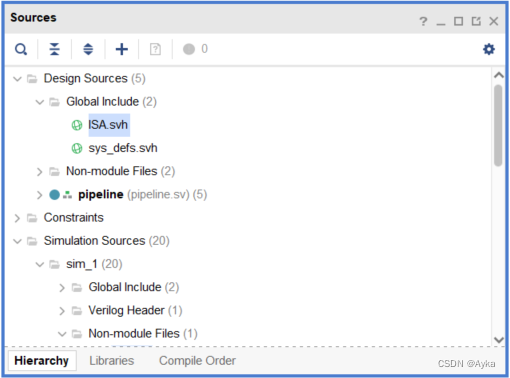

Import *.svh files to Design Sources, where their hierarchy layer is "Non-module Files". In "Sources" sub-window, right-click the .svh files,and click "Set Global Include". After that, *.svh files are appeared in "Global Include" hierarchy layer:

The default file type of these *.svh files is "Verilog Header", so if these *.svh files contain syntaxes that are not Verilog-only, then the syntax checking of Vivado Text Editor will show syntax errors. However, if you set their file type as "SystemVerilog", then the syntax checking will throw no errors for design sources, but throw syntax errors for simulation sources still. Nevertheless, they can both do successful simulations. Obviously, it is a bug of Vivado's syntax checking. If you really do not like the wrong buggy syntax checking, you can try switching file types and doing simulations, then the bug may disappear.

If you add

`include "sys_defs.svh"at the beginning of the simulation sources and the file type of these *.svh files is "Verilog Header", the syntax checking will throw the warning "Warning: cannot open include file 'sys_defs.svh' ", and syntax errors same as the case without the include statement. If the file type of these *.svh files is "SystemVerilog", then the syntax errors are the same as the case that the file type of these *.svh files is "Verilog Header", but the simulation will fail:

ERROR: [VRFC 10-3195] cannot open include file 'sys_defs.svh' [F:/Documents/GitHub/ECE4700J_SU2022/Lab4/project-v-open-beta-For-ECE4700J/optimization/testbench/mem.sv:1]

INFO: [VRFC 10-311] analyzing module mem

ERROR: [VRFC 10-2865] module 'mem' ignored due to previous errors [F:/Documents/GitHub/ECE4700J_SU2022/Lab4/project-v-open-beta-For-ECE4700J/optimization/testbench/mem.sv:18]

and

ERROR: [USF-XSim-62] 'compile' step failed with error(s). Please check the Tcl console output or 'F:/Documents/GitHub/ECE4700J_SU2022/Lab4/lab_4/lab_4.sim/sim_1/behav/xsim/xvlog.log' file for more information.

ERROR: [Vivado 12-4473] Detected error while running simulation. Please correct the issue and retry this operation.

launch_simulation: Time (s): cpu = 00:00:01 ; elapsed = 00:00:07 . Memory (MB): peak = 1551.020 ; gain = 0.000

ERROR: [Common 17-39] 'launch_simulation' failed due to earlier errors.

so do not do that. In brief, do not use any "include" statements.

边栏推荐

- tmall.product.schema.get( 产品信息获取schema获取 ),淘宝店铺上传商品API接口,淘宝商品发布接口,淘宝商品上传API接口,店铺上传接口,oAuth2.0接口

- 4、数组指针和指针数组

- Route (II)

- MQ教程 | Exchange(交换机)

- PTA题库 ===>复数四则运算,一帮一,考试座位号(7-73)

- Methods of software testing

- buuctf-pwn write-ups (7)

- Fabric.js 上划线、中划线(删除线)、下划线

- OpenCV调用USB摄像头的点滴

- Advanced usage of C language -- function pointer: callback function; Conversion table

猜你喜欢

< schematic diagram of oral arithmetic exercise machine program development> oral arithmetic exercise machine / oral arithmetic treasure / children's math treasure / children's calculator LCD LCD driv

![[development environment] 010 editor tool (tool download | binary file analysis template template installation | shortcut key viewing and setting)](/img/de/7d70f513577e93f1bde1969935a29e.jpg)

[development environment] 010 editor tool (tool download | binary file analysis template template installation | shortcut key viewing and setting)

Daily learning 3

2022 home projector preferred! Dangbei F5 brings the ultimate audio-visual experience with its powerful audio-visual effect

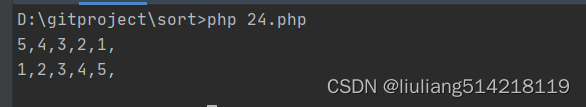

PHP linked list creation and traversal

Design and implementation of car query system based on php+mysql

Fabric.js 缩放画布

由粒子加速器产生的反中子形成的白洞

Quick analysis: easy to share the Internet

Uniapp automated test learning

随机推荐

Stm32-dac Experiment & high frequency DAC output test

What is erdma? Popular science cartoon illustration

Packet capturing tool Fiddler learning

[development environment] Dell computer system reinstallation (download Dell OS recovery tool | use Dell OS recovery tool to make USB flash disk system | install system)

String matching problem

Federated Search: all requirements in search

socket(套接字)与socket地址

buuctf-pwn write-ups (7)

卷积神经网络(入门)

NLA natural language analysis realizes zero threshold of data analysis

千元投影小明Q1 Pro和极米NEW Play谁更好?和哈趣K1比哪款配置更高?

Generally speaking, if the error of inconsistent tab and space occurs frequently

Daily learning 2

由粒子加速器产生的反中子形成的白洞

Talk about idempotent design

OpenHarmony笔记-----------(四)

kaggle如何使用utility script

##51单片机实验之简易验证码发生器

Systemserver process

万物生长大会在杭召开,当贝入选2022中国未来独角兽TOP100榜单