当前位置:网站首页>Understand chisel language thoroughly 07. Chisel Foundation (IV) - bundle and VEC

Understand chisel language thoroughly 07. Chisel Foundation (IV) - bundle and VEC

2022-07-04 14:08:00 【github-3rr0r】

Chisel Basics ( Four )——Bundle and Vec

Chisel In the first three chapters of basics, we learned about data types 、 Combinational circuit operators and registers , Although it is enough to realize very complex digital circuits , But it's not convenient enough . For example, I need to build a 32 Register group of registers , Then I need to write 32 individual RegInit Do you ? Another example is that I want to pack several signals together , How can I achieve it ?Chisel Two configurations are provided for grouping related signals , They are Bundle and Vec, among :

BundleIt is used to divide different types of signals into a group ;VecUsed to represent an indexable 、 A collection of signals of the same type ;

In this part, we will explain them in detail .

Bundle Introduce

Chisel in Bundle Used to combine multiple signals , This Bundle There is no good translation , I prefer to translate it into bundle , It can be understood as binding a bunch of signals , But in order not to cause misunderstanding , I will not translate the latter word .

The whole one bundle It can be quoted as a whole , And the individual fields can be accessed through their names . We define a by defining a class bundle( That is, a set of signals ), This class extends from Bundle class , Each field of it is marked with val The form of is given in the building block , Consider the following code :

class Channel() extends Bundle {

val data = UInt(32.W)

val valid = Bool()

}

Channel This bundle will data and valid These two signals are tied together . If you want to use this bundle Words , We can new One Channel Then package it into a Wire Inside ( there Wire The next article will introduce ), Then use . Just quote :

val ch = Wire(new Channel())

ch.data := 123.U

ch.valid := true.B

val b = ch.valid

. Tokens are commonly used in object-oriented ,x.y It means x Is a reference to an object and y This is a field of this object . because Chisel It's also object-oriented , So of course we can use . To visit bundle In the field .

Chisel Medium Bundle Follow C Inside struct、VHDL Inside record as well as SystemVerilog Inside struct It's all similar . One bundle It can also be quoted as a whole :

val channel = ch

Vec Introduce

Chisel Medium Vec Represents a set of signals of the same type , That's a vector . Every element in the vector can be accessed by index . obviously ,Chisel This vector inside , It is similar to arrays in other programming languages , however Ararry It's already Scala Keywords inside , therefore Chisel It uses Vec.

Create vectors by calling Vec To achieve , This constructor has two parameters , One is the number of elements in the vector , The other is the type of element in the vector . Vectors also need to be encapsulated in a Wire Inside :

val v = Wire(Vec(3, UInt(4.W)))

Every element in the vector can pass (index) To visit :

v(0) := 1.U

v(1) := 3.U

v(2) := 5.U

val idx = 1.U(2.W)

val a = v(idx)

It's understandable , Package to Wire The vector inside is a multiplexer , The selection signal corresponds to the index of the vector , This is packaged as Wire The situation of . We can also package vectors into Reg, To define a set of registers .

For example, the following example defines the register group of a processor , All in all 32 individual 32 Bit register , This is the classic 32 position RISC The register implementation of the processor , such as RISC-V Of 32 Bit version . The code is as follows :

val registerFile = Reg(Vec(32, UInt(32.W)))

See no , This is more stupid than writing 32 Is a register much stronger ?

Again , Elements of register heap ( That is, a register ) You can also use indexes to access and use the same as normal registers :

registerFile(idx) := dIn

val dOur = registerFile(idx)

Bundle and Vec Use

We are free to put Bundle and Vec Put it together .

For example, we can use a bundle Create a vector , We need to pass a prototype to the vector field , For example, for the above Channel, We can use the following code to define a Channel vector :

val vecBundle = Wire(Vec(8, new Channel()))

Bundle There can also be vectors , such as :

class BundleVec extends Bundle {

val field = UInt(8.W)

val vector = Vec(4, UInt(8.W))

}

If we want to create a with reset value bundle Register of type , We have to create that first bundle Of Wire, Set the initial value of each field as needed , Then pass it to RegInit:

val initVal = Wire(new Channle())

initVal.data := 0.U

initVal.valid := false.B

val channelReg = RegInit(initVal)

By combining Bundle and Vec Equal structure , We can define our own data structure , This is it. Chisel One of the places that embody strong abstract ability .

Partial assignment and Bundle

stay Chisel Partial assignment in is not allowed , Although in Chisel2 Medium can , stay Verilog and VHDL It's also possible , For example, the following code will report an error when the circuit is expanded :

val assignWord = Wire(UInt(16.W))

assignWord(7, 0) := lowByte

assignWord(15, 8) := highByte

under these circumstances , Use Bundle It's a good solution . For example, first create a part bundle, Then give this bundle Create a Wire, Then assign values to each individual field , Last use asUInt() Put this bundle convert to UInt And assign it to the target UInt. Be careful , So let's take this Bundle It is defined as a local data structure because it is only used here . The code is as follows :

val assignWord = Wire(UInt(16.W))

class Split extends Bundle {

val high = UInt(8.W)

val low = UInt(8.W)

}

val split = Wire(new Split())

split.low := lowByte

split.high := highByte

assignWord := split.asUInt

But there's a drawback to this approach , That's what we need to know bundle What is the order after the fields inside are merged into a bit vector , Like here high and low It can't be reversed .

Another way is to use Bool Construct vectors , In this way, each value can be assigned independently , Finally, it is converted into UInt Just fine :

val vecResult = Wire(Vec(4, Bool()))

vecResult(0) := data(0)

vecResult(1) := data(1)

vecResult(2) := data(2)

vecResult(3) := data(3)

val uintResult = vecResult.asUInt

Conclusion

Bundle and Vec stay Chisel It's very important , Proficiency can greatly improve the efficiency of writing code , Dealing with more complex 、 Scenes that require more modularity will also be more comfortable . Another core concept is also used in this article Wire, That is to say Verilog Medium wire, Namely wire network . This Wire And what I said before UInt、SInt What's different , It directly represents the type of hardware , except Wire Outside ,Chisel in Reg and IO It is also the type of direct hardware , The next part will talk about these three , Say more about how to understand Chisel Generation circuit .

边栏推荐

- Unittest中的TestSuite和TestRunner

- OPPO Find N2产品形态首曝:补齐各项短板

- Install Trinity and solve error reporting

- 自主工业软件的创新与发展

- 美国土安全部部长警告移民“不要踏上危险的旅程”

- Ruichengxin micro sprint technology innovation board: annual revenue of 367million, proposed to raise 1.3 billion, Datang Telecom is a shareholder

- E-week finance | Q1 the number of active people in the insurance industry was 86.8867 million, and the licenses of 19 Payment institutions were cancelled

- 字节面试算法题

- MongoDB常用28条查询语句(转)

- The Secretary of Homeland Security warned immigrants "not to embark on a dangerous journey"

猜你喜欢

【FAQ】华为帐号服务报错 907135701的常见原因总结和解决方法

Redis —— How To Install Redis And Configuration(如何快速在 Ubuntu18.04 与 CentOS7.6 Linux 系统上安装 Redis)

華昊中天沖刺科創板:年虧2.8億擬募資15億 貝達藥業是股東

2022年山东省安全员C证考试题库及在线模拟考试

![[R language data science]: cross validation and looking back](/img/a8/84a5685ebcb12d3cf8e32e1fbac053.png)

[R language data science]: cross validation and looking back

SCM polling program framework based on linked list management

小程序直播 + 电商,想做新零售电商就用它吧!

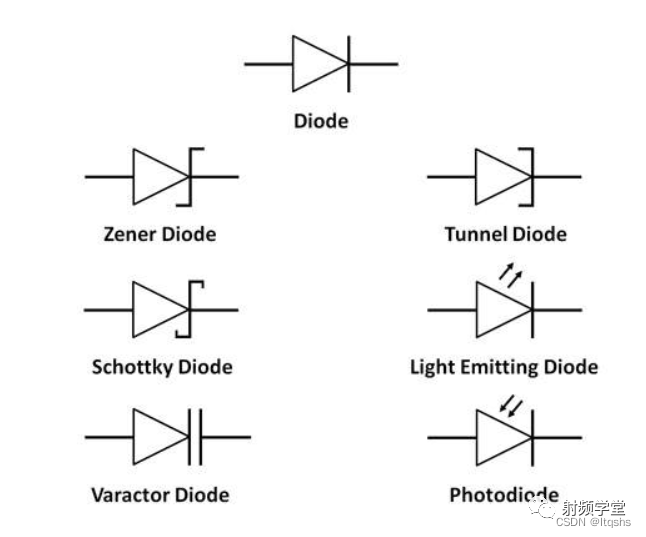

硬件基础知识-二极管基础

华昊中天冲刺科创板:年亏2.8亿拟募资15亿 贝达药业是股东

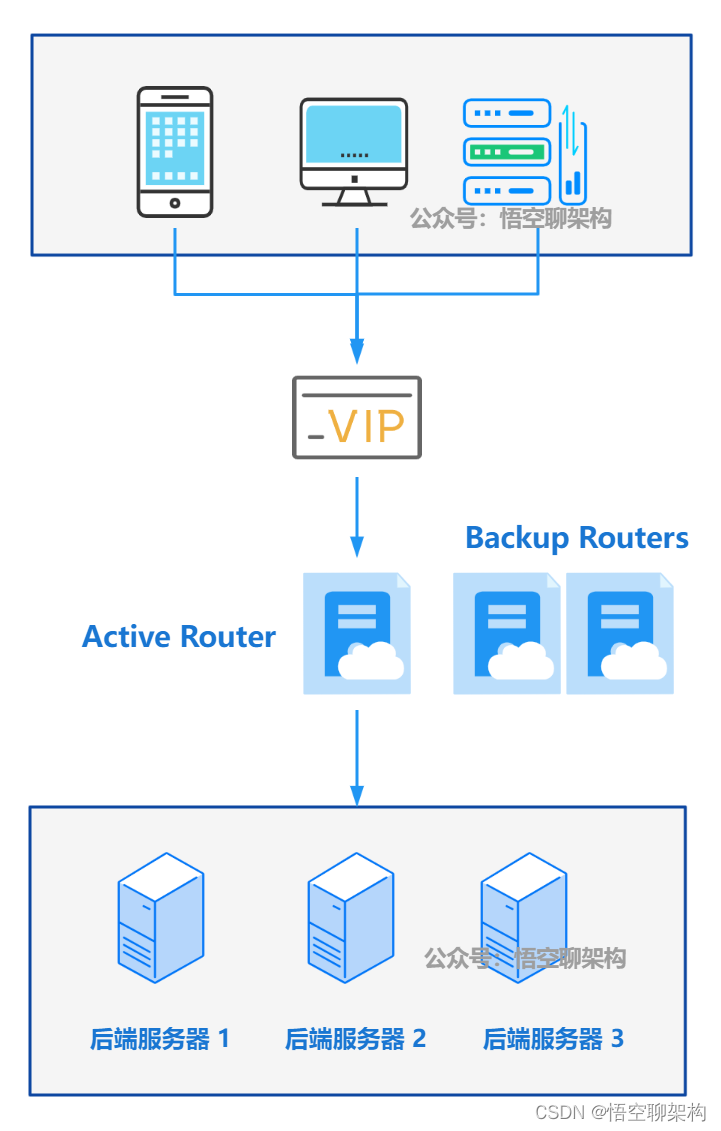

一次 Keepalived 高可用的事故,让我重学了一遍它

随机推荐

Introduction to reverse debugging PE structure resource table 07/07

好博医疗冲刺科创板:年营收2.6亿 万永钢和沈智群为实控人

【R语言数据科学】:交叉验证再回首

逆向调试入门-PE结构-资源表07/07

MySQL 5 installation and modification free

美国土安全部部长警告移民“不要踏上危险的旅程”

One of the solutions for unity not recognizing riders

吃透Chisel语言.11.Chisel项目构建、运行和测试(三)——Chisel测试之ScalaTest

Service Mesh的基本模式

安装trinity、解决报错

Five "potential errors" in embedded programming

go vendor 项目迁移到 mod 项目

SCM polling program framework based on linked list management

Automatic filling of database public fields

自主工业软件的创新与发展

Interviewer: what is the internal implementation of hash data type in redis?

国内酒店交易DDD应用与实践——代码篇

小程序直播 + 电商,想做新零售电商就用它吧!

1200. Minimum absolute difference

WS2811 M是三通道LED驱动控制专用电路彩灯带方案开发