当前位置:网站首页>Interruption system of 51 single chip microcomputer

Interruption system of 51 single chip microcomputer

2022-07-03 09:55:00 【Yiao】

One · structure

1.(P3.2) May by IT0 Select whether it is active at low level or active at falling edge . When CPU detected P3.2 When a valid interrupt signal appears on the pin , Interrupt flag IE0 Set up 1, towards CPU Application interruption .

2. (P3.3) May by IT1 Select whether it is active at low level or active at falling edge . When CPU detected P3.3 When a valid interrupt signal appears on the pin , Interrupt flag IE1 Set up 1, towards CPU Application interruption .

3. TF0, MCU internal timer / Counter T0 Overflow interrupt request flag bit . Timer / Counter T0 In case of spillage , Set as TF0, And to CPU Application interruption .

4.TF1, Timer in MCU / Counter T1 Overflow interrupt request flag bit . Timer / Counter T1 In case of spillage , Set up TF1, And to CPU Application interruption .

5.RI or TI, Serial port interrupt request flag . Set when the serial port receives a frame of serial data RI Or set when the serial port sends a frame of serial data TI, towards CPU Application interruption .

Two . Interrupt allowed control bit

IT0, External interrupt 0 Trigger mode bit .(IT0=1, Falling edge trigger ;IT0=0, Low level trigger ) IE0, External interrupt 0 Interrupt request flag bit . IT1, External interrupt 1 Trigger mode control bit . IE1, External interrupt 1 Interrupt request flag bit . TF0, timing / Counter T0 Overflow interrupt request flag bit . TF1, timing / Counter T1 Overflow interrupt request flag bit .

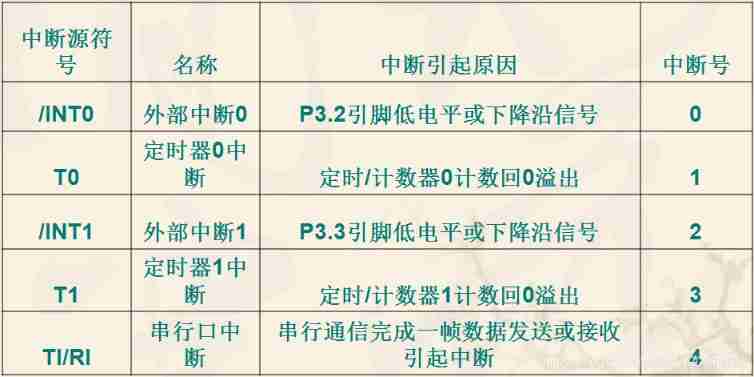

3、 ... and , Interrupt source

Four , Interrupt response condition 1· Interrupt source has interrupt request ; 2· The interrupt allowed bit of this interrupt source is 1; 3·CPU General interruption (EA=1). With external interrupt 0 For example EA=1; // Open total interrupt EX0=1; // Open external interrupt 0 IT0=0/1; // Set the external interrupt trigger mode Interrupt service function

void int0 () interrupt 0

{

do anything that you want

}

边栏推荐

- C language enumeration type

- Oracle数据库 SQL语句执行计划、语句跟踪与优化实例

- The new series of MCU also continues the two advantages of STM32 product family: low voltage and energy saving

- Assignment to '*' form incompatible pointer type 'linkstack' {aka '*'} problem solving

- Convert IP address to int

- 顺利毕业[3]-博客系统 更新中。。。

- Quelle langue choisir pour programmer un micro - ordinateur à puce unique

- CEF download, compile project

- GPIO port details, Hal library operation keys

- [male nanny style] teach you to open the first wechat applet

猜你喜欢

PRACH --- originator

MySQL Data Definition Language DDL common commands

Nr--- Pusch I: sorting out the agreement process

Runtime. getRuntime(). GC () and runtime getRuntime(). The difference between runfinalization()

Stm32f407 key interrupt

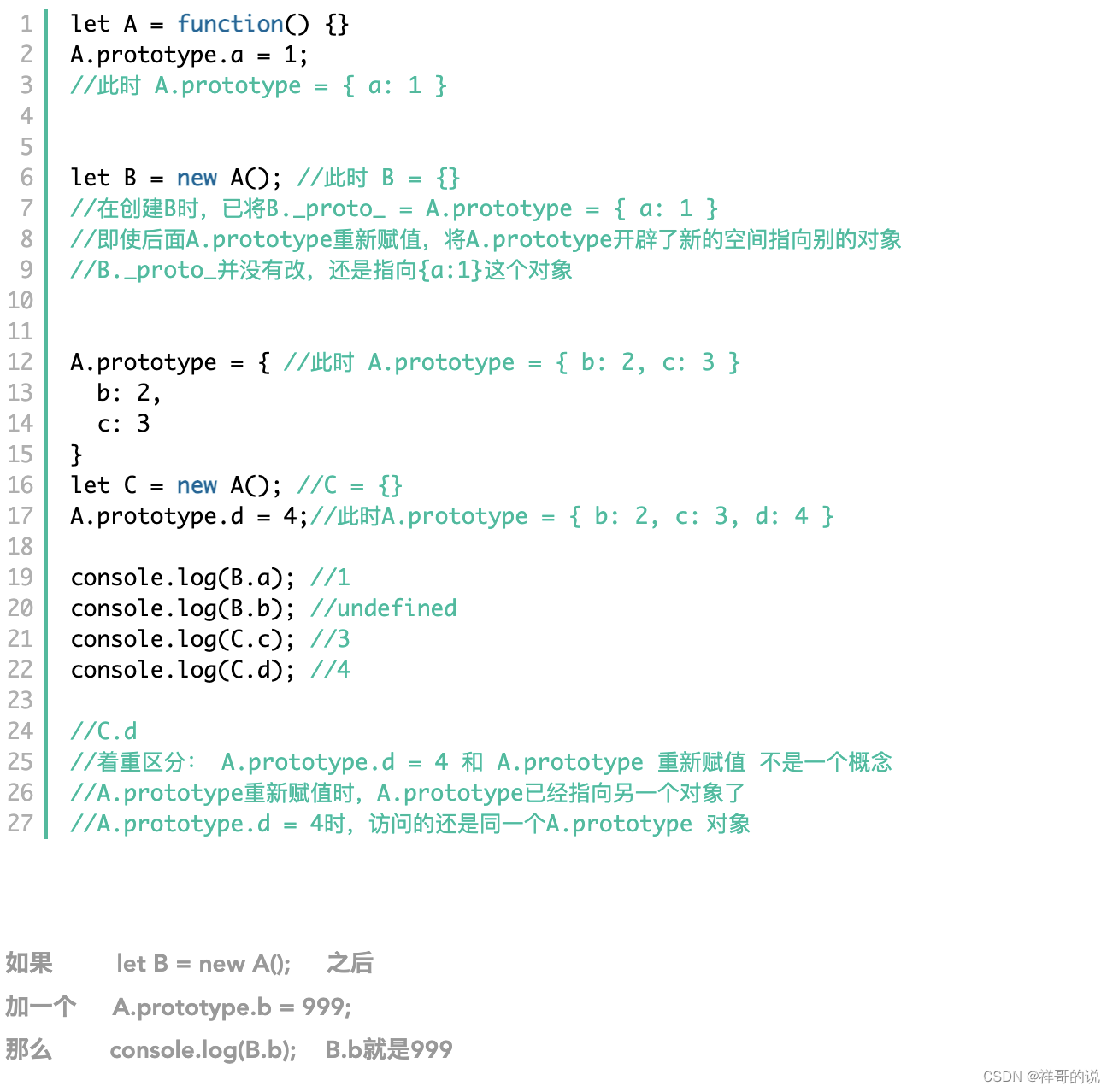

JS基础-原型原型链和宏任务/微任务/事件机制

el-table X轴方向(横向)滚动条默认滑到右边

![[male nanny style] teach you to open the first wechat applet](/img/a1/a571609ee846adf75506a88a629906.png)

[male nanny style] teach you to open the first wechat applet

内存数据库究竟是如何发挥内存优势的?

MySQL data manipulation language DML common commands

随机推荐

Runtime. getRuntime(). GC () and runtime getRuntime(). The difference between runfinalization()

Gpiof6, 7, 8 configuration

How MySQL modifies null to not null

Project cost management__ Cost management technology__ Article 8 performance review

C language enumeration type

UCI and data multiplexing are transmitted on Pusch - placement of data and UCI positions (Part III)

顺利毕业[3]-博客系统 更新中。。。

When you need to use some functions of STM32, but 51 can't realize them, 32 naturally doesn't need to learn

Nr--- Pusch I: sorting out the agreement process

2020-08-23

[successful graduation] [1] - visit [student management information system]

万字手撕七大排序(代码+动图演示)

嵌入式系统没有特别明确的定义

Fundamentals of Electronic Technology (III)__ Logic gate symbols in Chapter 5

学习开发没有捷径,也几乎不存在带路会学的快一些的情况

Definition and use of enum in C language

Fundamentals of Electronic Technology (III)__ Fundamentals of circuit analysis__ Basic amplifier operating principle

Error output redirection

Eight working modes of stm32gpio and chip naming rules

UCI and data multiplexing are transmitted on Pusch (Part VI) -- LDPC coding