当前位置:网站首页>Understand chisel language thoroughly 04. Chisel Foundation (I) - signal type and constant

Understand chisel language thoroughly 04. Chisel Foundation (I) - signal type and constant

2022-07-04 14:08:00 【github-3rr0r】

Chisel Basics ( One )—— Signal types and constants

At first, it must be an introduction Chisel The basic content of ,《Chisel Basics 》 This part mainly introduces two basic components in digital design : Combinational circuits and triggers . Neither of these basic components is complicated , But together, you can get a large scale 、 It is also a powerful digital circuit .

In the digital logic circuit system , Generally, binary signals are used , That is to say, only two possible values are allowed for a single bit or a single signal , That's what we all know 0 and 1. But in digital design , Some other terms may be used , such as : low (low)/ high (high), false (false)/ really (true), Or set invalid (de-asserted)/ Set valid (asserted). These groups of terms correspond to 0 and 1, But pay attention to the last group de-asserted and asserted, I translate it here as set invalid and set valid , The reason is that in some scenarios, the low level is effective , In some scenarios, high level is effective , So they and 0/1 The corresponding relationship of depends on the specific scenario .

In the first part, let's take a brief look Chisel Signal types and constants in , In the last article, there is also a related introduction , It also includes and Verilog Contrast between .

Three basic signal types

Chisel There are three basic data types to describe signals 、 Combinational logic and registers :Bits、UInt and SInt. among UInt and SInt from Bits Expanded .

These three types are signals / Vector of bits .UInt Used to represent the bit vector corresponding to an unsigned integer , and SInt Represents the bit vector corresponding to a signed integer , and Chisel The signed integer encoding method used is Binary complement , I learned this in computer general courses .

Below Chisel The code defines a 8 position Bits、 One 8 Bit unsigned integer and a 10 Bit signed integer :

Bits(8.W)

UInt(8.W)

SInt(10.W)

The width of these bit vectors is through Chisel Width type Width To define the , expression n.W You can put a Scala The integer is converted to a Width, Then it is used for the definition of bit vector :

n.W

Bits(n.W)

Be careful : Current version Chisel Medium Bits There is no corresponding operation , So it's of little use to us , Just know there's such a thing .

Chisel Constant

Constants can be used like Width Define methods to define , Direct use Scala The integer of is converted to Chisel Type is OK :

0.U // Defined a UInt Constant of type 0

-3.S // Defined a SInt Constant of type -3

When defining constants, you can also take the width , Use or Chisel Of Width type :

3.U(4.W) // A bit width is defined as 4 Of UInt Type constant 3

Maybe you think 3.U and 4.W This kind of notation is very strange , Then you can think of it as an integer constant followed by a type . This notation is similar to C、Java and Scala Medium 3L, Indicates a value of 3 Long integer .

A common problem when defining a specified width constant

We may define a constant with a specified width , Forget the width behind .W identifier , such as 1.U(32). This representation Can't Define a 32 Constant of bit width 1, contrary , expression (32) Will be interpreted as 1.U This number is in position 32 Bit extraction on , That is, you will get a single bit constant 0, Obviously, it's not what we expected , Therefore, we must not omit .W!

Chisel Use other base numbers to represent constants

Chisel It's from Scala Extended ,Scala Type inference in Chisel Benefit a lot , Therefore, the type information in many places can be omitted . This type of inference on bit width also applies ,Chisel It will automatically infer the correct bit width , So from this point of view Chisel Describing hardware circuits is also better than Verilog and VHDL More concise 、 More readable .

For constants in base numbers other than decimal , Constants are defined by strings , Determine the base according to the character at the beginning of the string . among h It's hexadecimal ,o It's octal ,b For binary , The following code uses these three bases to represent constants 255:

"hff".U

"o377".U

"b1111_1111".U

It can be noted that , The above definitions are useless (n.W) To specify the width , Because this can be omitted ,Chisel The minimum width will be automatically inferred to represent this constant , Here is all 8 position (255 The binary representation of 8 Bit binary number ).

You can also notice ,"b1111_1111" Underline in , Here is for grouping numbers , Make the code more readable , In the compiler's view, underscores are omitted , such as b_1_1_11_1111 and b11111111 Is equivalent .

Chisel of use ASCII Characters represent constants

ASCII code ( Content of computer general course ) The character of can also be used for Chisel Constant definition of :

val aChar = 'A'.U

The result is UInt<7>(65), namely 7 Bit unsigned number 65. Note that strings cannot be used in this way , such as :

val aChar = "AA".U // Incorrect usage

Report error as chisel3.internal.ChiselException: Invalid base A, That is, for strings ,Chisel The first character will be regarded as the base of a hexadecimal string .

Chisel Logical value in

To represent logical values ,Chisel Types are defined in Bool.Bool The value of type can represent a true perhaps false Value , Define a Bool Variables of type can be like this :

Bool()

And constant Bool Value can be passed Scala The logical value is converted to , Method is xx.B:

true.B

false.B

边栏推荐

- js中的变量提升和函数提升

- 担心“断气” 德国正修改《能源安全法》

- 自主工业软件的创新与发展

- 吃透Chisel语言.05.Chisel基础(二)——组合电路与运算符

- 一次 Keepalived 高可用的事故,让我重学了一遍它

- 2022g3 boiler water treatment examination question simulation examination question bank and simulation examination

- 美国土安全部长:国内暴力极端主义是目前美面临的最大恐怖主义威胁之一

- How to choose a technology stack for web applications in 2022

- Fs7867s is a voltage detection chip used for power supply voltage monitoring of digital system

- Huahao Zhongtian rushes to the scientific and Technological Innovation Board: the annual loss is 280million, and it is proposed to raise 1.5 billion. Beida pharmaceutical is a shareholder

猜你喜欢

2022g3 boiler water treatment examination question simulation examination question bank and simulation examination

动画与过渡效果

Detailed explanation of Fisher information quantity detection countermeasure sample code

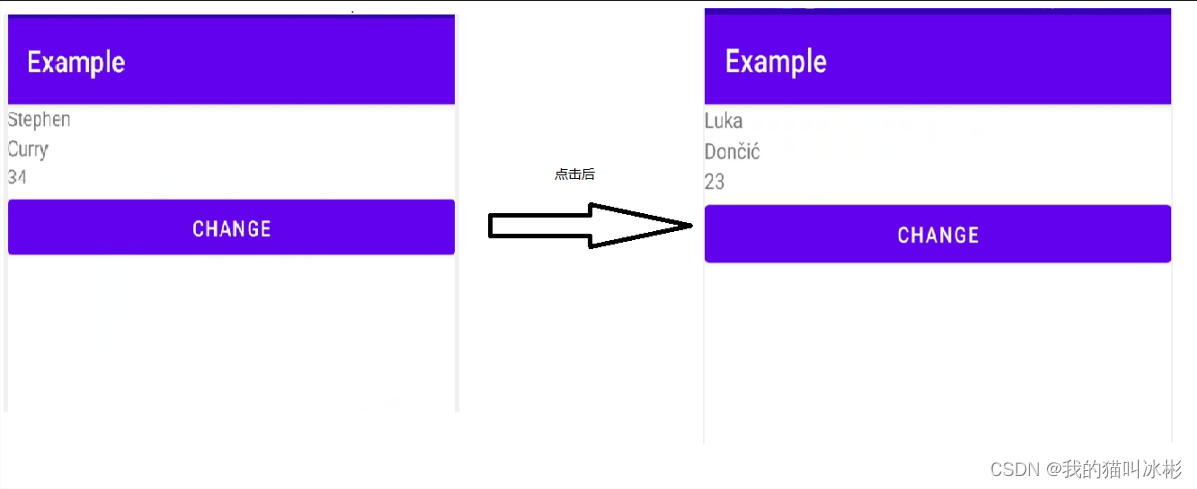

Understanding and difference between viewbinding and databinding

【Matlab】conv、filter、conv2、filter2和imfilter卷积函数总结

![[R language data science]: cross validation and looking back](/img/a8/84a5685ebcb12d3cf8e32e1fbac053.png)

[R language data science]: cross validation and looking back

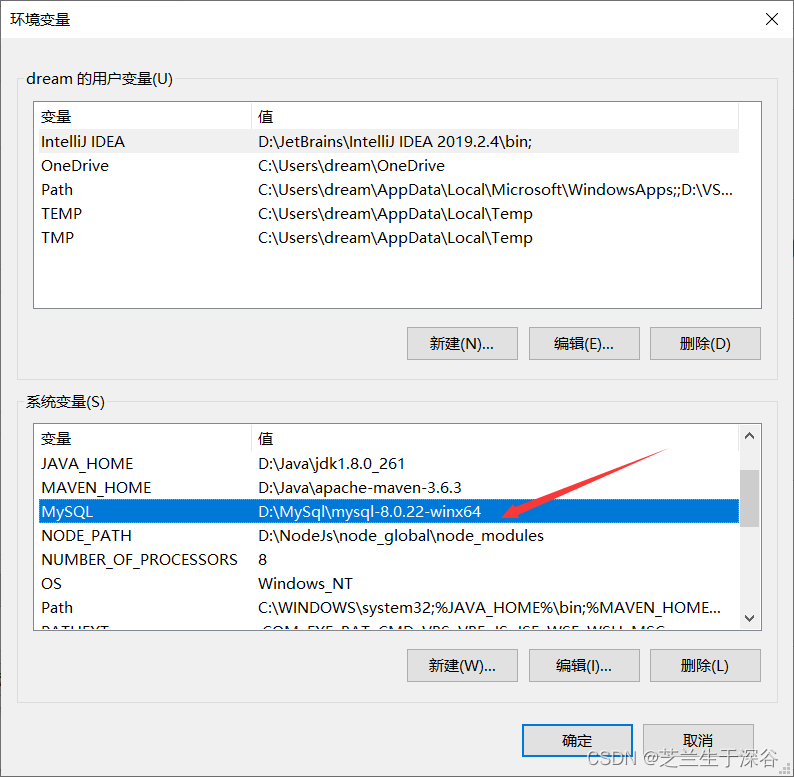

MySQL version 8 installation Free Tutorial

![[antd] how to set antd in form There is input in item Get input when gourp Value of each input of gourp](/img/eb/11e5da1c5e897c5f6a18d49125925f.png)

[antd] how to set antd in form There is input in item Get input when gourp Value of each input of gourp

德明利深交所上市:市值31亿 为李虎与田华夫妻档

How to choose a technology stack for web applications in 2022

随机推荐

中邮科技冲刺科创板:年营收20.58亿 邮政集团是大股东

CVPR 2022 | 大幅减少零样本学习所需的人工标注,提出富含视觉信息的类别语义嵌入(源代码下载)...

30:第三章:开发通行证服务:13:开发【更改/完善用户信息,接口】;(使用***BO类承接参数,并使用了参数校验)

2022kdd pre lecture | 11 first-class scholars take you to unlock excellent papers in advance

Interviewer: what is the internal implementation of hash data type in redis?

Dgraph: large scale dynamic graph dataset

MySQL version 8 installation Free Tutorial

自主工业软件的创新与发展

以房抵债能否排除强制执行

基于YOLOv1的口罩佩戴检测

IDEA快捷键大全

MongoDB常用28条查询语句(转)

Getting started with microservices

php 日志调试

MySQL 5 installation and modification free

go vendor 项目迁移到 mod 项目

Haobo medical sprint technology innovation board: annual revenue of 260million Yonggang and Shen Zhiqun are the actual controllers

. Net delay queue

Service Mesh的基本模式

205. 同构字符串