当前位置:网站首页>【數字IC驗證快速入門】20、SystemVerilog學習之基本語法7(覆蓋率驅動...內含實踐練習)

【數字IC驗證快速入門】20、SystemVerilog學習之基本語法7(覆蓋率驅動...內含實踐練習)

2022-07-07 15:24:00 【luoganttcc】

導讀:作者有幸在中國電子信息領域的排頭兵院校“電子科技大學”攻讀研究生期間,接觸到前沿的數字IC驗證知識,旁聽到諸如華為海思、清華紫光、聯發科技等業界頂尖集成電路相關企業面授課程,對數字IC驗證有了一些知識積累和學習心得。為幫助想入門前端IC驗證的朋友,思忱一二後,特開此專欄,以期花最短的時間,走最少的彎路,學最多的IC驗證技術知識。

文章目錄

- 一、內容概述

- 二、基於覆蓋率驅動的驗證技術

- 三、功能覆蓋率模型

- 四、功能覆蓋率收斂

- 五、功能覆蓋率數據

- 六、功能覆蓋率數據的歸一化和分析

- 七、覆蓋率的類型:RTL代碼覆蓋率

- 八、覆蓋率的類型:斷言覆蓋率

- 九、覆蓋率的類型:功能覆蓋率

- 九、覆蓋率的類型:功能覆蓋率 VS 代碼覆蓋率

- 十、基於覆蓋率驅動的驗證策略

- 十一、覆蓋率與缺陷率(Bug rate)的關系

- 十二、定義功能覆蓋率模型

- 十三、功能覆蓋率的建模

- 十四、功能覆蓋率報告

- 十五、功能覆蓋率的采樣事件

- 十六、功能覆蓋率:觸發SystemVerilog Assertion

- 十七、定義覆蓋點:信號和錶達式

- 十八、定義覆蓋點:bins

- 十九、定義覆蓋點:條件覆蓋

- 二十、定義覆蓋點:狀態跳轉覆蓋

- 二十一、定義覆蓋點:交叉覆蓋

- 二十二、參數化的覆蓋率:提供代碼的重用性

- 二十三、covergroup實戰補充(2021-10-15)

- 二十四、小結

- X、實踐練習

一、內容概述

- 基於覆蓋率驅動的驗證技術

- 覆蓋率類型:代碼覆蓋率(工具自動生成,客觀)和功能覆蓋率(人為定義覆蓋點,主觀)

- SV中的功能覆蓋率建模

- 定義覆蓋率模型:

covergroup - 定義覆蓋點:

coverpoint - 覆蓋點的

bins - 覆蓋率函數

覆蓋率驅動 可以用來衡量我們的驗證進度,簡而言之就是,看我們驗了半天驗到了什麼程度。當然最核心的還是保證我們驗證完備性,我們能識別到的點都要驗證到。需要澄清的是,覆蓋率達到要求,並不能說驗證就真正的OK了,其實驗證的空間還是非常大的,只是說我們的風險變小了,不能說一點風險都沒有!故,驗證有時候還是我們盡力而為的一個東西。

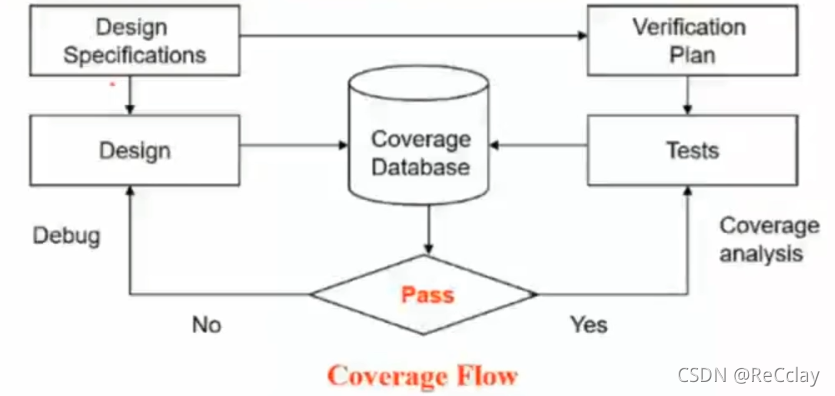

二、基於覆蓋率驅動的驗證技術

- 覆蓋率是對RTL設計功能進行驗證後達到的覆蓋百分比(量化數據)

- 檢查過程必須滿足完整性與正確性,沒有冗餘的勞動

- 為了最小化驗證工作量,使用覆蓋率來衡量一個設計哪些功能測試過,哪些功能還沒有被測試過

- 功能覆蓋率是由驗證工程師自己定義的,用於衡量設計規格是否被正確實現,具體內容體現在驗證計劃中

- 功能覆蓋率用於檢查設計的應用場景、邊界條件、特殊變量或者設計條件是否被完整的正確的測試或者確認過

三、功能覆蓋率模型

定義覆蓋率模型

- 編寫覆蓋率模型用於衡量驗證計劃的目標是否被實現

- 功能覆蓋率模型不能自動的從設計中獲取

- 功能覆蓋率模型是由驗證工程師自己定義,在驗證環境中檢查設計意圖和設計功能是否被正確實現

- 根據設計規格書和驗證計劃,驗證工程師需要定義哪些內容必須被覆蓋到(被測試到或者被驗證到)

步驟

- 定義采樣的信號(coverage group)

- 定義采樣的時間

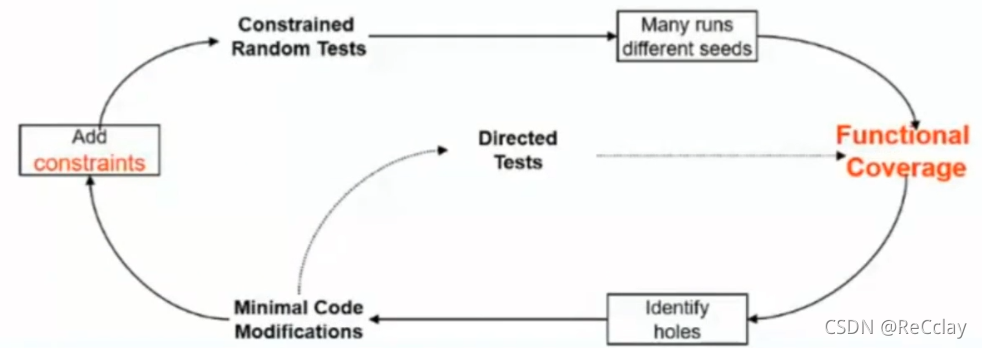

四、功能覆蓋率收斂

- 覆蓋率收斂

- 采用什麼樣的策略和行為,使得覆蓋率達到100%

- 功能覆蓋率適用於衡量測試案例覆蓋了哪些設計屬性(design feathures)

- 覆蓋率收斂是一個反饋環路,用於分析覆蓋率的結果並為下一步達到100%的覆蓋率確定測試方案

- 使用不同的種子(seed)運行現有的測試哪裏

- 新增約束(new constraints)

- 采用什麼樣的策略和行為,使得覆蓋率達到100%

五、功能覆蓋率數據

- 收集覆蓋率數據

- 使用多個種子運行同一個測試案例

- 檢查測試用例(case)是否正確運行(pass/fail)

- 只有當測試用例(case)的仿真結果正確時,功能覆蓋率數據才有效

- 因RTL設計中的bug導致仿真結果不正確時,功能覆蓋率數據無效,必須丟弃

- 分析覆蓋率

- 在設計中收集代碼覆蓋率,在驗證中收集功能覆蓋率

- 收集覆蓋率是一個回歸的過程!

六、功能覆蓋率數據的歸一化和分析

- 收集覆蓋率數據庫,並歸一化處理

- 使用不同的種子,多次重複運行隨機化驗證平臺和測試用例

- 將所有測試用例運行的功能覆蓋率結果歸一化處理,用於衡量驗證進度

- 分析覆蓋率數據,確認如何修改測試用例

- 如果獲取的覆蓋率數據保持穩定,需要使用不同的種子測試用例並且測試用例運行時間要延長

- 如果覆蓋率增長緩慢,需要增加約束條件獲得更多有效激勵

- 如果遇到瓶頸,需要創建更多的直接測試用例,滿足邊界條件

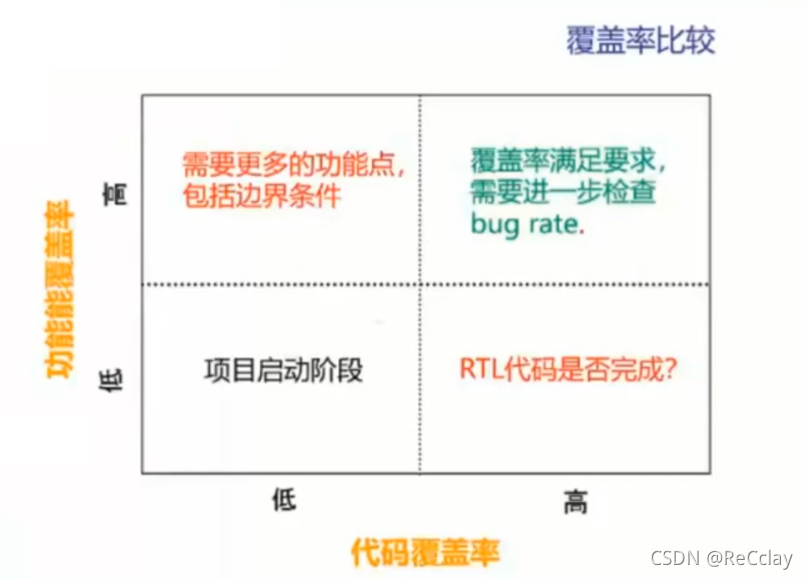

- 當功能覆蓋率接近100%時,需要檢查bug出現的幾率,如果bug經常被發現,說明有一部分設計的覆蓋不完整。如果不出現bug,說明設計驗證工作結束。

七、覆蓋率的類型:RTL代碼覆蓋率

注:代碼覆蓋率是一個客觀條件,即代碼風格維度看覆蓋率,代碼覆蓋率很容易也必須(或雖然達不到但可解釋)要求達到100%。

- 代碼覆蓋率

- 衡量測試用例驗證覆蓋了哪些設計規格在RTL中實現了,而不能衡量驗證計劃

- 行(

Line Coverage):RTL中的代碼行 - 有限狀態機(

FSM Coverage):RTL代碼中的有限狀態機的狀態和狀態之間的轉化 - 路徑(

Path Coverage):RTL代碼中的路徑分支(if-else語句) - 信號反轉(

Toggle Coverage):RTL代碼中的一個信號從0跳變到1,以及從1跳變到0 - 比導師(

Expression Coverage):RTL代碼中的條件錶達式,例如if(a & b & c)

- 行(

- 衡量測試用例驗證覆蓋了哪些設計規格在RTL中實現了,而不能衡量驗證計劃

八、覆蓋率的類型:斷言覆蓋率

注:功能覆蓋率更多的去檢查邏輯功能,看不到時序信息是否正確,所以就有了斷言覆蓋率!

- Assertion Coverage 斷言覆蓋率

- 斷言是一種聲明性的代碼,用於檢查RTL代碼中的信號之間的(時序)關系

- 斷言可以使用過程性的代碼或者使用

SystemVerilog Assertions - 斷言可以檢查信號的值或者設計的狀態

cover property語句

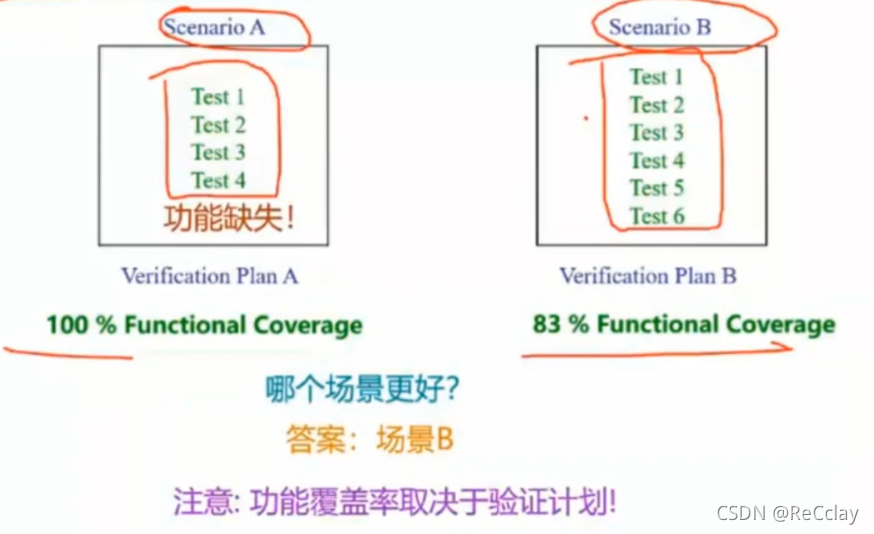

九、覆蓋率的類型:功能覆蓋率

- 與設計意圖有關系

- 功能覆蓋率取决於驗證計劃!

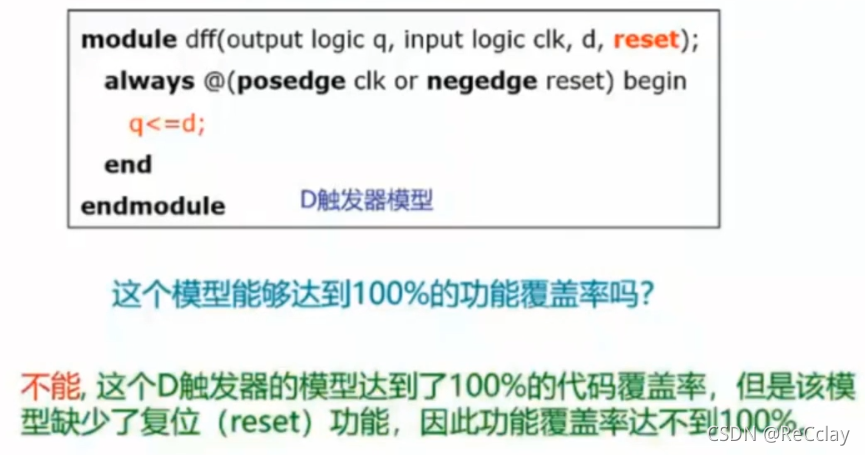

九、覆蓋率的類型:功能覆蓋率 VS 代碼覆蓋率

- 100% 代碼覆蓋率並不意味著100%的功能覆蓋率!

十、基於覆蓋率驅動的驗證策略

- 收集信息而不是數據

- 只能衡量使用了哪些內容

- 衡量完整性

十一、覆蓋率與缺陷率(Bug rate)的關系

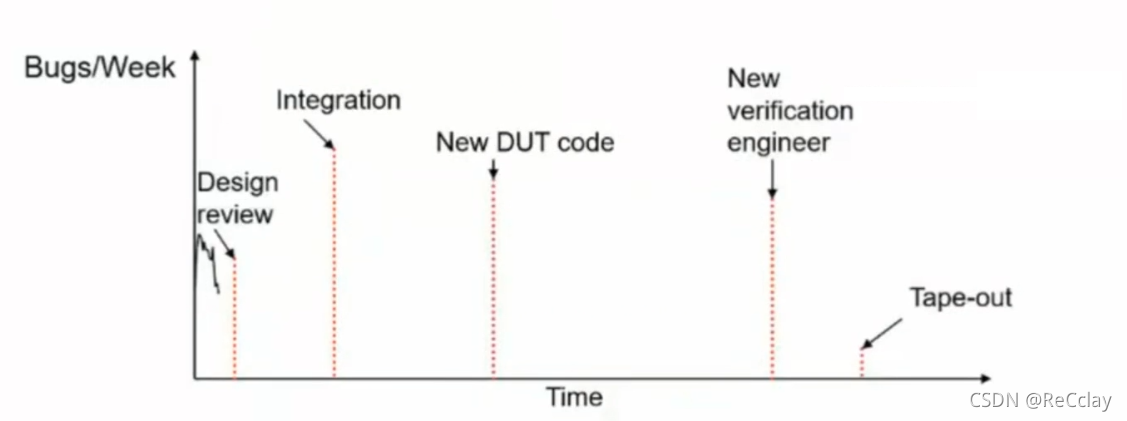

- Bug 出現的幾率

- Bug rate是指新的RTL功能缺陷被發現的幾率,可以間接的衡量覆蓋率

- Bug rate隨著項目和驗證的進度不斷變化

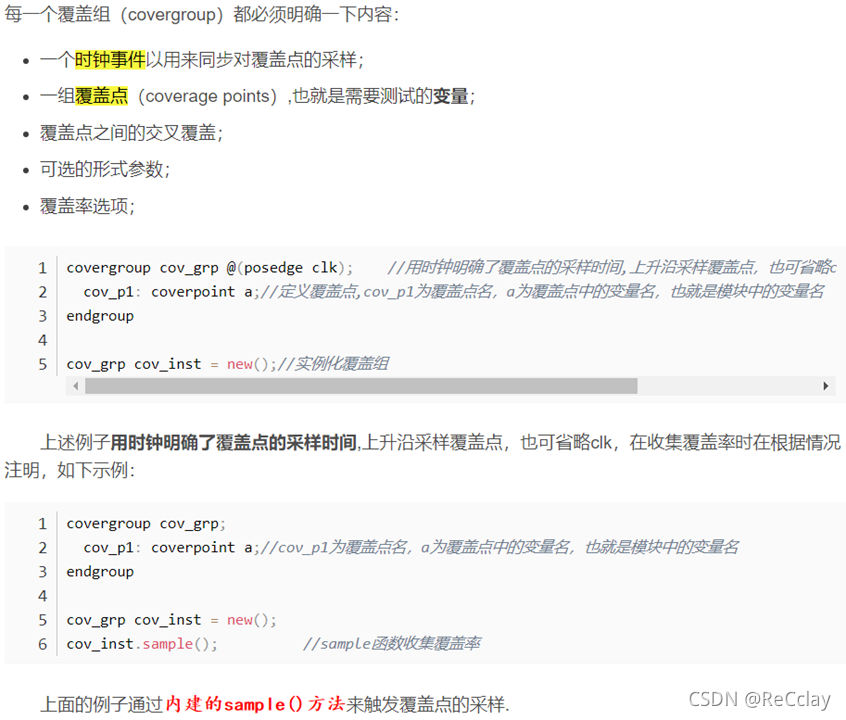

十二、定義功能覆蓋率模型

- covergroup

- 封裝覆蓋率模型的規格

- 每個covergroup包含以下內容

- 一個時鐘事件,用於同步采樣覆蓋點

- 一組覆蓋點

- 覆蓋點之間的交叉覆蓋

- 可選的形式參數

- 覆蓋率選項

- Coverfroup是用戶定義的一種結構類型

- 定義好類型之後,可以在不同的程序中多次例化

- 跟class類似,定義完成後,可以通過構造函數

new()生成covergroup的實例【OOP】 covergroup可以額定義在module,program,interface或class中- 一個

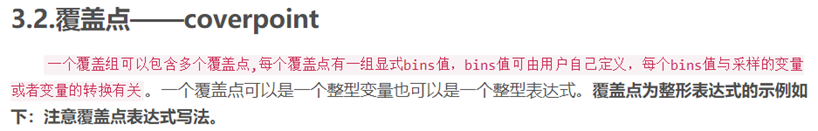

covergroup可以包含一個或多個覆蓋點- 一個覆蓋點可以是一個變量或者一個錶達式

- 每個覆蓋點有一組

bins值,這個值跟采樣的變量或者變量的轉換有關 - Bins的值可以由用戶自己定義,或者由EDA工具自動生成

- covergroup 的命名要清晰明了,通過名稱就可以確認覆蓋的功能是什麼,最好跟驗證計劃統一

// 聲明一個covergroup

covergroup cg;

….

endgroup

cg cg_inst = new;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

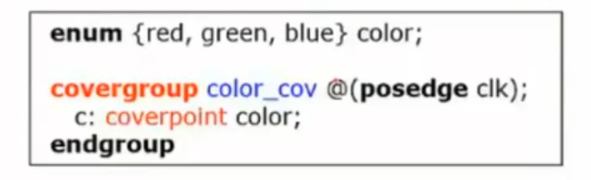

十三、功能覆蓋率的建模

- 以驗證計劃為起點,編寫可以仿真的功能覆蓋率模型

- 在驗證平臺中采樣變量和錶達式的值(

coverpoints) - 在下面的例子中,驗證平臺隨機產生端口值,驗證計劃中要求遍曆所有值

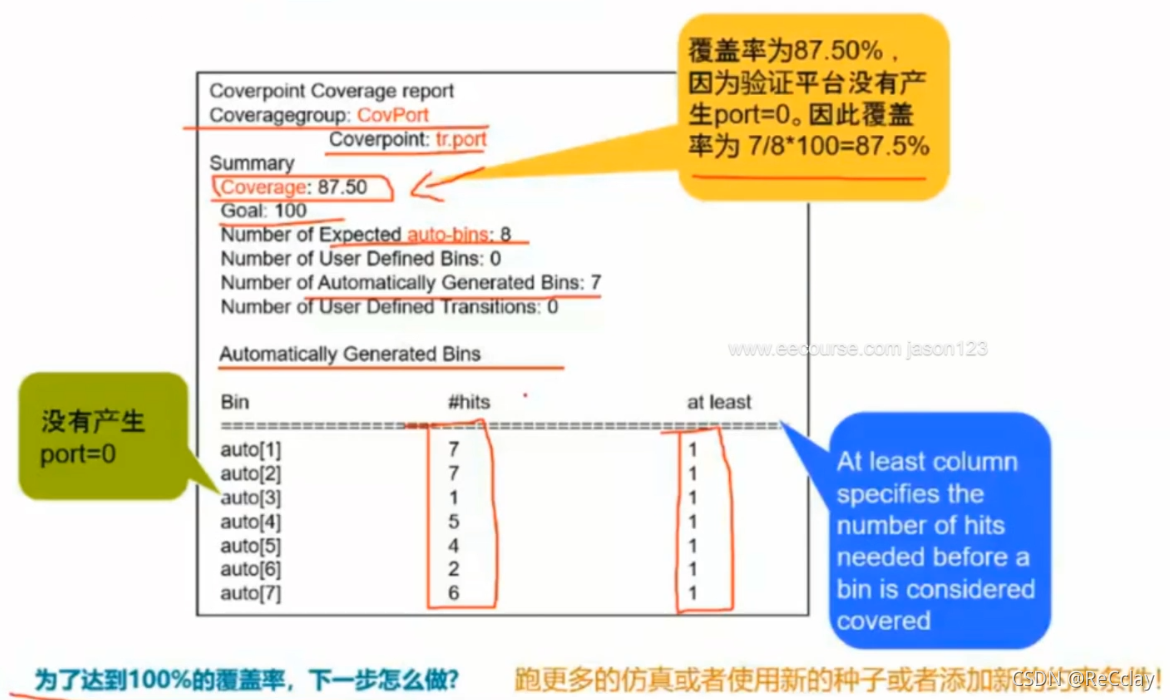

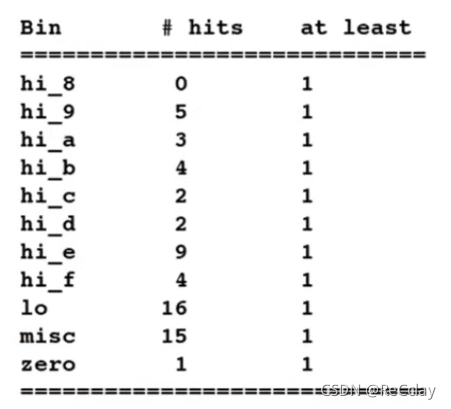

十四、功能覆蓋率報告

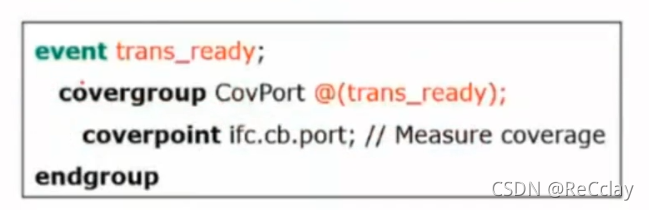

十五、功能覆蓋率的采樣事件

- 帶有event觸發的covergroup

- 當驗證平臺觸發 trans_ready 事件時,采樣CovPort

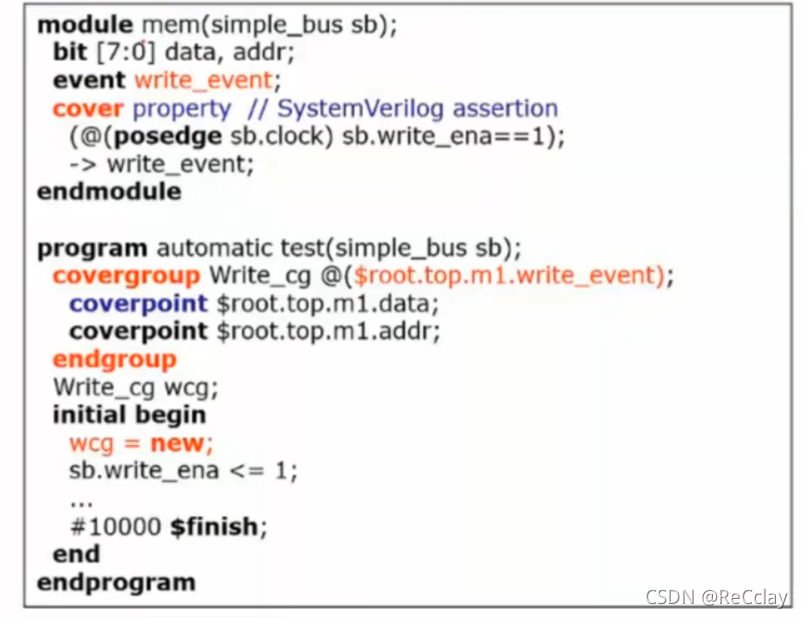

十六、功能覆蓋率:觸發SystemVerilog Assertion

十七、定義覆蓋點:信號和錶達式

采樣數據

- 如何收集覆蓋率信息?

- 在覆蓋點中指定了變量和錶達式,SystemVerilog創建了一組bins,用於記錄那些采樣到的數值

- bins是一個功能覆蓋率的衡量單比特

- 在每次仿真結束後,生成的數據庫中包含了采樣後所有的bins

- EDA分析工具可以讀取這個數據庫,生成一個覆蓋率報告,報告中包含了設計中哪一部分被覆蓋,以及總的覆蓋率數值

- 如何收集覆蓋率信息?

私有bins和總的覆蓋率

- 計算一個覆蓋點的覆蓋率,首先確認所有可能數值的總的數量

- 覆蓋率等於采樣的bins值除以總的bins的值

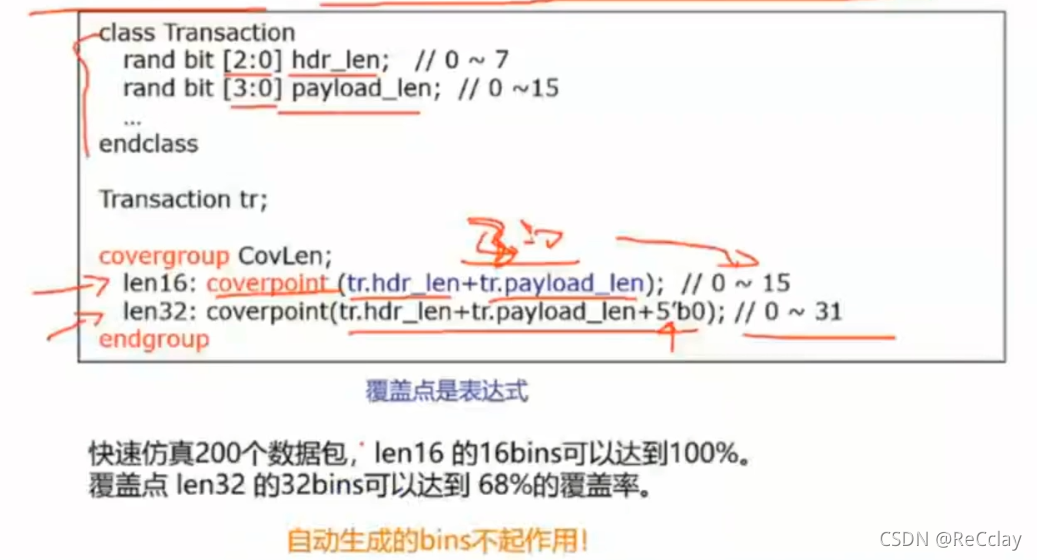

采樣錶達式

- 錶達式可以被采樣,但必須檢查覆蓋率報告,確保采樣值是正確的

注:

lens32的覆蓋率應該為:24 / 32 = 75%。範圍計算方法:hdr_len是3bit,所以一共8個組合,payload_len時4bit,所以一共16個組合。那麼,加起來一共是24個組合0-23,而總的空間是0-31即32個組合,又最後加的是5'b0故32個組合中必定有某些值達不到,所以lens32的覆蓋率為:24 / 32 = 75%

- 采樣數據:

bins- 私有bins和總覆蓋率

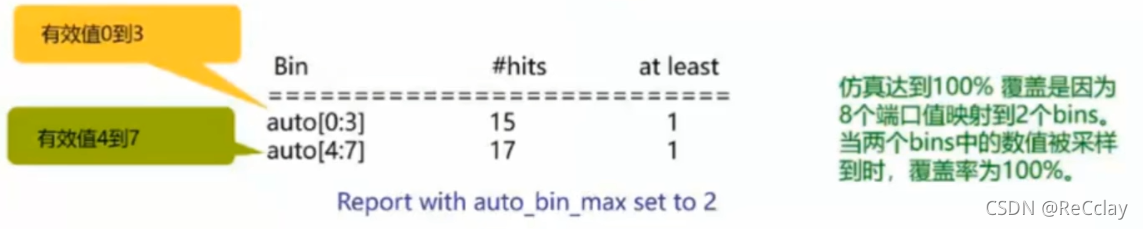

- SystemVerilog 自動為覆蓋點創建bins

- 一個N比特的錶達式有

2 N 2^N </span><span class="katex-html"><span class="base"><span class="strut" style="height: 0.841331em; vertical-align: 0em;"></span><span class="mord"><span class="mord">2</span><span class="msupsub"><span class="vlist-t"><span class="vlist-r"><span class="vlist" style="height: 0.841331em;"><span class="" style="top: -3.063em; margin-right: 0.05em;"><span class="pstrut" style="height: 2.7em;"></span><span class="sizing reset-size6 size3 mtight"><span class="mord mathdefault mtight" style="margin-right: 0.10903em;">N</span></span></span></span></span></span></span></span></span></span></span></span>個有效值</li><li>一個3bit的變量port有8有效值</li></ul> </li><li>限制自動生成的bins的數量 <ul><li>covergroup 選項<code>auto_bin_max</code>指定自動生成bins的最大數量,默認值為64bins</li></ul> </li></ul> </li></ul>

- 私有bins和總覆蓋率

注:自動生成bins這種在實際中應有的比較少!

- Q:什麼算是一個功能點?

- A:UT/BT 功能點更多聚焦模塊上下接口和時序上面;IT 對應的可能是數據流;ST 對應的可能是系統級的應用場景

- 故,功能點在不同的level驗證上分解對應的點是不太一樣的

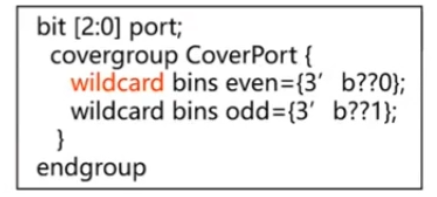

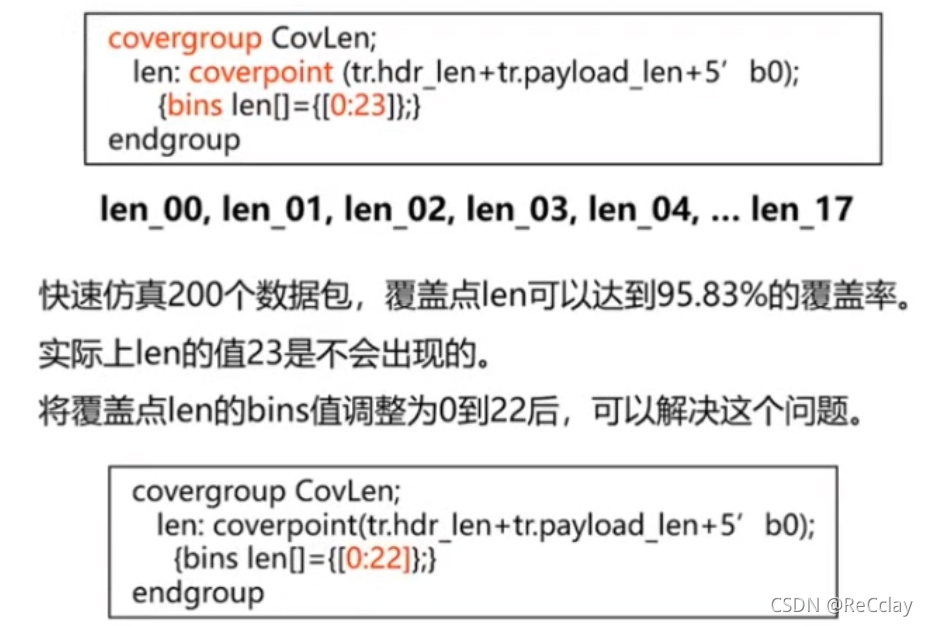

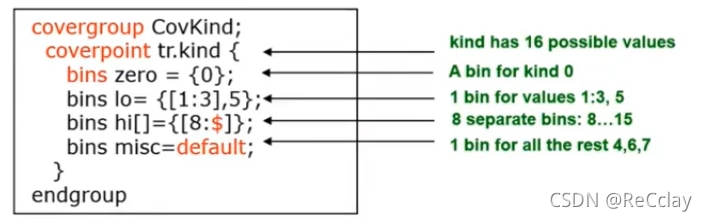

十八、定義覆蓋點:bins

- 用戶定義bins

- 顯式命名

bins可以提高精度,方便統計覆蓋率

- 顯式命名

注:為什麼23不會出現呢?hdr_len的最大值為

7,而payload_len的最大值為22,故len的最大值為22不會出現23!

- 覆蓋點bins的命名

- 定義bins時

- 用戶限制覆蓋率統計時需要的數值

- SystemVerilog 不再自動創建bins,並且忽略非用戶定義的bins值

- 只有 用戶定義的bins的值才可以用於計算功能覆蓋率

- 用戶默認bin值可能被遺忘

- 定義bins時

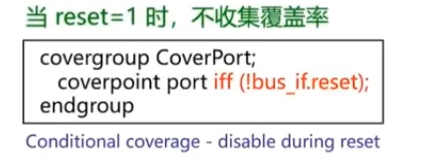

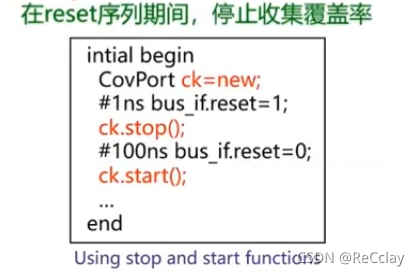

十九、定義覆蓋點:條件覆蓋

- 條件覆蓋(下述兩種用法等效)

- 使用關鍵字

iff為覆蓋點添加條件(更簡潔) - 使用

start和stop函數

- 使用關鍵字

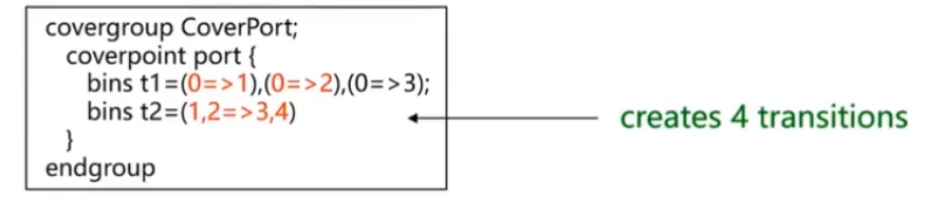

二十、定義覆蓋點:狀態跳轉覆蓋

注:上面是收集靜態的覆蓋點,下面來看看狀態切換點的覆蓋收集。

- Transition Coverage 跳轉覆蓋率

- 用戶定義覆蓋點的狀態跳轉,並收集相關的信息

- 使用

?等通配符錶示狀態和狀態跳轉

注意:上述

t2是1到3;1到4;2到3;2到4,四種跳轉情况!

注:當狀態較多時,可以使用?通配符

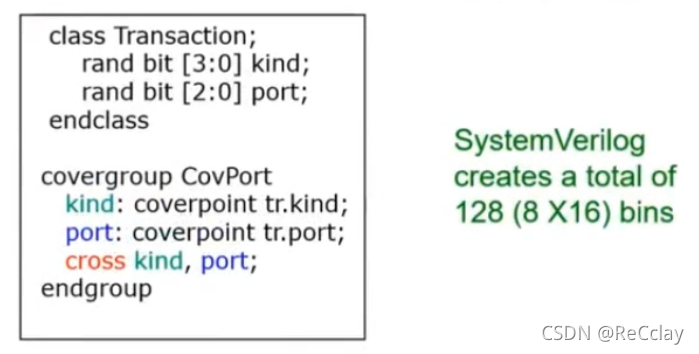

二十一、定義覆蓋點:交叉覆蓋

Cross Coverage交叉覆蓋率- 在覆蓋率組中,可以定義兩個或多個覆蓋點或者變量之間的交叉 覆蓋率

注:kind 一共

16種組合,port一共8種組合,交叉一共有16x8=128種組合

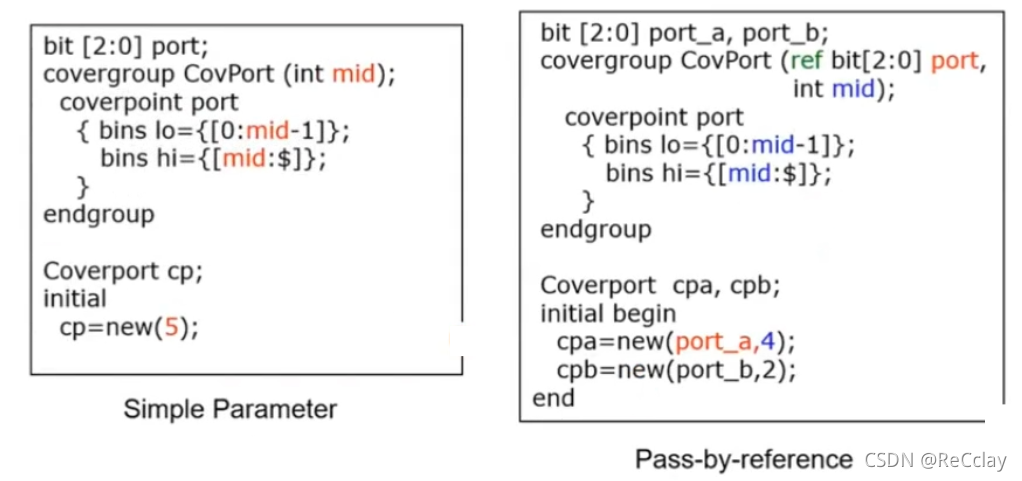

二十二、參數化的覆蓋率:提供代碼的重用性

- 參數化的covergroup

- SystemVerilog 允許創建參數化的covergroup,便於創建通用的定義

二十三、covergroup實戰補充(2021-10-15)

二十四、小結

- 基於覆蓋率驅動的驗證技術

- 為什麼是基於覆蓋率驅動?整個驗證需要看驗證進度,需要覆蓋率這個可以量化的標准可以看到進展。功能覆蓋率一般是100%,代碼覆蓋率接近100%(條件覆蓋率需要根據具體的電路類型,一般來講很難達到100%,需要根據不同的代碼來定)。總之做驗證計劃的時候有一個覆蓋率目標,達到覆蓋率目標,才算達到我們的要求!另外需要强調一點,並不是說達到覆蓋率我們的驗證就OK了,達到覆蓋率後,需要去看比如缺陷的情况等。如果覆蓋率ok,但缺陷仍持續很高,此時並不能證明驗證是收斂的!另外一點,功能覆蓋率是驗證人員自己來寫的,主觀寫的話,一開始可能就寫的不全,故即便達到100%,也不能說所有的功能就覆蓋掉了!因為本身可能寫的覆蓋率場景本身就沒有cover到,故整個過程需要做多輪的迭代來完成。

- 總之,記住幾個點。1、覆蓋率是用來衡量驗證進度的標值。2、體現在驗證計劃中,在驗證一開始需要體現一個覆蓋率目標。

- 覆蓋率類型:代碼覆蓋率和功能覆蓋率

- 代碼覆蓋率是一種根據代碼描寫結構去客觀的工具自動收集的覆蓋率;功能覆蓋率是驗證人員根據我們要驗的功能規格從規格設計書作為一個入口來分析我們要驗的DUT有哪些功能,然後把這些功能點寫出來!

- 代碼覆蓋率達到要求並不代錶功能達到要求!如果代碼覆蓋率都沒達到要求,那麼肯定驗證是不完備的。

- SV中的功能覆蓋率建模

- 定義覆蓋率模型:covergroup

- 定義覆蓋點:coverpoint

- 覆蓋點的 bins(類似約束限定範圍,還有條件覆蓋、交叉覆蓋、transition覆蓋(隨著時間的延續的覆蓋))

- 覆蓋率函數(傳遞參數)

X、實踐練習

X.1、編寫源代碼

修改Makefile,由於我們需要看覆蓋率,所以需要在Makefile中添加dve工具相關的命令。

Makefile

comp_file = ;

all: comp run dve_cov

comp:

vcs -full64 -sverilog -debug_all -timescale=1ns/1ps $(comp_file) -l comp.log

run:

./simv -l $(comp_file).log

dve_wave:

dve -vpd vcdplus.vpd &

dve_cov:

dve -full64 -covdir simv.vdb

log:

sed '/^[^*].*/d' $(comp_file).log > rslt.log

open:

gvim rslt.log

clean:

rm -rf csrc simv* *.log ucli.key

dve_wave在後面的SVA會用到,現在暫時用不到- 更改

all為:comp run dve_cov dve_cov是我們收集覆蓋率要用到的

cov_demo.sv

module cov_demo();

class transaction;//激勵

rand bit [31:0] data;

rand bit [2:0] port;

/* constraint data_c1{

data inside{

[0:100], [101:9999], [10000:12000]};

} */

endclass

covergroup cov_grp;

cport : coverpoint tr.port;

cdata : coverpoint tr.data;

/* cdata : coverpoint tr.data {

bins min = {

[0:100]};

bins mid = {

[101:9999]};

bins max = {

[10000:$]};

}*/

endgroup

transaction tr = new;

cov_grp ck = new;

initial begin

repeat(32) begin//重複次數

tr.randomize;//發送激勵

ck.sample();//采集覆蓋率

end

end

endmodule

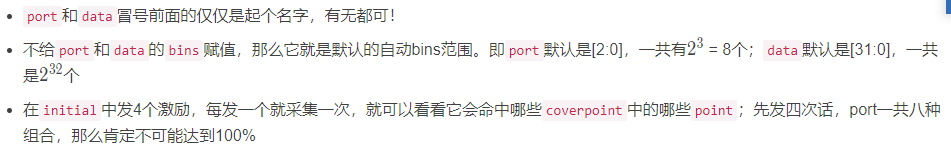

port和data冒號前面的僅僅是起個名字,有無都可!

X.2、運行源代碼

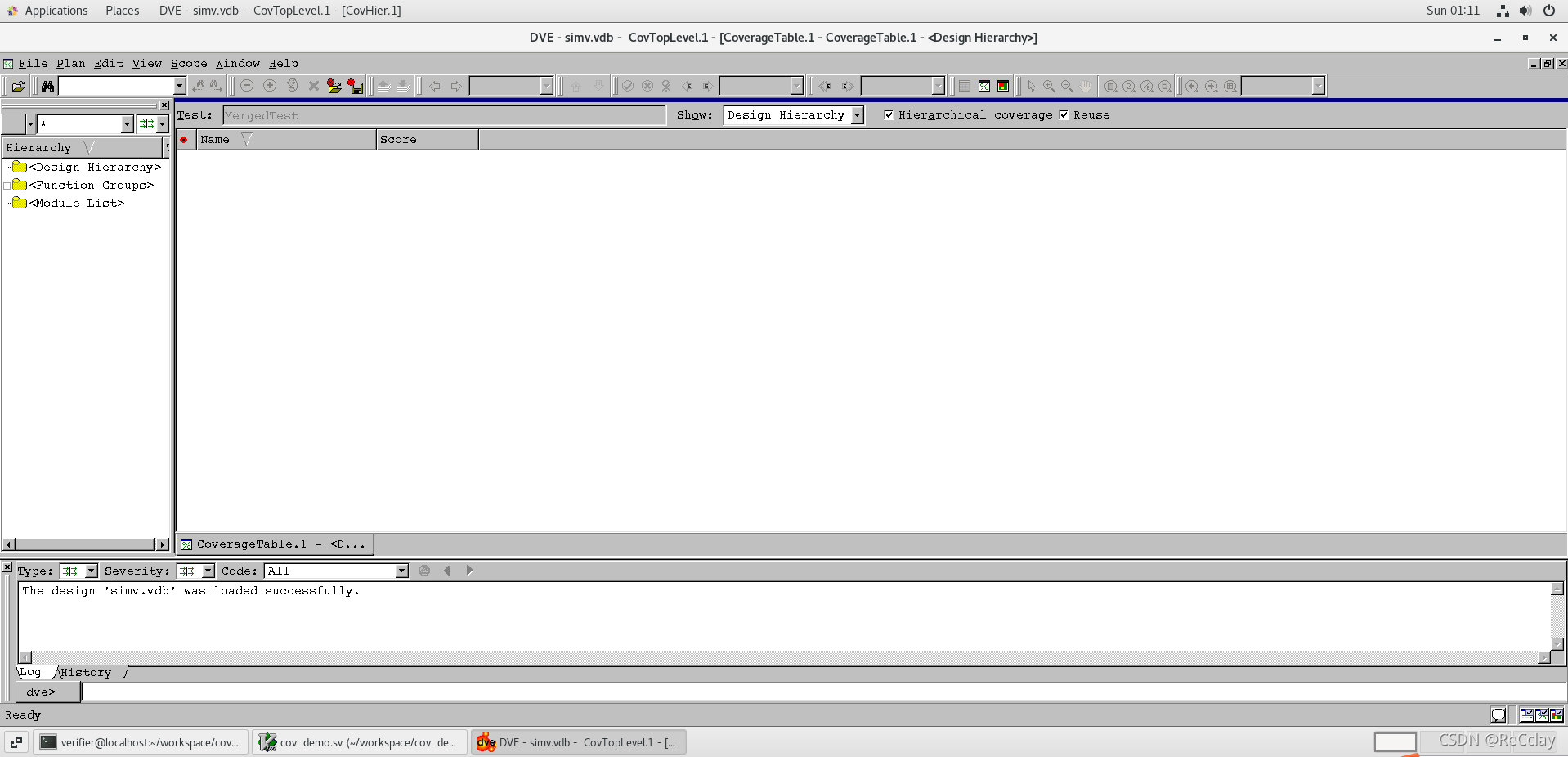

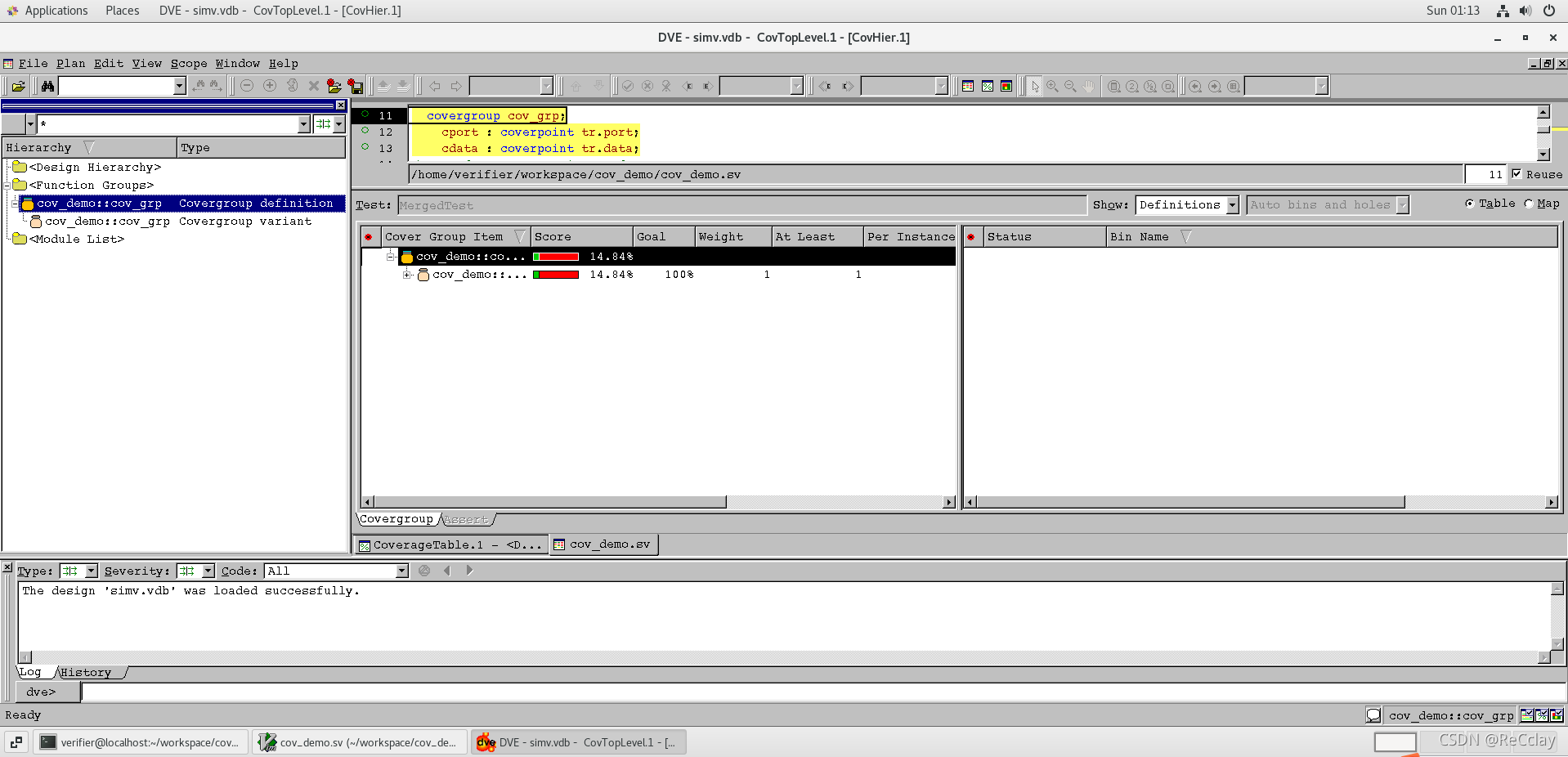

執行make comp_file=cov_demo.sv會自動編譯運行並彈出DVE窗口以供我們查看覆蓋率!

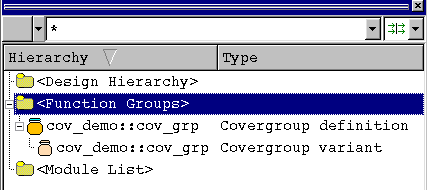

點擊左側的<Function Groups>的+展開該選項,而後雙擊cov_demo::cov_grp Covergroup definition

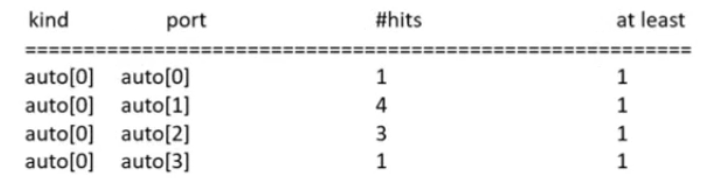

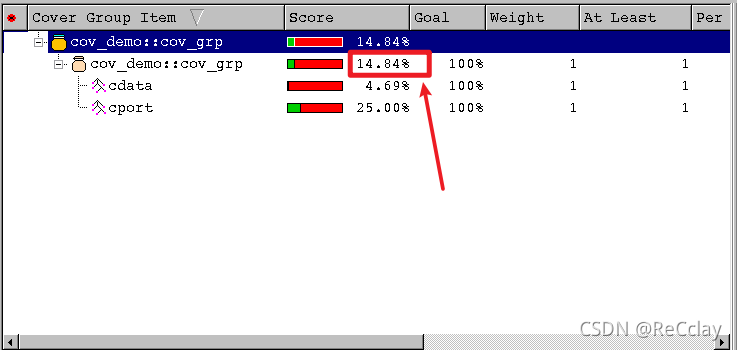

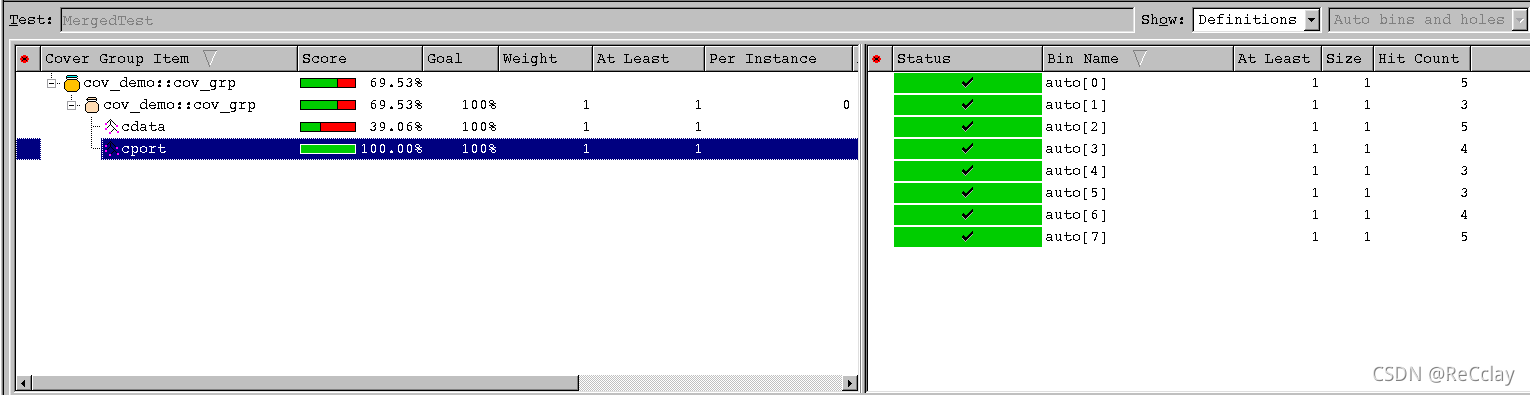

在右側串口可以看到cov_demo::cov_grp對應的覆蓋率只有14.84%,這是很低的!可以繼續點擊其下的cdata和cport在右側會看到變量的哪些覆蓋了,哪些沒有覆蓋。如下圖:

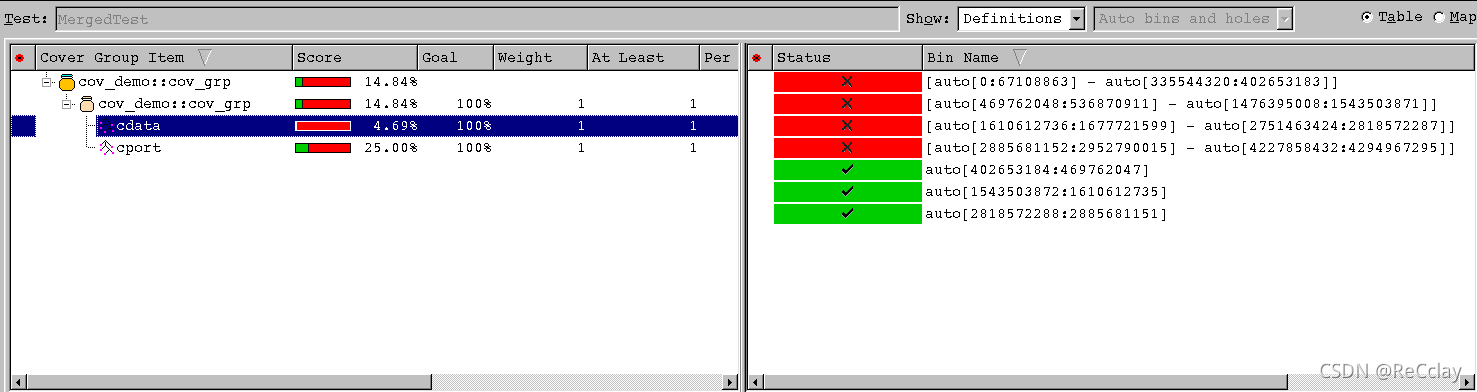

注:由於使用的是默認的bins,所以這裏標識的是

auto。auto bins的情形下,bins的分類特別多,覆蓋率特別低!

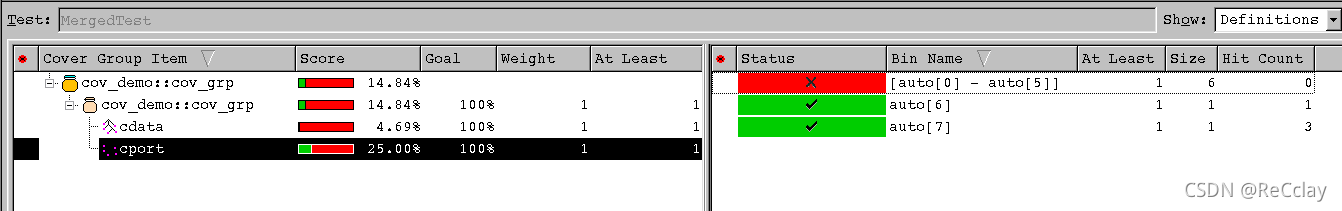

從下圖不難看出,cport覆蓋率為25%,在右側可以看到具體覆蓋信息,6和7個命中了1次和3次,還有0-56個值沒有被覆蓋,所以覆蓋率為2/8=0.25。

上述實驗中,我們僅僅repeat了4次,導致命中的範圍變小,覆蓋率只有25%也是情理之中。接下來我們修改repeat改為32,增加次數,可以擴大命中範圍,也就是cport和cdata變量的覆蓋率也會增加!

點擊右上角關閉DVE,修改源代碼中的repeat參數,並重新運行Makefile脚本。

運行結果如下圖,可以看到總體覆蓋率為69.53%,顯著提昇。其中cport的8種情况全部覆蓋,所以覆蓋率為100%!

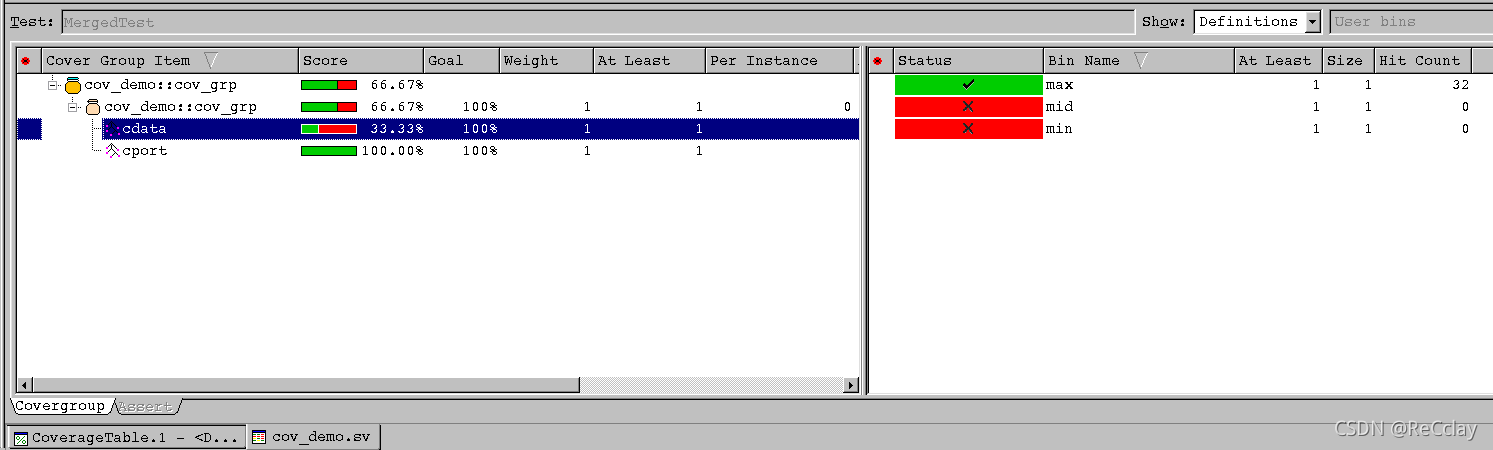

接著我們使用自定義bins,取消14-18行注釋,並把第13行注釋。這裏是將data分為了三類,拿第一類min舉例來說,只要出現0~100中的任意一個數,就算命中min,就算一個等價的測試點!比如產生一個50,那麼就意味著0~100這樣一個範圍就已經測試過了!

如下圖,可以看到cdata只覆蓋了max,對於mid和min並沒有進行覆蓋,這個時候我們只能去調整隨機激勵的約束,讓他產生中間值和小值!

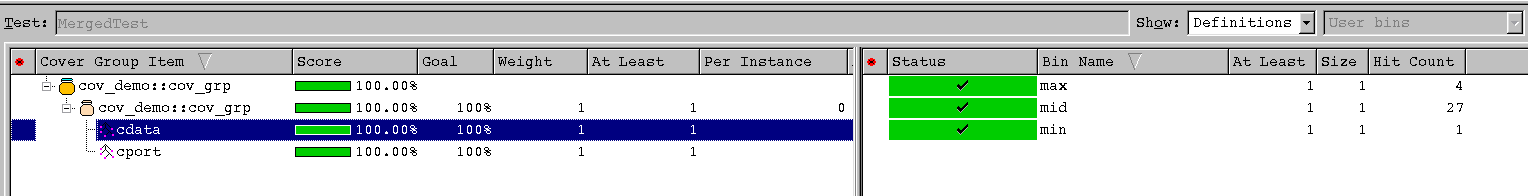

取消掉第6-8行注釋,實現對data的範圍進行約束。重新便於DVE,運行Makefile脚本,可以看到cdata的覆蓋率和整體覆蓋率均達到了100%!

注:如果某一類沒有覆蓋到,我們就可以將約束改小,單獨的去覆蓋它。這裏給我們一個啟示,可以跑多個用例,每個用例跑多個範圍,那麼這樣的話最終merge,data的覆蓋率就可以達到100%了!

边栏推荐

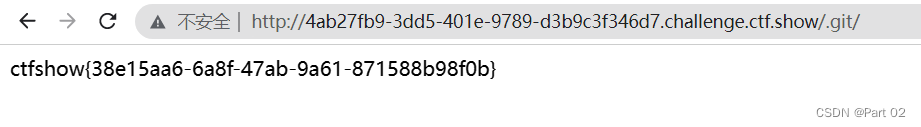

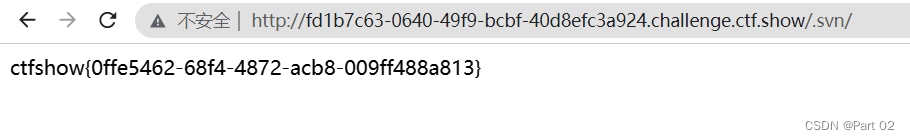

- Ctfshow, information collection: web8

- 最安全的证券交易app都有哪些

- jacoco代码覆盖率

- Introduction of mongod management database method

- Wechat applet 01

- [机缘参悟-40]:方向、规则、选择、努力、公平、认知、能力、行动,读3GPP 6G白皮书的五层感悟

- Connecting FTP server tutorial

- 2022年5月互联网医疗领域月度观察

- 【目标检测】YOLOv5跑通VOC2007数据集

- Guangzhou Development Zone enables geographical indication products to help rural revitalization

猜你喜欢

Guangzhou Development Zone enables geographical indication products to help rural revitalization

Novel Slot Detection: A Benchmark for Discovering Unknown Slot Types in the Dialogue System

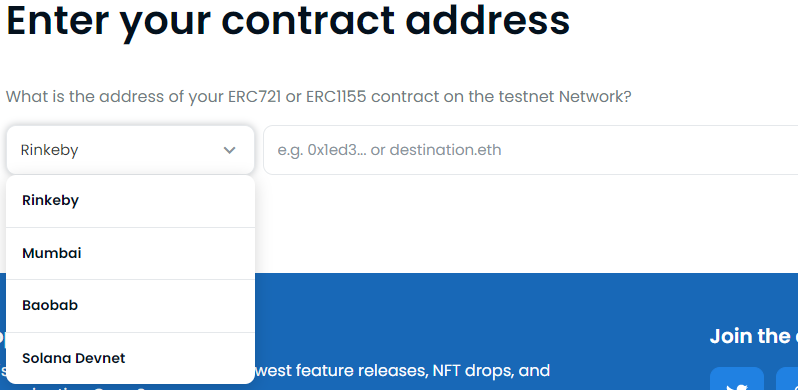

How to release NFT in batches in opensea (rinkeby test network)

#HPDC智能基座人才发展峰会随笔

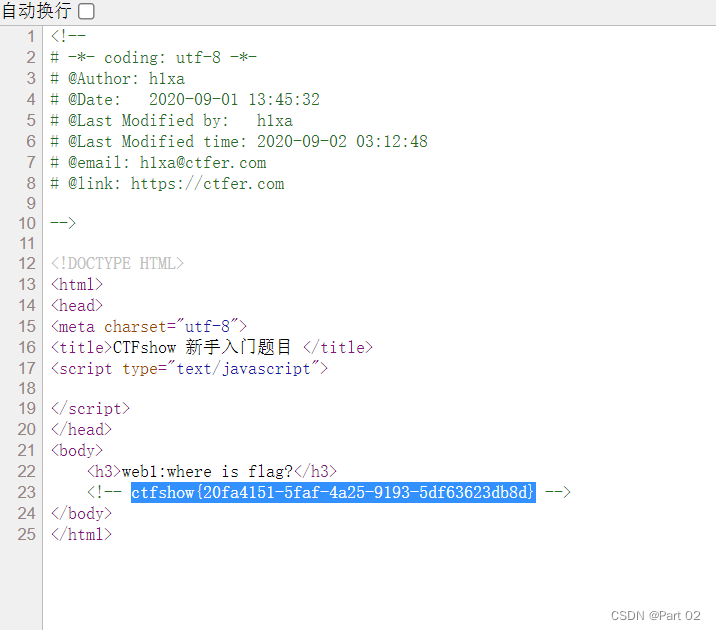

Ctfshow, information collection: web1

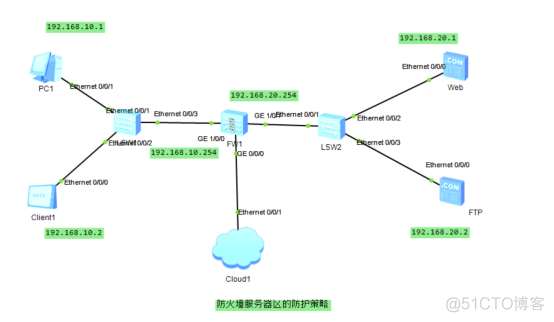

Protection strategy of server area based on Firewall

Configure mongodb database in window environment

IDA pro逆向工具寻找socket server的IP和port

Ctfshow, information collection: web7

Ctfshow, information collection: web8

随机推荐

Do you know the relationship between the most important indicators of two strong wind control and the quality of the customer base

Niuke real problem programming - Day9

Ctfshow, information collection: web6

CTFshow,信息搜集:web2

众昂矿业:萤石继续引领新能源市场增长

[server data recovery] a case of RAID data recovery of a brand StorageWorks server

2.Golang基础知识

2022全开源企业发卡网修复短网址等BUG_2022企业级多商户发卡平台源码

8大模块、40个思维模型,打破思维桎梏,满足你工作不同阶段、场景的思维需求,赶紧收藏慢慢学

【深度学习】图像超分实验:SRCNN/FSRCNN

Pit avoidance: description of null values in in and not in SQL

Ctfshow, information collection: web5

[Data Mining] Visual Pattern Mining: Hog Feature + cosinus Similarity / K - means Clustering

Ctfshow, information collection: web8

Promoted to P8 successfully in the first half of the year, and bought a villa!

Niuke real problem programming - day14

【目标检测】YOLOv5跑通VOC2007数据集

Basic knowledge sorting of mongodb database

大表delete删数据导致数据库异常解决

Notes HCIA