当前位置:网站首页>[The Art of Hardware Architecture] Study Notes (1) The World of Metastability

[The Art of Hardware Architecture] Study Notes (1) The World of Metastability

2022-08-04 14:16:00 【Linest-5】

目录

1.3.1 Using multi-stage synchronizer

1.3.2 Use the clock frequency doubling circuit multistage synchronizer

1.6 Metastable comprehensive advice

写在前面

This blog series is about the recent books《硬件架构的艺术》的读书笔记,Most of the content is copied content of the book,Are a few notes,Understanding of the book part knowledge and develop(有标注).

1. 亚稳态

1.1 什么是亚稳态?

在之前的文章中有介绍,Direct call link.

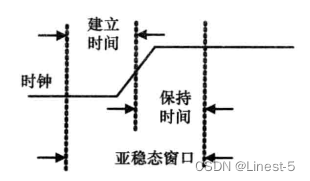

1.2 亚稳态窗口

亚稳态窗口( Metastability Window) With a certain length of time,During this time the input signal and the clock should remain the same.如果它们发生变化,The output is likely to become metastable.如下图所示,Establish and keep time to the width of the metastable window.

窗口越大,To enter the higher the probability of metastable.在大多数情况下,A new logic devices will have smaller metastable window,Also means that the device into the metastable probability will be smaller.

Metastable window can be seen as need stable data length,So you need to stabilize the longer the length of the data,The more difficult it is to meet the requirements,Also the easier it is to appear metastable.

1.3 避免亚稳态

如上面所述,Whenever violation to establish、Keep the time,Metastable will appear.在以下条件中,The signal may violate timing requirements.

- 输入信号是异步信号.

- 时钟偏移/摆动(上升/下降时间)高于容限值.

- Signals in two different frequency or the same frequency but different phase and migration of the clock domain under the clock domain work.

- Combination delay trigger data input in metastable window change.

Metastable can cause excessive propagation delay and system fault,All my triggers and register in the metastable.Although the metastable ineradicable,但是可以减小亚稳态发生的概率.

在最简单的情况下,Designers can be make sure clock cycle is long enough to avoid the metastable,This clock cycle should be greater than the resolution time of quasi steady state,Than to the next level also trigger any logical path delay.虽然这种方法简单,But under the performance requirements of most modern design is not practical.Another method to avoid metastable is the use of synchronizer.

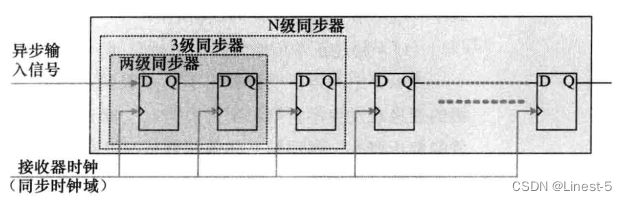

1.3.1 Using multi-stage synchronizer

Avoid metastability is the most common method in the clock domain signal with one or more of the synchronous trigger,如下图所示.This method with a complete clock cycles to solve the first level of synchronization trigger metastable problem(Do not include secondary settling time of the trigger).But this way increases the observation of synchronization logic input delay.

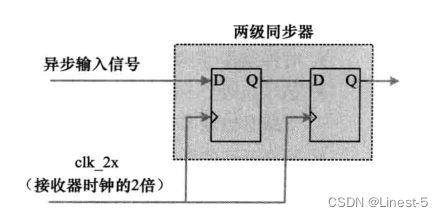

1.3.2 Use the clock frequency doubling circuit multistage synchronizer

Multistage synchronizer is a limitation of the system will take a long time to respond to asynchronous input.Solution to this problem is to use frequency doubling the clock as two synchronous trigger clock input.Altera 的 FPGA In this called a clock frequency doubling technique.

This method not only can let the system within a system clock cycle in response to an asynchronous input,And improve theMTBF.Although the frequency doubling the clock can reduceMTBF,But the influence caused by more than two levels of the trigger offset.Both methods can't guarantee synchronizer halt the spread of metastable down,They only reduce the incidence of the metastable.

Using frequency doubling the clock here because with fast clock to slow sampling clock is able to complete the data collection of the,There will be no missing problem,Does not necessarily need double frequency doubling,Faster than the source clock can be,General data from slow clock domain across to fast clock domain,Solutions are using the two pat,Also is to use two levels of synchronizer.

1.4 亚稳态测试电路

Whenever the trigger sampling an asynchronous input,Trigger output is likely to result in an unpredictable delays,Although the probability is very low.This will not only lose people violate established、Hold time requirements occur,And the trigger to receive new input this could happen within a short period of time sequence window.在这些情况下,The trigger in metastable.

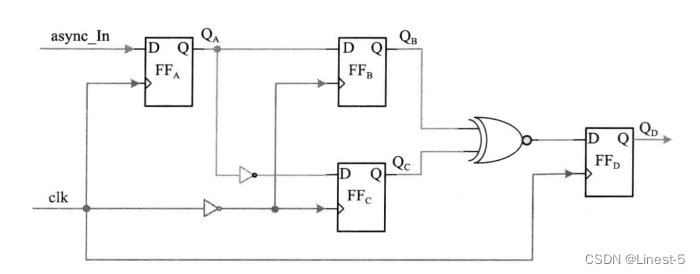

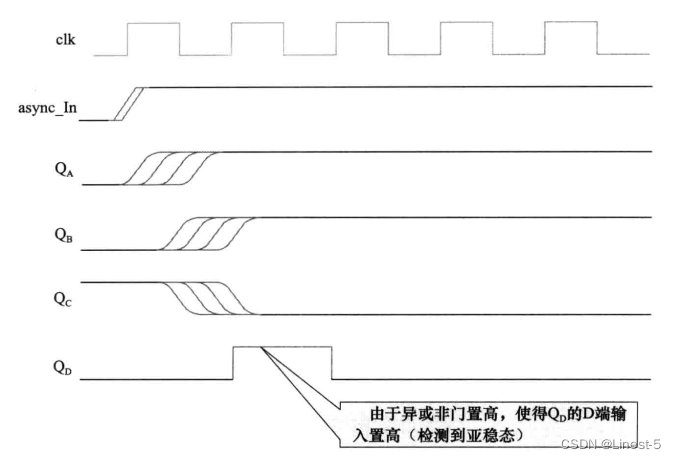

图1.8Described in the test circuit can be used to determine the trigger metastable characteristics.Picture below shows the has an asynchronous input“async_ jin” 的触发器“FF", Again by the clock "clk"的上升沿触发.Shown in the picture below the trigger“FFp”和“FFc”All along the trigger in clock down,The idea is to captureFFThe metastable events.

When two complementary signal is passed to the“FFB” 和“FFC”的输入时,无论“FFA”The occurrence of metastable events when,异或非( XNOR)The output of the gate will become a high level.在触发器“FF.” Output capture the high level that has been detected metastable events.

All the nodes in the test circuit sequence as shown in the figure below.

For parsing the trigger(“FFB" 和“FFc") Triggered by falling edge clock,So can change the clock time high level(Δt)Required to control the stability of the time.稳定时间tmet由下式确定

tmet =Δt - tACN

式中,tscNIs the minimum clock period,等于tco (FFAThe clock to the output delay) + Parsing the trigger(FFg 或FFc)的建立时间tsu.

Reduce the resolution time or one way is to establish a stable time/Retention time of the data set to join shaking.

Exclusive or non logic is as follows

相同为 1,不同为 0,在 FFA The output will pass through an inverter output to FFC,如果正常的话,输入到 FFB 和 FFC The values are the opposite,If the metastable two output will become,Which leads to different or the output for 1,So that you can achieve detection circuit is a metastable.

A | B | OUT |

0 | 0 | 1 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 1 |

1.5 The type of synchronizer

An asynchronous input circuit MTBF And the time for recover from metastable exponential relationship.With synchronizer of buffer time can help to recover from metastable.

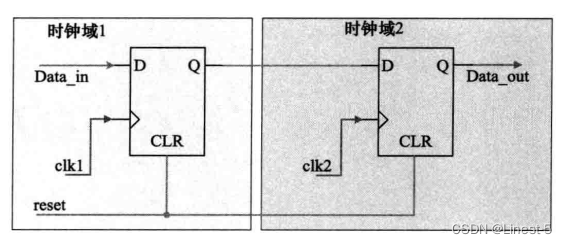

要注意,Should not be an asynchronous signal by two or more synchronizer synchronization( Doing so will the risk of multistage synchronizer output produce different signals).This section describes two levels of synchronizer pattern of two different:模式A和模式B.

模式AIs a standard circuit,When an asynchronous input signal is much large than the clock cycle is the most effective.

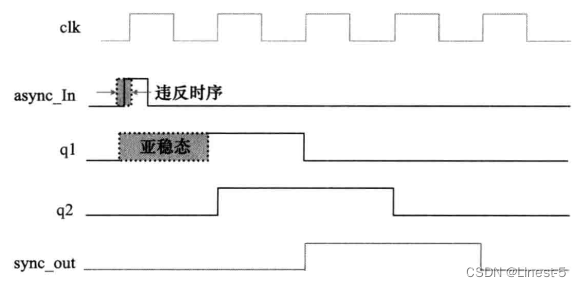

注意,Even if the asynchronous input outside establish a time interval stability,It still needs to be generated by the clock drive two cycles of delay,否则 FF1 May in metastable.

If the metastable in less than one clock cycle to parse the,FF2 There will be a stable input,Otherwise you need deeper cascade.

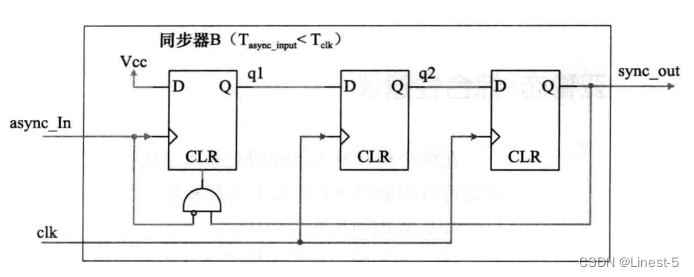

但是,模式ACannot be used in asynchronous input signal is less than the width of the clock cycle.In this case to adopt mode B,如图所示.

注意,For synchronizer mode B,The first level trigger input D 与 Vcc 相连,At the same time the clock signal is asynchronous input signal.The other two trigger directly by the system clock(clk) 控制.A short pulse let q1 变成高电平,This high level after two clock(clk) After the from sync__out 输出.

The rules are summarized

- When the signal must work across the clock domain,To adopt synchronizer.

- 如果 clk1

个人理解是:If you need to across the width of the clock domain data is much bigger than the clock,则使用模式 A,If the data width is smaller than the clock,Use at this time with a clock go to pick words will result in lost data sampling part,At that time the mode B 进行同步,According to the previously learned knowledge can know,也可以使用 FIFO Or handshake mechanism of the clock domain data processing.

1.6 Metastable comprehensive advice

In the border of two asynchronous system steady state is inevitable.But the following Suggestions can reduce the incidence of the metastable.

- Using synchronizer.

- Adopt more responsive trigger(Shorten the metastable windowTw).

- Use of metastable hardening trigger(Designed for high broadband and reduce input circuit and optimization for clock domain sampling time).

- Using the cascade trigger(两个或者多个)As a synchronizer.If the metastable failure probability of a trigger forP,那么NA trigger of metastable failure rate isP".

- Reduce the sampling rate.

- 避免使用dV/dtLow input signal.

边栏推荐

猜你喜欢

【 HMS core 】 【 Media 】 online video editing service 】 【 material can't show, or network anomalies have been Loading state

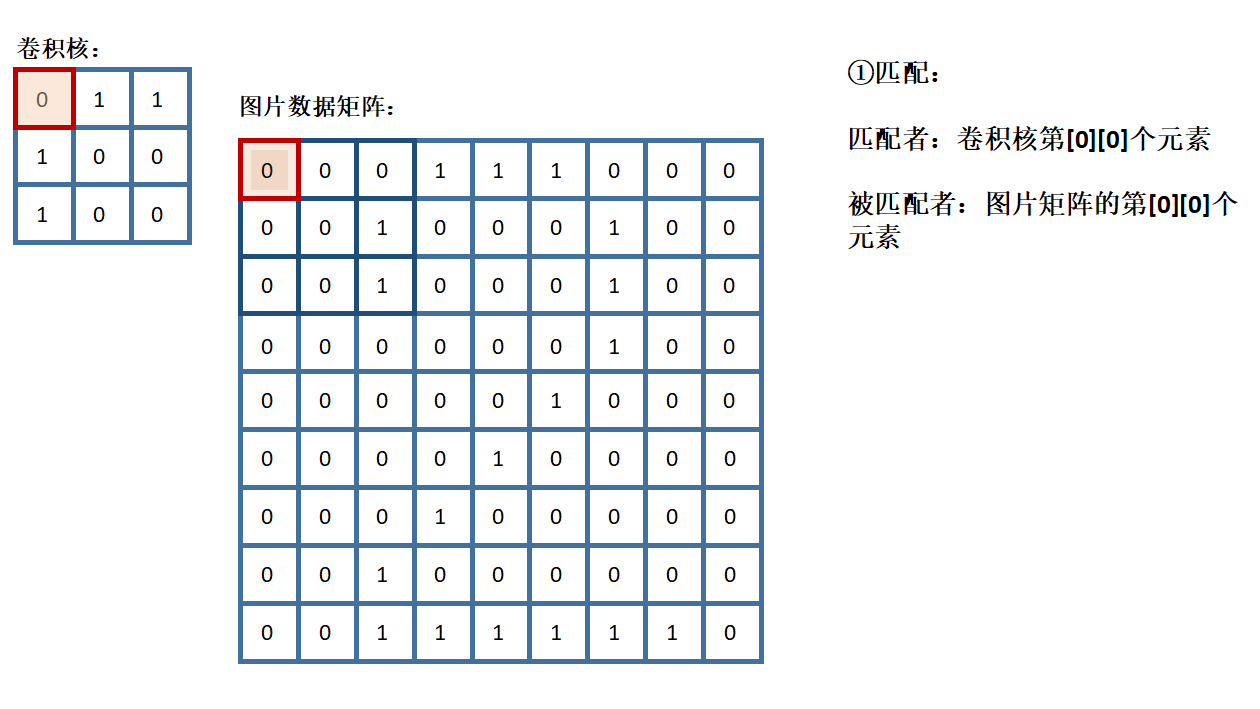

Convolutional Neural Network Basics

State security organs conduct criminal arrest and summons review on Yang Zhiyuan, a suspect suspected of endangering national security

四平方和,激光炸弹

MPLS experiment

ICML 2022 | 图神经网络的局部增强

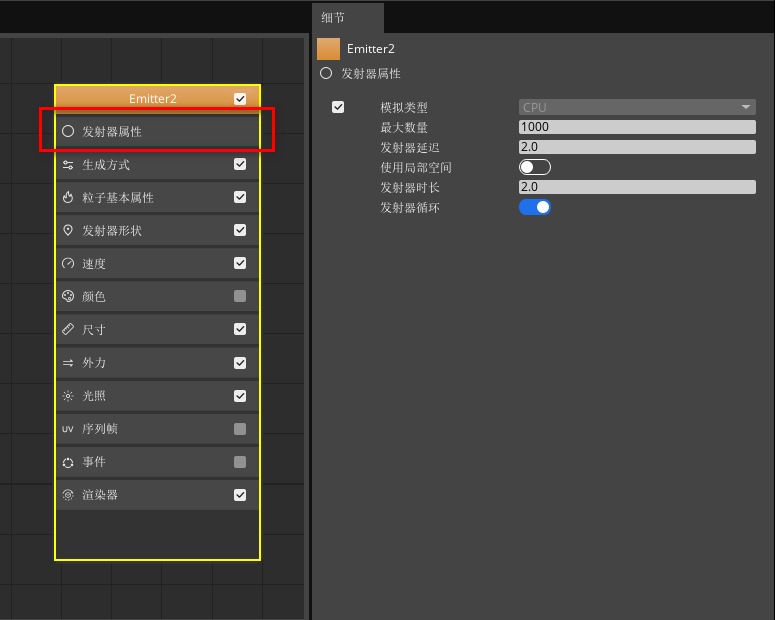

手搓一个“七夕限定”,用3D Engine 5分钟实现烟花绽放效果

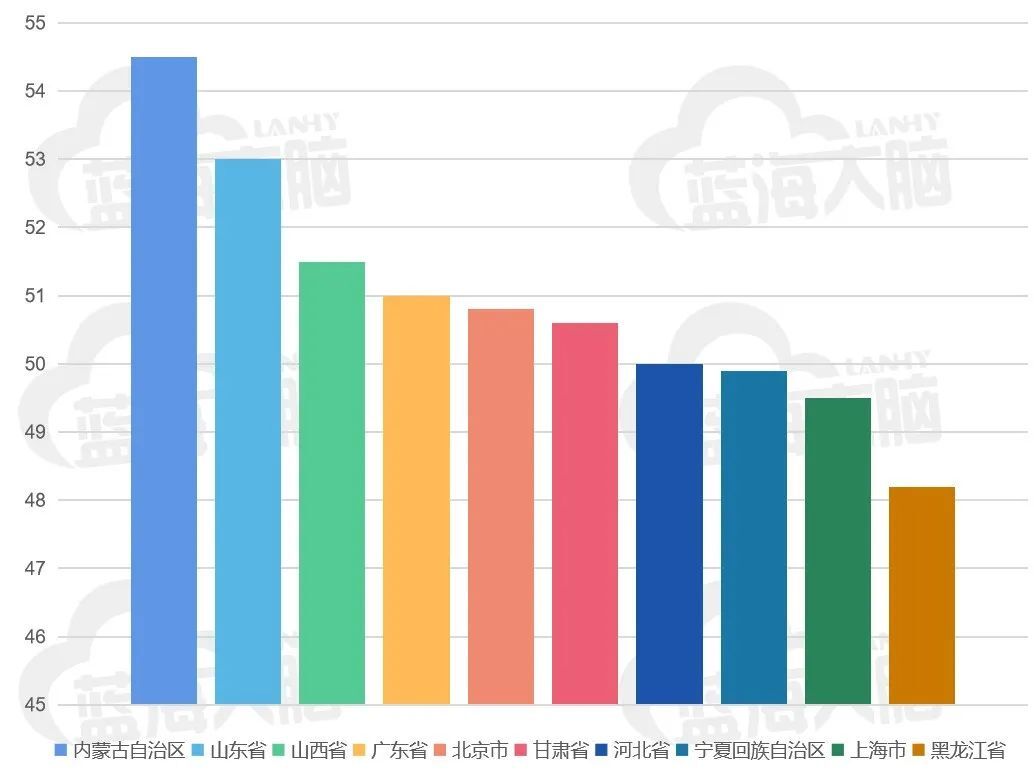

《中国综合算力指数》《中国算力白皮书》《中国存力白皮书》《中国运力白皮书》在首届算力大会上重磅发出

企业应当实施的5个云安全管理策略

南瓜科学产品升级 开启益智探索新篇章

随机推荐

南瓜科学产品升级 开启益智探索新篇章

SLAM 04.视觉里程计-1-相机模型

NPDP|作为产品经理,如何快速提升自身业务素养?

B.构造一个简单的数列(贪心)

阴影初始化【5】

世间几乎所有已知蛋白质结构,都被DeepMind开源了

化算力为战力:宁夏中卫的数字化转型启示录

Theory 1: Deep Learning - Detailed Explanation of the LetNet Model

xampp安装包含的组件有(php,perl,apche,mysql)

leetcode 48. Rotate Image (Medium)

Keycloak 6.0.0 正式发布,身份和访问管理系统

Rust 从入门到精通04-变量

数据库的基本概念

四平方和,激光炸弹

人像分割技术解析与应用

字符串类的设计与实现_C语言字符串编程题

记录都有哪些_js常用方法总结

【硬件架构的艺术】学习笔记(1)亚稳态的世界

1375. 二进制字符串前缀一致的次数-前序遍历法

Set partition minimum difference problem (01 knapsack)