当前位置:网站首页>Start from the bottom structure to learn the customization and testing of FPGA --- Xilinx ROM IP

Start from the bottom structure to learn the customization and testing of FPGA --- Xilinx ROM IP

2022-07-02 23:03:00 【Lonely single knife】

List of articles

2、ROM IP Customization of nuclear power

3、ROM IP Example and simulation test of

3.1、 Exemplify a ROM IP nucleus

Series catalog and portal

《 Start with the underlying structure FPGA》 Directory and portal

Customizing one RAM IP Before nuclear , It is strongly recommended that you read :

Start with the underlying structure FPGA----RAM IP Introduction to nuclear and key parameters

Start with the underlying structure FPGA----Xilinx RAM IP Customization and testing of

In the above two articles , Have been to RAM IP The key factors of nuclear are explained in detail , Also on RAM IP We made a customization and test for the instantiation of .

1、 What is? ROM?

In this paper, we introduce a new method in FPGA Storage classes commonly used in development IP nucleus ——ROM How to use .

ROM Read only memory (Read-Only Memory) For short , It is a solid-state semiconductor memory that can only read out the data stored in advance . Its characteristic is that once the data is stored, it can no longer be changed or deleted , And the data will not disappear because the power is turned off . And in fact FPGA Pass through IP Nucleated ROM or RAM All the calls are FPGA Inside BRAM resources , Power down content will be lost ( It's also easy to explain ,FPGA There is no power down nonvolatile memory unit inside the chip ).

use IP Nucleated ROM The module just adds data files in advance (.coe Format ), stay FPGA At run time, data files are sent to ROM Module initialization , So that ROM The module is like a “ real ” Power down nonvolatile memory ; That's why ,ROM The contents of the module must be written in the data file in advance , Cannot modify... In a circuit .

Simply speak ,RAM Is a writable 、 Readable IP nucleus ; and ROM Just a readable but not writable IP nucleus . So you can put ROM As one is “ Youth version ” Of RAM, It only has RAM Read function of . in fact , stay xilinx Of FPGA In development ,RAM And ROM All of them are used BRAM Resource realization ( customized IP It's the same ), But the external interface encapsulation is different .

stay RAM IP chapter , We know RAM There are three forms of :

- Single port RAM(Single-port RAM)

- Simple double mouth RAM(Simple Dual-port RAM, Also called pseudo dual port RAM)

- What a double mouth RAM(True Dual-port RAM)

that ROM There are several forms of composition ?

It's not hard to infer , Single port ROM It must be possible , That is, one port to read . So double port ROM Will there be two ? Can't , because ROM The read-only but not write feature is doomed to have only one kind of double port ROM, That is, both ports are readable ROM. as follows :

- Single port ROM(Single-Port Rom)

- Dual port ROM(Dual-Port ROM)

(1) Single port ROM: Write operation cannot be realized , Only one port can be used for reading

(2) Dual port ROM: Write operation cannot be realized , Two ports can be used for reading , The bit width of the read data of the two ports can be different , But it must be an integer multiple

2、ROM IP Customization of nuclear power

ROM IP Customization and RAM IP The customization process of the core is very similar , But there are fewer parameters to focus on , So the implementation is simpler . Next, we will show how to customize a bit width 4bit, depth 16 Single port ROM The process of .

Get ready

- Create a new one ROM After the project, click the arrow IP Catalog

- It will appear after clicking IP Catalog page , stay IP Search in the search box of the kernel block

- According to the screening sequence , Double click the arrow RAM & ROM nucleus “Block Memory Generator”, After double clicking, the configuration interface will appear

①、 first page

②、 The second page

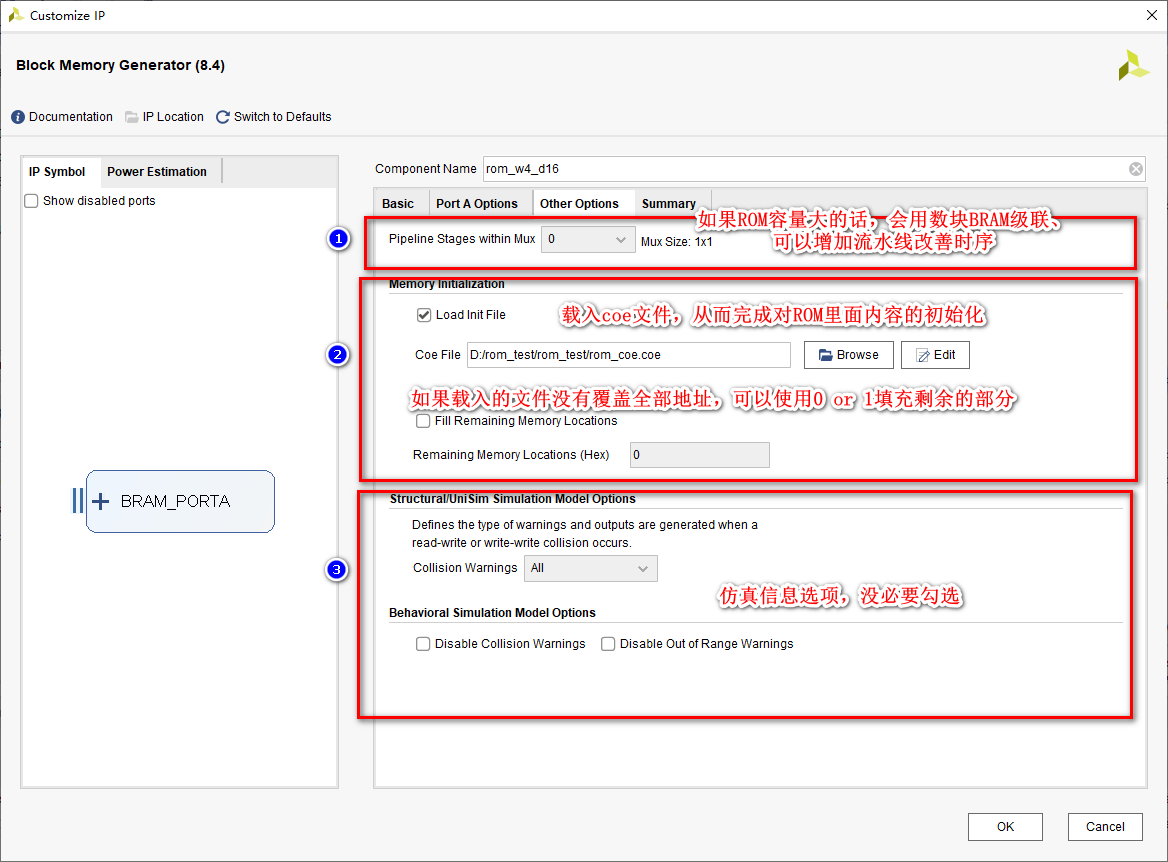

③、 The third page

About the initial file loaded (.coe file ), It can be written in the following format , Then click on Browse selection :

You can also click ,Edit, Then create a new one .coe After the document , Write your own content ( It should be noted that , Do not use ; To the end ):

Yes, of course , What is loaded above is some relatively simple , Regular data . If the data you want to load is complex , It is recommended to use MATLAB Or other scripting software to generate , And save it as coe File reload .

④、 Page four

3、ROM IP Example and simulation test of

3.1、 Exemplify a ROM IP nucleus

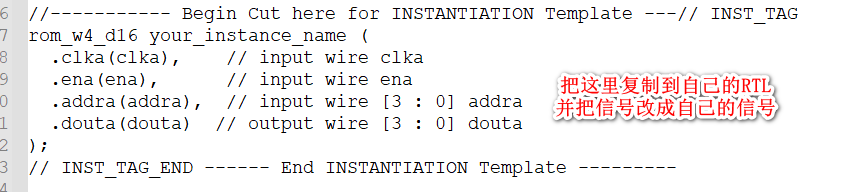

Follow the above steps to generate IP after , Copy IP nucleus The self-contained instantiation template .

And then in our RTL In the code , Instantiate the ROM.RTL No other functions , Only instantiate ROM that will do .

module rom_test(

input clk, // Input clock

input en, // Enable signal

input [3:0] addr, // Address

output [3:0] data_out // Output data

);

// Exemplification ROM IP nucleus

rom_w4_d16 rom_w4_d16_inst (

.clka (clk),

.ena (en),

.addra (addr),

.douta (data_out)

);

endmodule3.2、 The simulation test

Write a testbench, Yes ROM IP Test it .

Test behavior : Write initialization file before (.coe) I already said , The contents loaded are 0、1、2······F. So after stabilization from the address 0-15 Reading data , Observe whether the read data is consistent with the initialization content .

`timescale 1ns / 1ns

module tb_rom_test();

reg clk;

reg en;

reg [3:0] addr;

wire [3:0] data_out;

initial begin

clk = 0;

en = 0;

addr = 0;

#110

en = 1; // Start reading data

repeat(18) begin // From address 0-15 Reading data ( Plus the delay 3)

#10 addr = addr + 1;

end

en = 0; // Stop reading data

#20 $finish; // End the simulation

end

always #5 clk = ~clk; // Generate clock , cycle 10ns

// Instantiate the tested module rom_test

rom_test rom_test_inst(

.clk (clk ),

.en (en ),

.addr (addr ),

.data_out (data_out )

);

endmodule

Use vivado Built in simulation tools simulator Run the simulation , The simulation results are as follows :

stay 3 After a delay of clock cycles , The data read out are 0、1、2······、F, In line with the expected results .

4、 Summary and reference

- You can see ROM IP The customization of is very simple , It's basically a “ Youth version ” Of RAM IP.

- It's not easy to create , If this article helps you , Please give me more praise 、 Reviews and collections . Your support is the biggest driving force for me to continuously update !

Reference material 1:Block Memory Generator v8.4

- Blog home page :wuzhikai.blog.csdn.net

- This paper is written by Lonely single blade original , First appeared in CSDN platform

- Do you have any questions , You can communicate with me in the comment area !

- It's not easy to create , Your support is the biggest driving force for me to continuously update ! If this article helps you , Please give me more praise 、 Reviews and collections !

边栏推荐

- Go language sqlx library operation SQLite3 database addition, deletion, modification and query

- 【板栗糖GIS】arcmap—为什么使用自定义捕捉的时候,经典捕捉的勾要去掉呢?

- Addition, deletion, modification and query of handwritten ORM (object relationship mapping)

- xshell配置xforward转发火狐浏览器

- mysql重置密码,忘记密码,重置root密码,重置mysql密码

- Golang面试整理 三 简历如何书写

- The first batch of Tencent cloud completed the first cloud native security maturity assessment in China

- 成功改变splunk 默认URL root path

- Go multithreaded data search

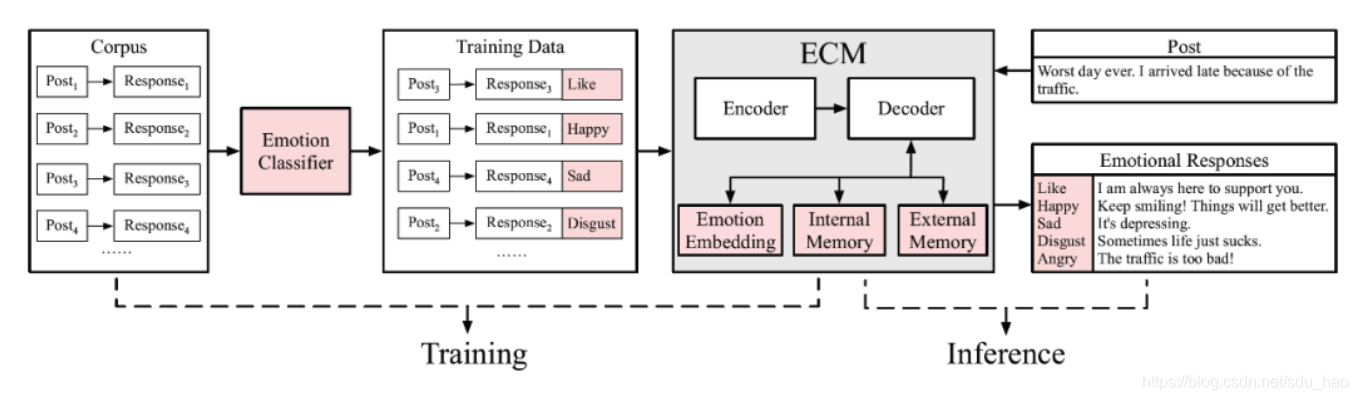

- 情感对话识别与生成简述

猜你喜欢

【硬件】标准阻值的由来

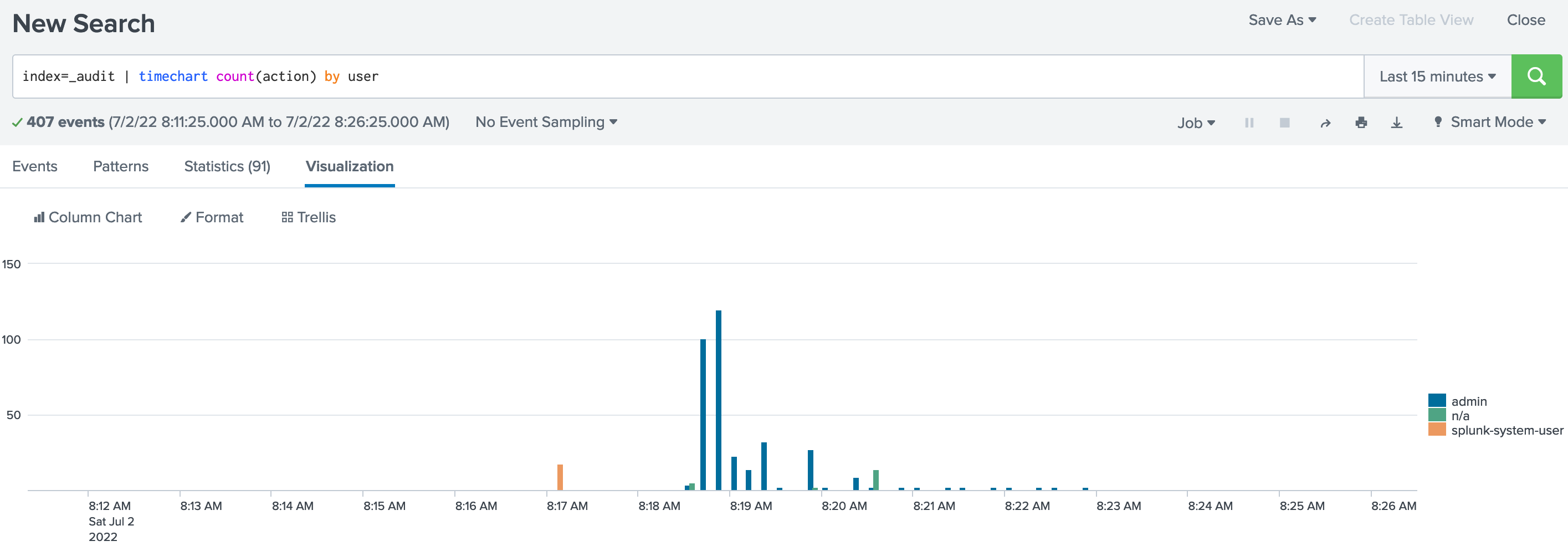

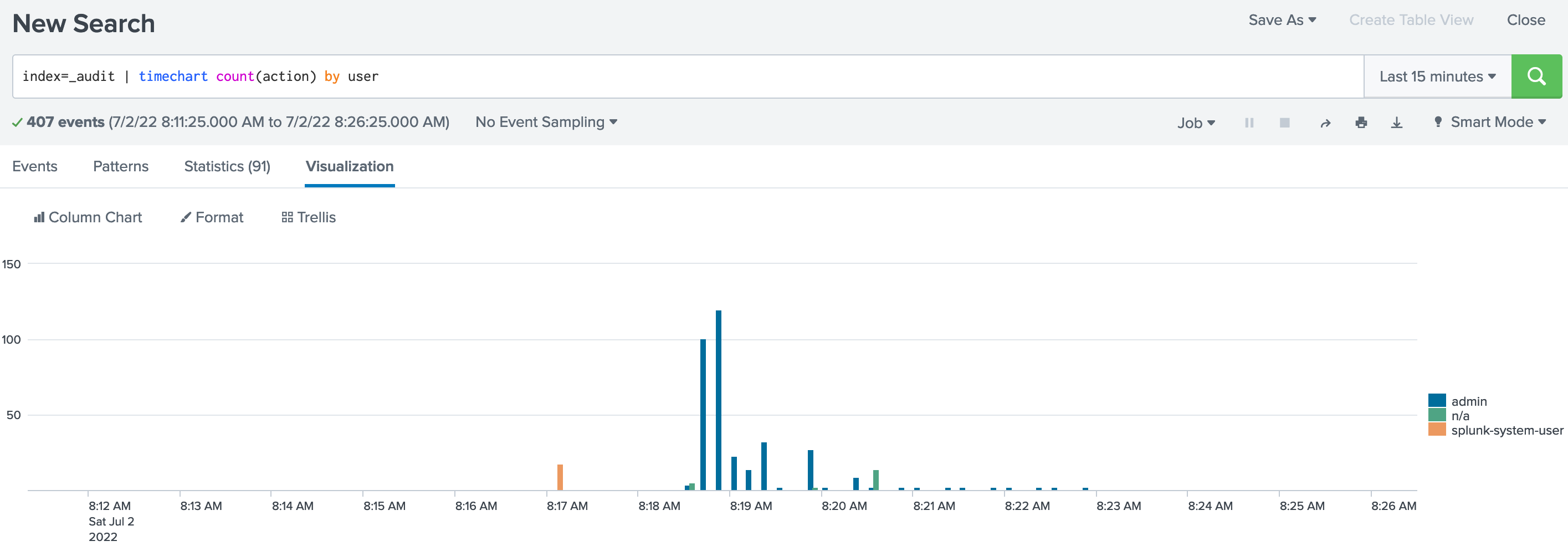

Splunk audit setting

Innovation strength is recognized again! Tencent security MSS was the pioneer of cloud native security guard in 2022

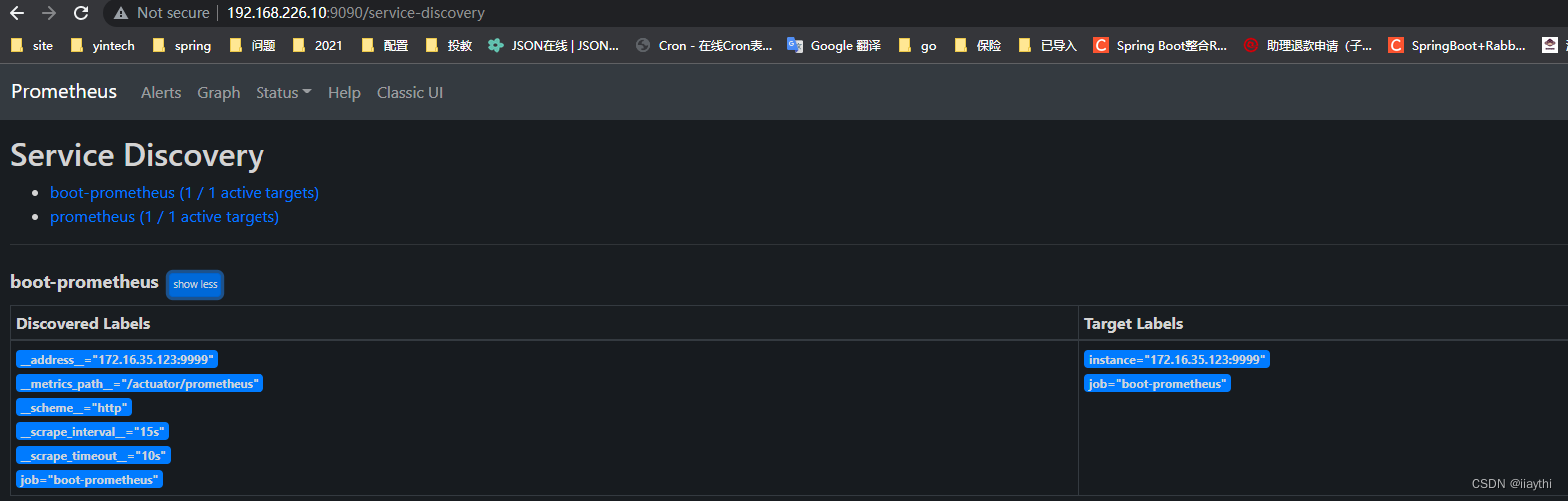

boot actuator - prometheus使用

Local dealers play the community group purchase mode and share millions of operations

情感对话识别与生成简述

Splunk audit 的设定

Hanging mirror security won four global infosec awards on rsac2022

![The kth largest element in the [leetcode] array [215]](/img/72/d3e46a820796a48b458cd2d0a18f8f.png)

The kth largest element in the [leetcode] array [215]

Jatpack------LiveData

随机推荐

`Usage of ${}`

Jerry's fast touch does not respond [chapter]

[LeetCode] 反转字符串中的单词 III【557】

地方经销商玩转社区团购模式,百万运营分享

Go language sqlx library operation SQLite3 database addition, deletion, modification and query

【板栗糖GIS】global mapper 如何通过dsm批量制作贴地等高线

[Solved] Splunk: Cannot get username when all users are selected“

Rails 3 activerecord: sort by association count - rails 3 activerecord: order by count on Association

[NPUCTF2020]ezlogin xPATH注入

Mask R-CNN

移动端 1px 像素兼容性问题,实现1px 边框

Minimum spanning tree

Lambda expression: an article takes you through

Webrtc audio and video capture and playback examples and mediastream media stream analysis

MySQL reset password, forget password, reset root password, reset MySQL password

Jerry's prototype will trigger shutdown after multiple touches [chapter]

从底层结构开始学习FPGA----Xilinx ROM IP的定制与测试

Jatpack------LiveData

损失函数~

严守工期,确保质量,这家AI数据标注公司做到了!