当前位置:网站首页>FPGA - 7系列 FPGA内部结构之Clocking -01- 时钟架构概述

FPGA - 7系列 FPGA内部结构之Clocking -01- 时钟架构概述

2022-07-01 05:45:00 【Vuko-wxh】

前言

本文节选UG472的第一章,进行整理翻译,主要用于介绍7系列的FPGA的时钟架构以及与前几代的FPGA的区别,并总结了时钟连接的相关使用方法。

文章目录

时钟架构概述

7 系列 FPGA 时钟资源通过专用的全局和区域 I/O 和时钟资源管理复杂和简单的时钟要求。 时钟管理块 (CMT) 提供时钟频率合成、去偏斜和抖动过滤功能。在设计时钟功能时,不建议使用非时钟资源,例如本地布线。

- 全局时钟树允许跨器件同步元件的时钟。

- I/O 和区域时钟树允许对多达三个垂直相邻的时钟区域进行计时。

- CMT,每个都包含一个混合模式时钟管理器 (MMCM) 和一个锁相环 (PLL),位于 I/O 列旁边的 CMT 列中。

每个 7 系列器件都被划分了时钟区域。

- 时钟区域的数量随设备大小而变化,从最小设备中的一个时钟区域到最大设备中的 24 个时钟区域。

- 一个时钟区域包括跨越 50 个 CLB 和一个 I/O bank (50 I/O) 的区域中的所有同步元素(例如:CLB、I/O、串行收发器、DSP、块 RAM、CMT),水平 时钟行 (HROW) 在其中心。

- 每个时钟区域从HROW 向上跨越25 个CLB,向下跨越25 个CLB,并水平跨越器件的每一侧。

时钟布线资源概述

每个 I/O bank 都包含具有时钟功能的输入管脚,用于将用户时钟引入 7 系列 FPGA 时钟布线资源。 与专用时钟缓冲器相结合,具有时钟功能的输入将用户时钟带到:

- 器件同一上/下半部分中的全局时钟线。

- 同一 I/O bank 和垂直相邻 I/O bank 内的 I/O 时钟线

- 同一时钟区域和垂直相邻时钟区域内的区域时钟线。

- 同一时钟区域内的 CMT,并且有限制地垂直相邻时钟区域。

每个 7 系列单片芯片都有 32 条全局时钟线,可以为整个器件中的所有时序资源提供时钟和控制信号。 全局时钟缓冲器(BUFGCTRL,简化为 BUFG)驱动全局时钟线,并且必须用于访问全局时钟线。 使用时钟区域中的 12 条水平时钟线,每个时钟区域最多可以支持 12 条这些全局时钟线。

全局时钟缓冲器:

- 可用作时钟使能电路,以启用或禁用跨越多个时钟区域的时钟 。

- 可用作无毛刺多路复用器以:

- 在两个时钟源之间进行选择。

- 从故障时钟源切换。

- 通常由 CMT 驱动以:

- 消除时钟分配延迟。

- 调整相对于另一个时钟的时钟延迟。

水平时钟缓冲器 (BUFH/BUFHCE) 允许通过水平时钟行访问单个时钟区域中的全局时钟线。 它还可以用作时钟使能电路 (BUFHCE),以独立启用或禁用跨越单个时钟区域的时钟。使用每个时钟区域中的 12 条水平时钟线,每个时钟区域最多可支持 12 个时钟。

每个 7 系列 FPGA 都有区域和 I/O 时钟树,可以为一个时钟区域中的所有顺序资源提供时钟。 每个器件还具有多时钟区域缓冲器 (BUFMR),允许区域和 I/O 时钟跨越多达三个垂直相邻的时钟区域。

- I/O 时钟缓冲器 (BUFIO) 驱动 I/O 时钟树,提供对同一 I/O bank 中所有顺序 I/O 资源的时钟访问。

- 区域时钟缓冲器 (BUFR) 驱动区域时钟树,该树驱动同一时钟区域中的所有时钟目标,并可通过编程对输入时钟速率进行分频。

- 结合 IOB 中的可编程串行器/解串器,BUFIO 和 BUFR 时钟缓冲器允许源同步系统跨时钟域而无需使用额外的逻辑资源。

- 与相关的BUFR 或BUFIO 一起使用时,可以使用多时钟区域缓冲器(BUFMR) 驱动相邻时钟区域和I/O bank 中的区域和I/O 时钟树。

- 一个时钟区域或I/O bank 中最多可支持四个唯一I/O 时钟和四个唯一区域时钟。

高性能时钟路由以极低抖动、最小占空比失真的直接路径将 CMT 的某些输出连接到 I/O。

CMT 概述

每个 7 系列 FPGA 最多有 24 个 CMT,每个 CMT 由一个 MMCM 和一个 PLL 组成。 MMCM 和 PLL 用作各种频率的频率合成器,用作外部或内部时钟的抖动滤波器,以及去偏斜时钟。 该锁相环包含MMCM 功能的子集。 7 系列 FPGA 时钟输入连接允许多种资源为 MMCM 和 PLL 提供参考时钟。

7 系列 FPGA MMCM 在任一方向具有无限精细相移能力,可用于动态相移模式。 MMCM 在反馈路径或一个输出路径中也有一个小数计数器,从而实现频率合成能力的进一步粒度。

IP 时钟向导可用于帮助利用 MMCM 和 PLL 在 7 系列 FPGA 设计中创建时钟网络。 GUI界面用于采集时钟网络参数。 时钟向导选择适当的 CMT 资源并优化配置 CMT 资源和相关的时钟路由资源。

时钟缓冲器、管理和路由

下图提供了 7 系列 FPGA 时钟架构的可视化和分层解释。下图是 7 系列 FPGA 时钟架构的高层次的结构视图。 垂直时钟中心线(时钟主干)将器件分为相邻的左右区域,而水平中心线将器件分为顶部和底部。

时钟主干中的资源被镜像到水平相邻区域的两侧,从而将某些时钟资源延伸到水平相邻区域中。 顶部和底部划分将两组全局时钟缓冲器 (BUFG) 分开,并对它们的连接方式施加了一些限制。 但是,BUFG 不属于时钟区域,可以到达设备上的任何时钟点。 所有水平时钟资源都包含在时钟区域水平时钟行 (HROW) 的中心,而垂直的非区域时钟资源包含在时钟主干或 CMT 主干中。

一个时钟区域始终包含每列 50 个 CLB、每列 10 个 36K 块 RAM(除非五个 36K 块被用于 PCI Express 的集成块代替)、每列 20 个 DSP 片和 12 个 BUFH。 如果适用,一个时钟区域包含一个 CMT (PLL/MMCM)、一组 50 个 I/O、一个由四个串行收发器组成的 GT quad,以及块 RAM 列中用于 PCIe的半列。

时钟区域的基本视图

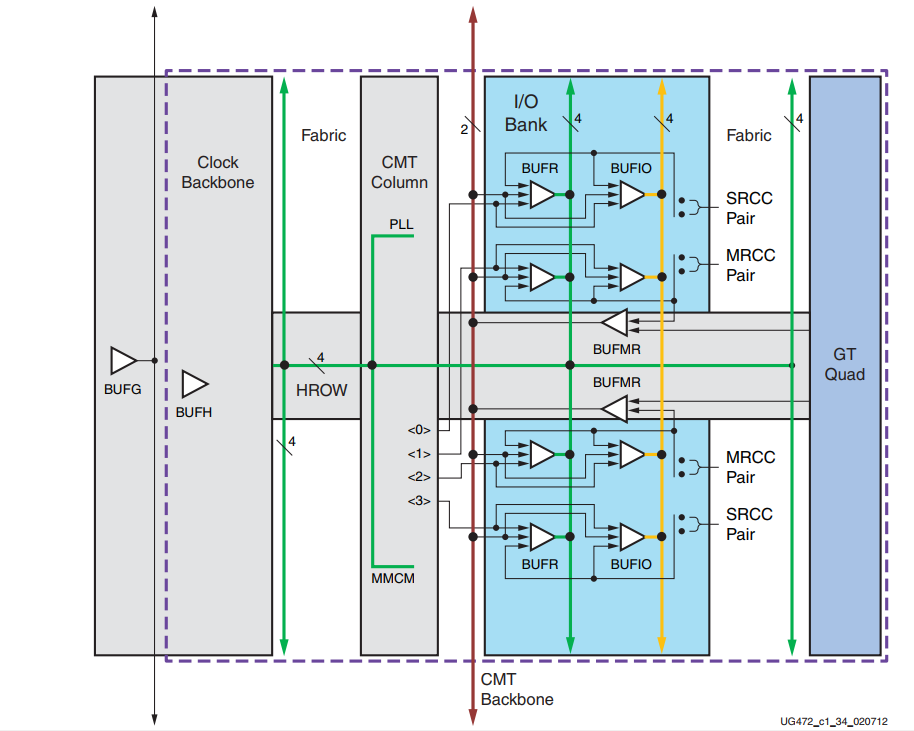

下图是时钟区域的基本视图。

全局时钟缓冲器可以通过 HROW 驱动到每个区域, 水平时钟缓冲器 (BUFH) 通过 HROW 驱动到该区域中的每个时钟点。 BUFG 和 BUFH 共享 HROW 中的布线轨迹。I/O 缓冲器 (BUFIO) 和区域时钟缓冲器 (BUFR) 位于 I/O bank 内。 BUFIO 仅驱动 I/O 时钟资源,而 BUFR 驱动 I/O 资源和逻辑资源。 BUFMR 支持 BUFIO 和 BUFR 的多区域链接。 具有时钟功能的输入将外部时钟连接到设备上的时钟资源。 某些资源可以通过 CMT 主干连接到上方和下方的区域。

单个时钟域的详细视图

下图显示了器件右侧边缘单个时钟区域中时钟的更详细视图。

全局 BUFG 和区域 BUFH/CMT/CC 引脚连接

下图显示了全局 BUFG 和区域 BUFH/CMT/CC 引脚连接以及区域中可用资源数量的详细信息。

四个具有时钟功能的输入管脚中的任何一个都可以驱动 CMT 和 BUFH 中的 PLL/MMCM。 BUFG 显示为存在于该区域中,但可以物理上位于时钟主干中的其他位置。 BUFG 和 BUFH 共享 HROW 中的 12 个路由轨道,可以驱动该区域的所有时钟点。 BUFG 也可以驱动 BUFH。 这允许在其他全局时钟分布上实现单独的时钟使能 (CE)。

GT quad 有 10 个专用轨道来驱动时钟主干中的 CMT 和时钟缓冲器。 位于 I/O bank 中的 BUFR 有四个轨道驱动逻辑、CMT 和 BUFG 中的时钟点。 CMT 可以在有限的情况下使用 CMT 主干驱动相邻区域中的其他 CMT。 同样,具有时钟功能的引脚可以在相同的限制下驱动相邻区域的 CMT。 具有时钟功能的引脚可以驱动器件同一顶部/底部的任何位置的 BUFG。 CMT 主干中有四个轨道来支持垂直区域之间的连接。

来自一个区域的时钟源可以驱动其自身区域以及水平相邻区域中的时钟缓冲器资源。CMT、具有时钟功能的引脚和串行收发器可以通过 BUFH 将时钟驱动到水平相邻区域,并且还可以连接到设备同一顶部/底部的 BUFG。

逻辑互连驱动 BUFG 和 BUFH 的 CE 引脚。 逻辑互连也可以将时钟驱动到相同的缓冲区中,但必须小心,因为时序是不可预测的。

BUFR/BUFMR/BUFIO 时钟区域

下图显示了 I/O 时钟资源的BUFR/BUFMR/BUFIO 时钟区域详细信息。

每个 I/O bank 包含四个 BUFIO 和四个 BUFR。 这些时钟缓冲器中的每一个都可以由具有时钟功能的特定输入时钟引脚对驱动,也可以由 MMCM 的特定输出时钟直接驱动。 两个具有时钟功能的输入引脚对,称为 MRCC,支持多区域时钟方案。 一个 MRCC 引脚对可以驱动特定的 BUFMR,而 BUFMR 又可以驱动相同和相邻区域中的 BUFIO 和 BUFR,从而促进多区域/存储体接口。 同样,GT quad 也可以驱动 BUFMR。

MMCM< 3:0 > 输出具有通往 BUFR 和 BUFIO 的专用高性能差分路径。 此功能也称为高性能时钟 (HPC)。

7 系列 FPGA 时钟与前几代 FPGA 的区别

尽管所有 7 系列器件具有相同的基本架构,但家族之间和家族内的器件之间存在一些架构差异。

每个 7 系列 FPGA 在器件的左边缘至少有一个完整的 I/O 列。 GT 可以是 7 系列 FPGA(GTP、GTX 或 GTH)支持的任何一种串行收发器。带有 GT 的设备要么在设备的右边缘有混合的 GT 和 I/O 列(一些 Kintex-7 设备和一些 Artix-7 设备),要么在右边缘有一个完整的 GT 列(一些 Kintex-7 设备和一些 Virtex-7 设备)以及设备右侧的完整 I/O 列。 其他 Virtex-7 器件具有完整的 GT左侧和右侧边缘的列,左侧和右侧具有完整的 I/O 列。Artix-7 200T 设备在时钟列旁边的顶部和底部都有 GTP 收发器。因此,并非 7 系列器件中的所有时钟区域都包含前面图中所示的所有模块。

7 系列 FPGA 时钟具有与 Virtex-6 FPGA 相似的结构,并支持许多相同的功能。 但是,对各种时钟元件及其功能存在一些架构差异和修改。 与 Spartan-6 FPGA 相比,架构和功能都发生了一些重大变化。一些 Spartan-6 FPGA 时钟原语不再可用,取而代之的是更强大、更简单的结构。

与 Virtex-6 FPGA 的主要区别

- 7 系列 FPGA 的基本 BUFIO 时钟功能没有改变,只是 BUFIO 现在只跨越一个存储体。 相邻存储体的直接时钟由新的时钟缓冲器代替。 现在每个银行有四个 BUFIO。 与BUFIO演进类似,BUFR的基本目的并没有改变。 但是,现在 BUFR 仅直接跨越单个时钟区域。 现在每个区域有四个 BUFR 和四个区域时钟(轨道)。

- 7 系列 FPGA 引入了一种新的缓冲器类型:BUFMR/BUFMRCE。 BUFMR/BUFMRCE 驱动相同和垂直相邻区域中的 BUFIO 和/或 BUFR。它们还提供与 Virtex-6 FPGA 中相同的多时钟区域/多存储库时钟路由,支持相同的三个时钟区域/存储库功能。BUFMRCE 具有可选择的同步或异步切换功能。

- 7 系列 FPGA 不再支持 Virtex-6 系列中的全局时钟 (GC) 输入管脚。 每组四个具有时钟功能的时钟输入引脚/对取代了 GC。

具有时钟功能的输入引脚的连接性已得到增强,以支持许多以前的 GC 功能。 - 全局时钟多路复用器 BUFGMUX 添加了一个属性 CLK_SEL_TYPE,用于允许两个输入时钟的同步或异步时钟切换(以前只能通过 IGNORE 端口使用)。

- BUFHCE 具有增强的时钟使能,以允许输入时钟的同步或异步使能。

- CMT 现在包含一个 MMCM 和一个 PLL(MMCM 的一个子集),而不是两个 MMCM,以及保留的专用存储器接口逻辑。 CMT 列与 CMT 内的 SelectIO列/组相邻,并且具有对 I/O 的专用访问以实现高性能。 全局时钟缓冲器仍然位于由 CMT 驱动的 I/O 列之间的器件垂直中心。不再支持 CMT 内的直接级联。 直接级联到相邻的 CMT 是可能的,但由于资源有限而受到限制。 级联到其他 CMT超出相邻 CMT 会导致源和目标 MMCM/PLL 之间的相位偏移,并且需要特殊的属性设置。

- 小数除法器不再共享输出计数器。 这可以释放这些计数器用于其他用途。 分数计数器增加了静态相移能力。

- CLOCK_HOLD 功能不再可用。

- MMCM 支持扩频。

与 Spartan-6 FPGA 的主要区别

Spartan-6 架构特有的一些 Spartan-6 FPGA 时钟电路拓扑、功能和模块不受支持,并已被 7 系列 FPGA 时钟特性所取代。 7 系列器件不直接支持 DCM_SP、DCM_CLKGEN、BUFIO2、BUFIO2_2CLK、BUFIO2FB、BUFPLL 和 BUFPLL_MCB 等特性和功能。

PLL 是 MMCM 的子集,具有相同的性能(除了最小 CLKIN/PFD 和最小/最大 VCO 频率)、一些连接限制和一些减少的功能。 与之前的 Spartan FPGA PLL 相比,7 系列 FPGA PLL 增加了断电、输入时钟切换和级联到相邻 CMT 的功能。 PLL 与 BUFIO 或 BUFR 没有直接连接。

在 7 系列 FPGA 中,BUFIO2 和 BUFIO2_2CLK 原语没有直接替代品。 使用 BUFIO 和 BUFR 与推荐的连接来驱动 ILOGIC 和 OLOGIC。

不再支持从 GCLK 到 CMT 和全局时钟缓冲器的 Spartan-6 FPGA BUFIO2 专用输入路由。 要迁移到 7 系列 FPGA,请使用来自 CCIO 引脚的专用输入路由。

7 系列 FPGA 中没有与 Spartan-6 FPGA BUFPLL 直接等效的产品。 要进行迁移,请将 BUFIO 和 BUFR 与 ILOGIC 和 OLOGIC 的推荐连接一起使用。 来自 MMCME2 CLKOUT[0:3] 的高性能时钟布线取代了到 BUFPLL 的专用布线。 ISERDES 和 OSERDES 电路基于 Virtex-6 架构。

在 7 系列 FPGA 中,不再需要 BUFPLL_MCB 原语。 DDR 存储器接口在 7 系列 FPGA 中具有不同的(软)实现。

在 7 系列 FPGA 中,不再需要 BUFIO2FB 原语。 对于 MMCM 和 PLL 反馈连接,CLKFBIN 可以直接连接到全局时钟缓冲器、输入引脚或 CLKFBOUT,具体取决于所使用的反馈。

Spartan-6 FPGA 仅支持 BUFH。 7 系列 FPGA BUFHCE 原语增加了禁用时钟的能力,以在由该资源驱动的时钟区域中实现潜在的节能。

7 系列 FPGA 新缓冲器 BUFMR/BUFMRCE 在相同和垂直相邻的时钟区域中驱动 BUFIO 和/或 BUFR。 当与 BUFIO 或 BUFR 一起使用时,BUFMR/BUFMRCE 允许 MRCC 输入访问相邻时钟区域中的 BUFIO 和 BUFR。 BUFMRCE 具有可选择的同步或异步切换功能。

Spartan-6 FPGA 设计迁移的新原语是BUFR。 当与 BUFIO 结合使用时,BUFR 功能取代了 BUFIO2、BUFIO2_2CLK 和 BUFPLL 功能。 每个时钟区域有四个 BUFR。

Spartan-6 FPGA 设计迁移的另一个新原语是 BUFIO。 与 BUFR 一起使用时,BUFIO 功能取代了 BUFIO2、BUFIO2_2CLK 和 BUFPLL 功能。 每个BANK有四个 BUFIO。

Spartan-6 架构中没有两个 DCM 和一个 PLL,7 系列 FPGA 使用一个 CMT,其中包含一个 MMCM、一个 PLL 和专用的存储器接口逻辑,这些逻辑是为 Xilinx 保留的。 这些功能现在支持 DCM 及其相关功能。 CMT 位于与 SelectIO 列相邻的单独列中,并具有对 I/O 的专用访问权限。 DCM_SP 和 DCM_CLKGEN 不再可用,它们的功能现在在 MMCM 和 PLL 中得到支持。

7 系列 FPGA 不再支持全局时钟 (GCLK) 输入。 现在,每个支持 Spartan-6 FPGA GCLK 引脚功能的每个 bank 中都有四个具有时钟功能的输入引脚。

对于 Spartan-6 FPGA 设计人员来说,MMCM 是一个新的功能块。 MMCM 增加了分数除法、精细相移、动态相移、反相时钟输出、CLKOUT6 到 CLKOUT4 级联以及一些其他功能。 到 BUFPLL 的直接布线连接被使用 CLKOUT[0:3] 从 MMCM 到 BUFIO/BUFR 的 HPC 连接所取代。 更广泛的 DRP 也可用。

对于通用高速I/O 时钟,不再推荐使用PLL 的CMT 功能。 PLL 没有直接连接到 BUFIO 或 BUFR。 不再支持 CLKOUT0 反馈。 将 MMCM 用于高速 I/O 接口。 级联连接使用有限的 CMT 骨干资源。 还有一种新的断电模式。 完全支持输入时钟切换。 Spartan-6 FPGA 和 7 系列 FPGA 的工作范围不同。 DRP 功能仍然可用。 DRP 功能位置和地址已更改。

不再支持 Spartan-6 FPGA DCM_SP。 要迁移到 7 系列 FPGA,请使用 MMCM 和 PLL。

7 系列 FPGA 不直接支持 Spartan-6 FPGA DCM_CLKGEN。

使用低带宽的 MMCM 或 PLL 进行输入抖动滤波。 M/D 值的动态重新编程也可以使用 MMCM 或 PLL 的 DRP 参考设计来完成。

时钟连接总结

下表总结了 7 系列 FPGA 的时钟连接。

| Clocking Function or Pin | Directly Driven By | Used to Directly Drive |

|---|---|---|

| 支持多区域时钟的 I/O (MRCC) 每个 bank 中有两个引脚/对。 | External Clock | 位于同一时钟区域和器件驱动器的同一左/右侧的 MRCC: 1. 四个 BUFIO 2. 四个 BUFR 3. 两个 BUFMR 4. 一个 CMT(一个 MMCM 和一个 PLL) 5. 上方和下方的 CMT(使用有限的 CMT 骨干资源) 同一半顶部/底部驱动器内的 MRCC: 1. 16 个 BUFG 同一水平相邻时钟区域内的 MRCC 驱动器: 1. BUFH |

| 具有单区域时钟功能的 I/O (SRCC) 每个 bank 中有两个引脚/对。 | External Clock | SRCC 位于同一时钟区域和器件驱动器的同一左侧/右侧: 1. 四个 BUFIO 2. 四个 BUFR 3. 一个 CMT(一个 MMCM 和一个 PLL) 4. 上方和下方的 CMT(使用有限的 CMT 主干资源) 同一半顶部/底部驱动器中的 SRCC: 1. 16 个 BUFG 同一水平相邻时钟区域驱动器中的 SRCC: 1. BUFH |

| BUFIO | 在同一时钟区域内,BUFIO 由以下设备驱动: 1. MRCC 2. SRCC 3. MMCM.CLKOUT0– MMCM.CLKOUT3 4.CLKFBOUT 5. 在相同时钟区域和时钟区域上下的BUFMR。 | 在同一时钟区域内使用时,BUFIO 驱动: 1. ILOGIC.clk 2. ILOGIC.clkb 3. OLOGIC.clk 4. OLOGIC.clkb 5. OLOGIC.oclk 6. OLOGIC.oclkb |

| BUFR | 在同一时钟区域内,BUFR 由以下各项驱动: 1. MRCC 2. SRCC 3. MMCM.CLKOUT0- MMCM.CLKOUT3 4. CLKFBOUT 来自时钟区域上方和下方的BUFMR。 通用互连。 | 在同一时钟区域内使用时,BUFR 驱动: 1. CMT 2. BUFG 可以驱动的同一时钟区域内的任何时钟点 在同一半顶部/底部内使用时,BUFR 驱动: 1. 16 个 BUFG(不推荐) |

| BUFMR | 在同一时钟区域内,BUFMR 由以下各项驱动: 1. MRCC 2. 此表中列出的 GT 时钟输出 3. 互连(不推荐) | 在同一时钟区域以及上下时钟区域内使用时,BUFMR 驱动: 1. BUFIO 2. BUFR |

| BUFG | 在同一上/下半部分中,BUFG 由以下各项驱动: 1. SRCC 2. MRCC 3. CMT 4. 此表中列出的 GT 时钟输出 5. BUFR(不推荐) 6. 互连(不推荐) 7. 相邻的 BUFG 相同的上/下半部分 | • CMT • 此表中列出的 GT 时钟输出 • 同一上/下半部分中的相邻 BUFG • 架构和 I/O 中的任何时钟点 • CLB 控制信号 • BUFH |

| BUFH | 在同一时钟区域和水平相邻的时钟区域内,BUFH 由以下各项驱动: • SRCC • MRCC • CMT • BUFG • 此表中列出的 GT 时钟输出 • 互连(不推荐) | 在同一时钟区域内使用时,BUFH 驱动: • CMT • 此表中列出的 GT 时钟输出 • BUFG 可以驱动的同一时钟区域中的任何时钟点 |

| GT Transceiver Clocks RXUSRCLK RXUSRCLK2 TXUSRCLK TXUSRCLK2 | • 任何BUFG 在同一时钟区域内,GT 由以下驱动: • BUFH | N/A |

| GT Transceiver Clocks: RXOUTCLK TXOUTCLK | N/A | • 同一半顶部/底部的BUFG 在同一时钟区域内使用时,GT 可以驱动: • CMT • BUFMR • 水平相邻时钟区域中的BUFH 和BUFH |

| MGTREFCLK0/1P MGT 正差分参考时钟引脚 MGTREFCLK0/1N MGT 负差分参考时钟引脚 | External GT reference clock | • GT 参考时钟 • 同一半顶部/底部的BUFG 在同一时钟区域内使用时,外部GT 参考时钟引脚可以驱动: • CMT • BUFMR • 水平相邻时钟区域中的BUFH 和BUFH |

| CMT | • BUFG • SRCC(相同和相邻的时钟区域) • MRCC(相同和相邻的时钟区域) • 相同时钟区域中的 GT • 相同时钟区域中的 BUFR,以及使用 BUFMR 的上方或下方的时钟区域 • MMCM/PLL .CLKOUT0-3 | • 同一上/下半部分中的任何 BUFG 在同一时钟区域内使用时,CMT 可以驱动: • BUFIO (MMCM) • BUFR (MMCM) • 水平相邻时钟区域中的 BUFH 和 BUFH • MMCM/PLL(如果有相位偏移,则 不相邻) |

| IDELAYCNTRL.CLK | • MRCC/SRCC • BUFG • BUFH | N/A |

| CCLK pin | 配置逻辑 | 配置逻辑 |

| EMCCLK pin | N/A | 配置逻辑 |

| TCK pin | N/A | JTAG 配置逻辑和边界扫描 |

7 系列 FPGA 的时钟差异

7 系列 FPGA 系列中的每一个都有一些独特的连接要求。下表按器件系列列出了描述的连接限制。

| Family | Exceptions |

|---|---|

| Spartan-7 FPGAs: All devices | 没有连接异常。 |

| Artix-7 FPGAs: All devices | GTP 收发器与 CMT 和 BUFMR 之间没有直接连接。 从 GTP 收发器连接到 CMT 时,需要 BUFH 或 BUFG。 |

| Kintex-7 FPGAs: All devices | GTX 收发器与 CMT 和 BUFMR 之间没有直接连接。 从 GTX 收发器连接到 CMT 时,需要 BUFH 或 BUFG。 |

| All Virtex-7 T and XT FPGAs | 没有连接异常。 |

| All Virtex-7 HT FPGAs | GTZ 收发器只能连接到插入器时钟主干以连接到 SLR。 因此,它们只能驱动全局时钟网络(BUFG 布线轨道)和 BUFH,并且只能由 BUFG 驱动。 |

reference

- UG472

边栏推荐

- Learn the customization and testing of fpga---ram IP from the bottom structure

- C语言初阶——实现扫雷游戏

- 码蹄集 - MT3114 · 有趣的平衡 - 用样例通俗地讲解

- Chip, an empire built on sand!

- This is the necessary software for college students 𞓜 knowledge management

- Advanced drawing skills of Excel lecture 100 (1) - use Gantt chart to show the progress of the project

- 如何添加葫芦儿派盘

- Through cooperation with the University of international trade, we can increase efficiency for college students

- C language beginner level - realize the minesweeping game

- 数据治理:数据治理框架(第一篇)

猜你喜欢

In depth understanding of condition source code interpretation and analysis of concurrent programming

Trust guessing numbers game

mysql 将毫秒数转为时间字符串

LeetCode 最大矩形,最大正方形系列 84. 85. 221. 1277. 1725. (单调栈,动态规划)

多表操作-外键级联操作

基于微信小程序的青少年生理健康知识小助手(免费获取源码+项目介绍+运行介绍+运行截图+论文)

我从技术到产品经理的几点体会

HCM 初学 ( 三 ) - 快速输入PA70、PA71 浏览员工信息PA10

Mongodb學習篇:安裝後的入門第一課

Crossing pie · pie pan + Mountain duck = local data management

随机推荐

Daily code 300 lines learning notes day 11

Leetcode top 100 question 2 Add two numbers

CentOS 7 installed php7.0 using Yum or up2date

[medical segmentation] u2net

HDU - 1024 Max Sum Plus Plus(DP)

It's not that you have a bad mind, but that you haven't found the right tool

Geoffrey Hinton:我的五十年深度学习生涯与研究心法

tese_Time_2h

OpenGL ES: (1) OpenGL ES的由来 (转)

论文学习记录随笔 多标签之GLOCAL

Send you through the data cloud

【QT】qt加减乘除之后,保留小数点后两位

数据治理:数据治理框架(第一篇)

How to add a gourd pie plate

Data governance: metadata management implementation (Part IV)

码蹄集 - MT3149 · AND - 数据不是很强,暴力剪枝就能骗AC

穿越派与贸大合作,为大学生增添效率

Continuous breakthrough and steady progress -- Review and Prospect of cross platform development technology of mobile terminal

Advanced cross platform application development (II): uni app practice

为了保护自己的数据,他奋斗了一天一夜