当前位置:网站首页>verilog学习|《Verilog数字系统设计教程》夏宇闻 第三版思考题答案(第十章)

verilog学习|《Verilog数字系统设计教程》夏宇闻 第三版思考题答案(第十章)

2022-08-02 14:02:00 【驚蟄_】

《Verilog数字系统设计教程》夏宇闻 第三版思考题

答案合集 : Verilog学习系列 第三部分

1.写出8位加法器和8位乘法器的逻辑表达式,比较用超前进位逻辑和不用超前进位逻辑的延迟。

八位加法器

module add8 (a, b, sum, cout);

input [7:0] a,b;

output [7:0] sum;

output cout;

assign {

cout, sum} = a + b;

endmodule

八位乘法器

module add8 (a, b, m);

input [7:0] a,b;

output [15:0] sum;

assign m = a * b;

endmodule

2.为什么用算术操作符号表示的加法器和乘法器能通过综合器转变成逻辑电路?除了用算术操作符的表达式实现加法器和乘法器外,是否可以直接引用可配置的参数化实例来实现算术操作电路?

因为库中已经存在着可配置的参数化加法器乘法器的电路结构和相应行为模型。可以直接引用可配置的参数化实例来实现算术操作电路。

3.提高复杂运算组合逻辑运算速度有哪些办法?

采用流水线的设计方法,用总线的方式实现数据流通。

4.如何用Verilog HDL模块来描述总线的操作?为什么总线的操作必须有严格的时序控制?

各运算部件和数据寄存器可以通过带控制的三态门与总线的连接,通过对控制端电平的控制来确定在某一段时间内,总线归哪两个或哪几个部件使用。因为使总线连接模块能正常工作的最重要的因素是与其他模块的配合,控制信号的互相配合由同步状态机控制的开关阵列控制。

5.详细解释为什么采用流水线的办法可以显著提高层次多的复杂组合逻辑的运算速度。

采用流水线技术可以在相同的半导体工艺的前提下通过电路结构的改进大幅度地提高重复多次使用的复杂组合逻辑计算电路的吞吐量,从而来提高层次多的复杂组合逻辑的运算速度。如果某个组合逻辑设计的处理流程可以分为若干个步骤,而且整个数据处理过程是单向的即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计方法提高系统的数据处理频率即吞吐量。把组合逻辑分成延迟时间相等的小块,每块完成一定的组合逻辑功能都用寄存器暂存保存组合逻辑输出的数据值,只要小块的组合逻辑的延迟小于时钟周期,整个组合逻辑的输入值每个时钟就可以变化一次不会由于组合逻辑的延迟引起输出值的错误,若没有这些寄存器来暂时保存局部组合逻辑的输出值,则为了保证整个组合逻辑的输出正确,输出端信号的变化周期必须大于整体逻辑的延迟时间。数据处理的吞吐量受到限制,采用流水线方法,虽然第一次输出有较长的延迟,但过了若干个周期后,每个时钟周期可以输出值一次,数据处理的频率,即吞吐量大大增加了。

边栏推荐

- 编程规范——LiteOS

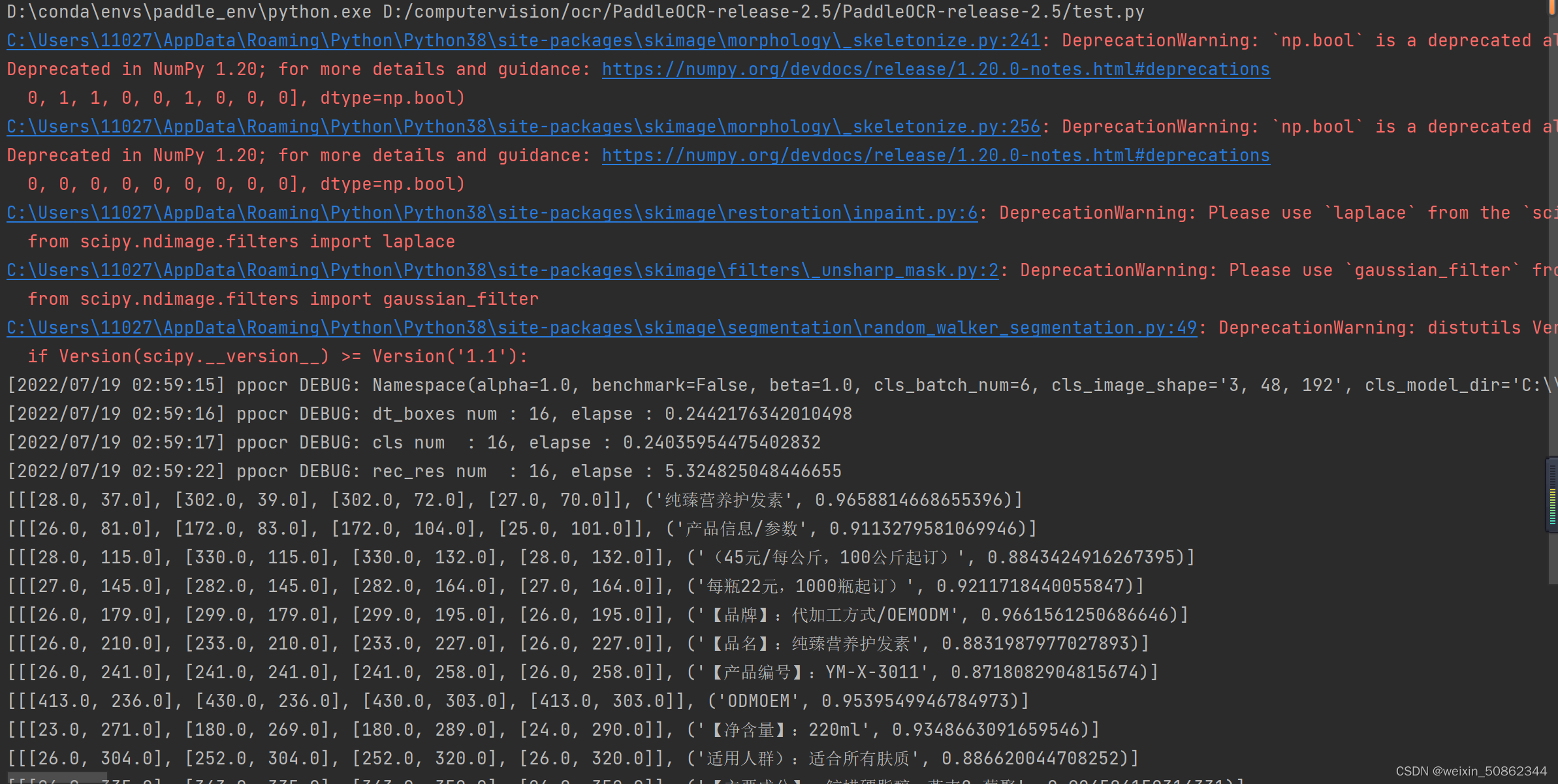

- Hands-on OCR (1)

- LayoutParams的详解

- Flask framework in-depth

- The bad policy has no long-term impact on the market, and the bull market will continue 2021-05-19

- Shell脚本完成pxe装机配置

- Sentinel源码(四)(滑动窗口流量统计)

- Chapter6 visualization (don't want to see the version)

- [ROS] (06) ROS Communication - Topic Communication

- 深度学习框架pytorch快速开发与实战chapter4

猜你喜欢

随机推荐

网页设计(新手入门)[通俗易懂]

chapter7

WeChat Mini Program-Recent Dynamic Scrolling Implementation

(ROS) (03) CMakeLists. TXT, rounding

Raft对比ZAB协议

Minio文件上传

[ROS] Introduction to common tools in ROS (to be continued)

[ROS](04)package.xml详解

瑞吉外卖笔记——第08讲读写分离

yolov5改进(一) 添加注意力集中机制

第十三单元 混入视图基类

理解TCP长连接(Keepalive)

MySQL数据库语法格式

[ROS] (06) ROS Communication - Topic Communication

yolov5,yolov4,yolov3乱七八糟的

8583 顺序栈的基本操作

Shell脚本完成pxe装机配置

瑞吉外卖笔记——第10讲Swagger

EasyExcel 的使用

Unit 5 Hold Status