当前位置:网站首页>(4)UART應用設計及仿真驗證2 —— TX模塊設計(無狀態機)

(4)UART應用設計及仿真驗證2 —— TX模塊設計(無狀態機)

2022-07-05 23:10:00 【少卿不在大理寺】

前言:再次回顧這個小項目已是幾個月後了,在後續的學習中,新的老師在不斷强調,實際工作中盡量少用狀態機,整理文章時忘了當時他咋說的了。所以我試著自己重新寫一下UART,整理一個不帶狀態機的版本。

這裏有幾個基礎的邏輯點要再次回顧一下:

1)完整的一幀數據格式包含:起始比特,有效數據比特,校驗比特,停止比特;

2)計算單bit數據的傳輸時間:利用baoud(波特率)和clk(系統時鐘),波特率單比特bit per second,時鐘Hz單比特time per second ,所以時鐘除以波特率得到的就是time per bit,即每bit對應多少個時鐘周期;

3)參考信號:傳輸信號baoud_cnt_half,每bit計數到一半的時候,傳遞數據;切換計數信號baoud_cnt_end,每bit計數完的時候,進入下一輪計數周期;比特計數bit_cnt,計算一幀數據中傳遞到第幾比特了;傳輸過程標志信號start_flag,貫穿每一次的數據傳輸。

上代碼:

//date:2022.6.30

//edgar.yao

//uart_tx block

module uart_tx(

input clk,

input rst_n,

input[7:0] cmd_data,

input data_valid,

output tx,

output tx_read边栏推荐

- Commonly used probability distributions: Bernoulli distribution, binomial distribution, polynomial distribution, Gaussian distribution, exponential distribution, Laplace distribution and Dirac delta d

- Global and Chinese markets of tantalum heat exchangers 2022-2028: Research Report on technology, participants, trends, market size and share

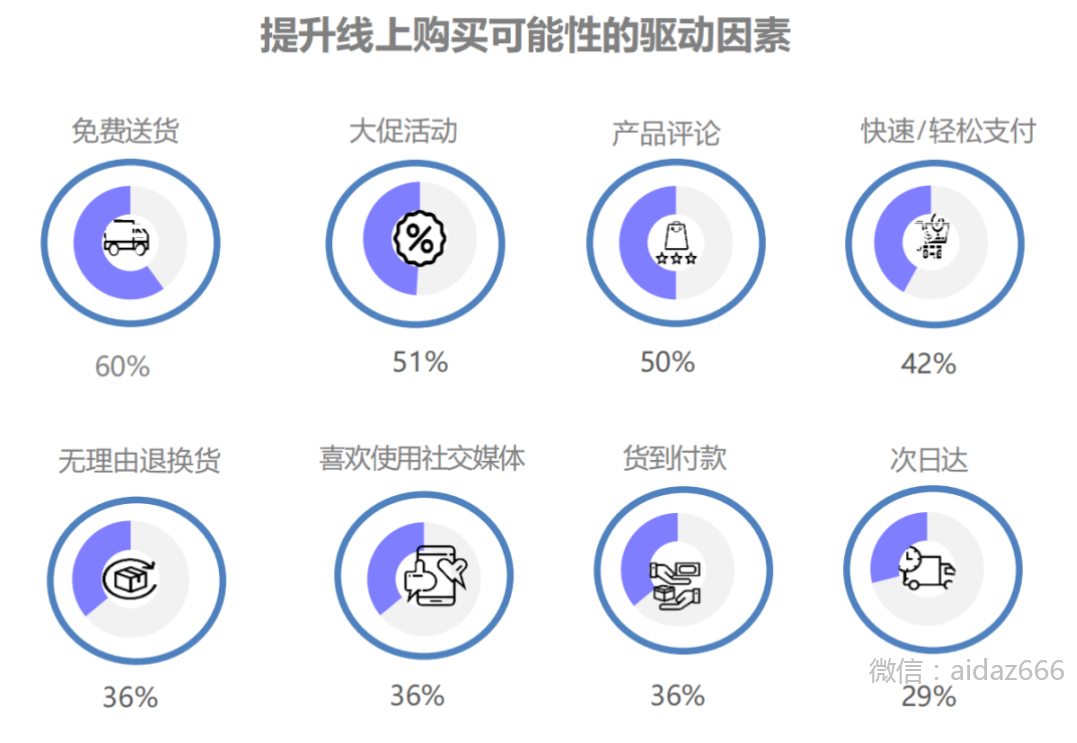

- Southeast Asia e-commerce guide, how do sellers layout the Southeast Asia market?

- Hcip day 12 (BGP black hole, anti ring, configuration)

- Shell: operator

- Negative sampling

- 3D reconstruction of point cloud

- Three. Js-01 getting started

- Alibaba Tianchi SQL training camp task4 learning notes

- February 13, 2022 -5- maximum depth of binary tree

猜你喜欢

Registration and skills of hoisting machinery command examination in 2022

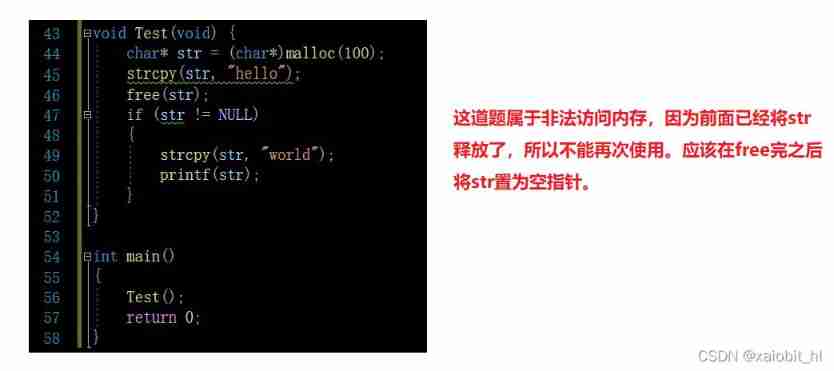

Dynamic memory management (malloc/calloc/realloc)

Southeast Asia e-commerce guide, how do sellers layout the Southeast Asia market?

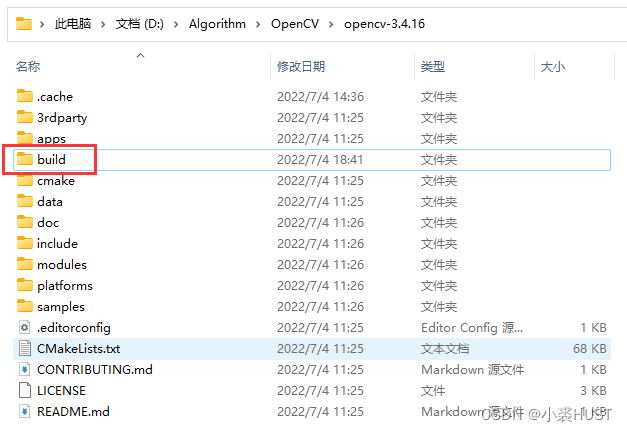

VOT toolkit environment configuration and use

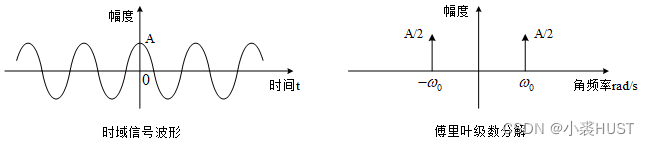

傅里叶分析概述

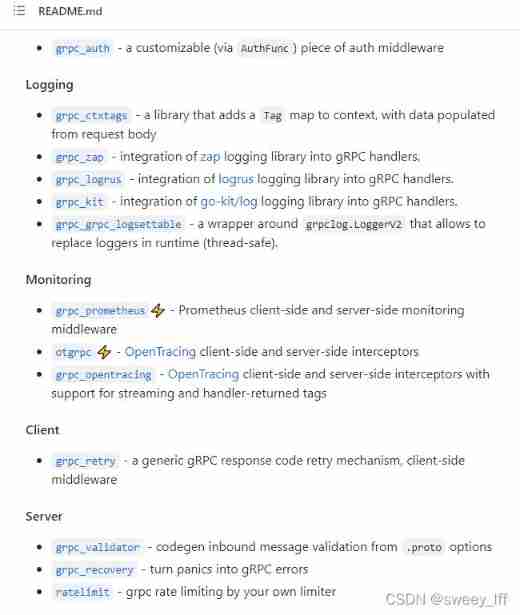

Use of grpc interceptor

![[speech processing] speech signal denoising based on Matlab GUI Hanning window fir notch filter [including Matlab source code 1711]](/img/03/8fa104b177698a15b7ffa70d4fb524.jpg)

[speech processing] speech signal denoising based on Matlab GUI Hanning window fir notch filter [including Matlab source code 1711]

![[speech processing] speech signal denoising and denoising based on Matlab GUI low-pass filter [including Matlab source code 1708]](/img/df/9aa83ac5bd9f614942310a040a6dff.jpg)

[speech processing] speech signal denoising and denoising based on Matlab GUI low-pass filter [including Matlab source code 1708]

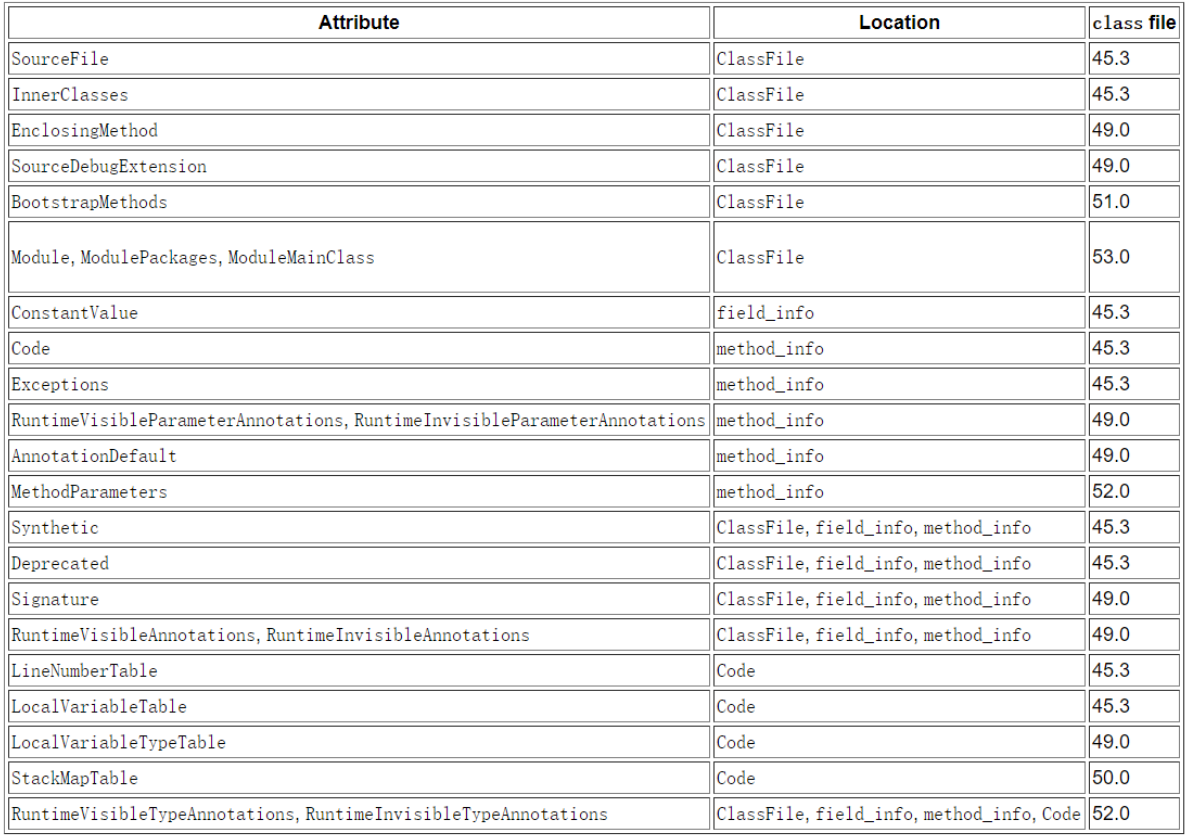

一文搞定class的微观结构和指令

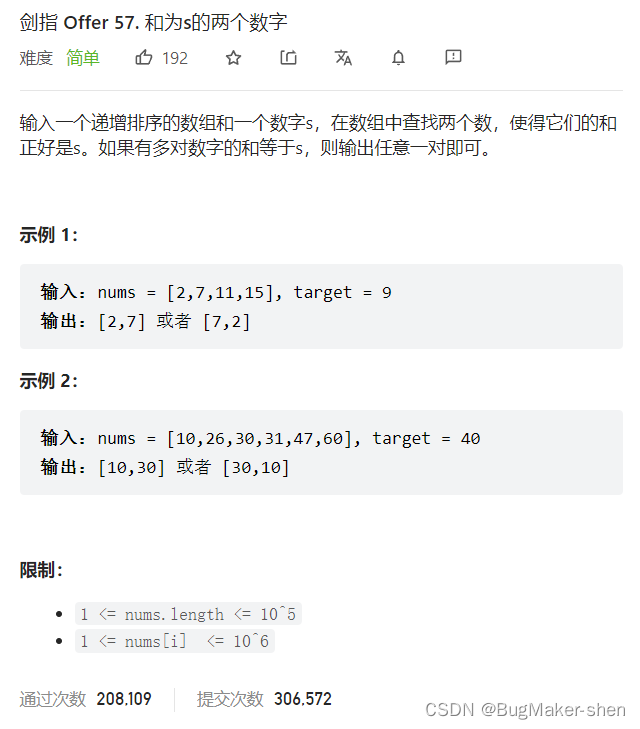

两数之和、三数之和(排序+双指针)

随机推荐

3:第一章:认识JVM规范2:JVM规范,简介;

leecode-学习笔记

Basic knowledge of database (interview)

2:第一章:认识JVM规范1:JVM简介;

LeetCode102. Sequence traversal of binary tree (output by layer and unified output)

Boring boring

Nail error code Encyclopedia

[speech processing] speech signal denoising based on Matlab GUI Hanning window fir notch filter [including Matlab source code 1711]

秒杀系统的设计与实现思路

Ultrasonic sensor flash | LEGO eV3 Teaching

Global and Chinese market of water treatment technology 2022-2028: Research Report on technology, participants, trends, market size and share

[screen recording] how to record in the OBS area

MoCo: Momentum Contrast for Unsupervised Visual Representation Learning

d3dx9_ What if 29.dll is missing? System missing d3dx9_ Solution of 29.dll file

d3dx9_ How to repair 31.dll_ d3dx9_ 31. Solution to missing DLL

C Primer Plus Chapter 9 question 10 binary conversion

February 13, 2022-4-symmetric binary tree

Realize reverse proxy client IP transparent transmission

Multi camera stereo calibration

视频标准二三事