当前位置:网站首页>The new version of onespin 360 DV has been released, refreshing the experience of FPGA formal verification function

The new version of onespin 360 DV has been released, refreshing the experience of FPGA formal verification function

2022-07-07 21:18:00 【Maihexong】

360 DV Is aimed at FPGA Design solutions for functional verification . It combines full-featured high-performance formal analysis with unique assertion coverage assessment , Eliminate guesswork during quality assertion generation , Effectively improve the productivity of existing design and validation processes . What new experiences will this update bring to the design team ?

One 、DV inspect Function update

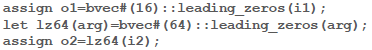

● Read write competition check

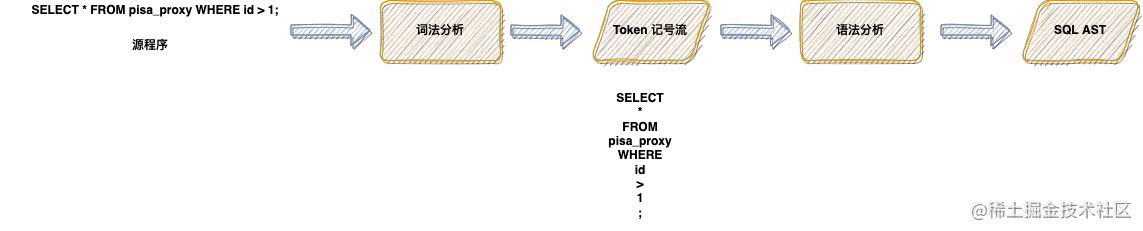

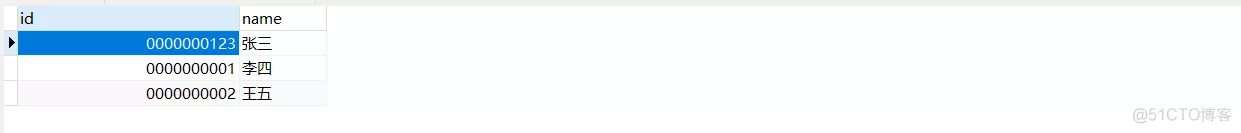

explain : As shown in the figure below , The simulation results are not consistent with those of the upper board , This is a synthesis and simulation mismatch problem caused by reading and writing signals in different processes , Now? ,OneSpin New features to check for such problems , Ensure that the simulation results are consistent with the actual situation after synthesis .

● Negative conversion check

explain : Automatic tagging of unexpected design behavior

● Deadlock / Live lock inspection

explain : If DUT Into a state that is no longer running ( Auto suspend ), Then mark... In the inspection results

● newly added Lint Check the item

* Mixed extremum reset

* Mix sync / Asynchronous reset

* blend ( Not ) Block assignment

* Useless state machine position

* An incomprehensible delay

* Repetitive case label

* Multiple drive

* Non constant asynchronous reset value

Two 、 Debug function update

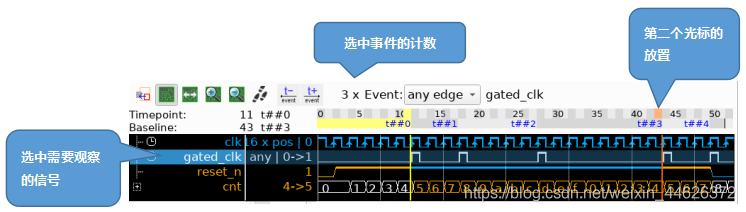

● Modification of the second wave cursor

explain : It's tedious to calculate the number of events in the waveform interface , And it's easy to make mistakes . Now the second cursor will automatically display the event count of the selected signal , And you can put it in the next / The previous event

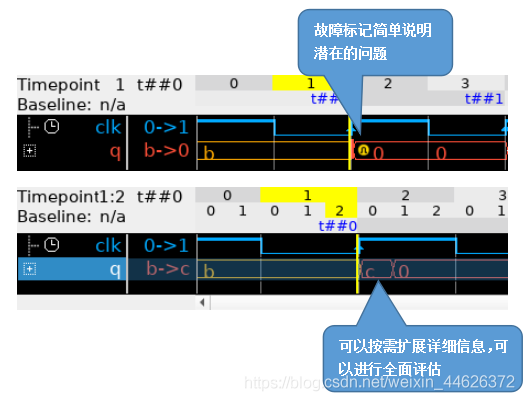

● New fault view

explain : In the course of debugging , Fewer harmful faults , In order to make the fault in the waveform debugging interface , More obvious , It's easier to analyze , The waveform interface will highlight the place where the fault occurs , And provide a simple explanation .

3、 ... and 、 Code language update

● New support for static SystemVerilog class , Using shared functions of classes with static methods / The type is more flexible , Here's the picture , The universal leading zero counter can be used directly

Four 、DV Apps to update

● IEEE-754 2019 Added new Max / Minimum function , and RISC-V The standard forbids IEEE-754 Some of the optional elements in , Now? ,FPU app Of RISC-V Configuration can be seamlessly integrated into RISC-V Of FPU Verification in progress

● Check signal name is supported in register check

explain : Make sure RTL The signal name matches IP-XACT standard

● Connectivity APPs Custom naming is supported in

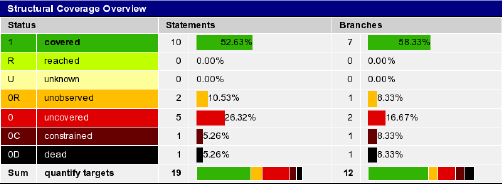

● Simplify coverage check reporting

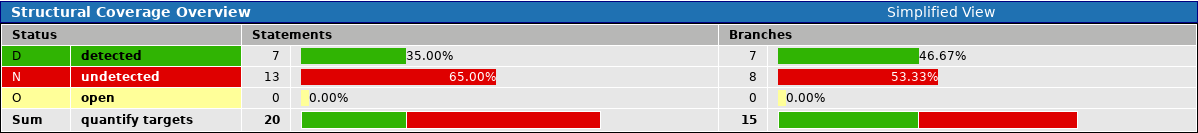

explain : The coverage state is simplified to D(detected), N(undetected), O(open), To make the result clearer

Original coverage interface

New coverage screen

New coverage screen

For more details :http://www.softtest.cn/

边栏推荐

- Mahout-Pearson correlation的实现

- 201215-03-19—cocos2dx内存管理–具体解释「建议收藏」

- FatMouse' Trade (Hangdian 1009)

- Description of the difference between character varying and character in PostgreSQL database

- Demon daddy A1 speech listening initial challenge

- 开户必须往账户里面赚钱吗,资金安全吗?

- 数值法求解最优控制问题(〇)——定义

- Lex & yacc of Pisa proxy SQL parsing

- 恶魔奶爸 B3 少量泛读,完成两万词汇量+

- 95年专注安全这一件事 沃尔沃未来聚焦智能驾驶与电气化领域安全

猜你喜欢

使用枚举实现英文转盲文

Lex & yacc of Pisa proxy SQL parsing

![Is embedded system really safe? [how does onespin comprehensively solve the IC integrity problem for the development team]](/img/af/61b384b1b6ba46aa1a6011f8a30085.png)

Is embedded system really safe? [how does onespin comprehensively solve the IC integrity problem for the development team]

Codesonar Webinar

Solve the problem of using uni app mediaerror mediaerror errorcode -5

MySQL约束之默认约束default与零填充约束zerofill

How to meet the dual needs of security and confidentiality of medical devices?

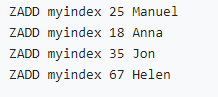

Implement secondary index with Gaussian redis

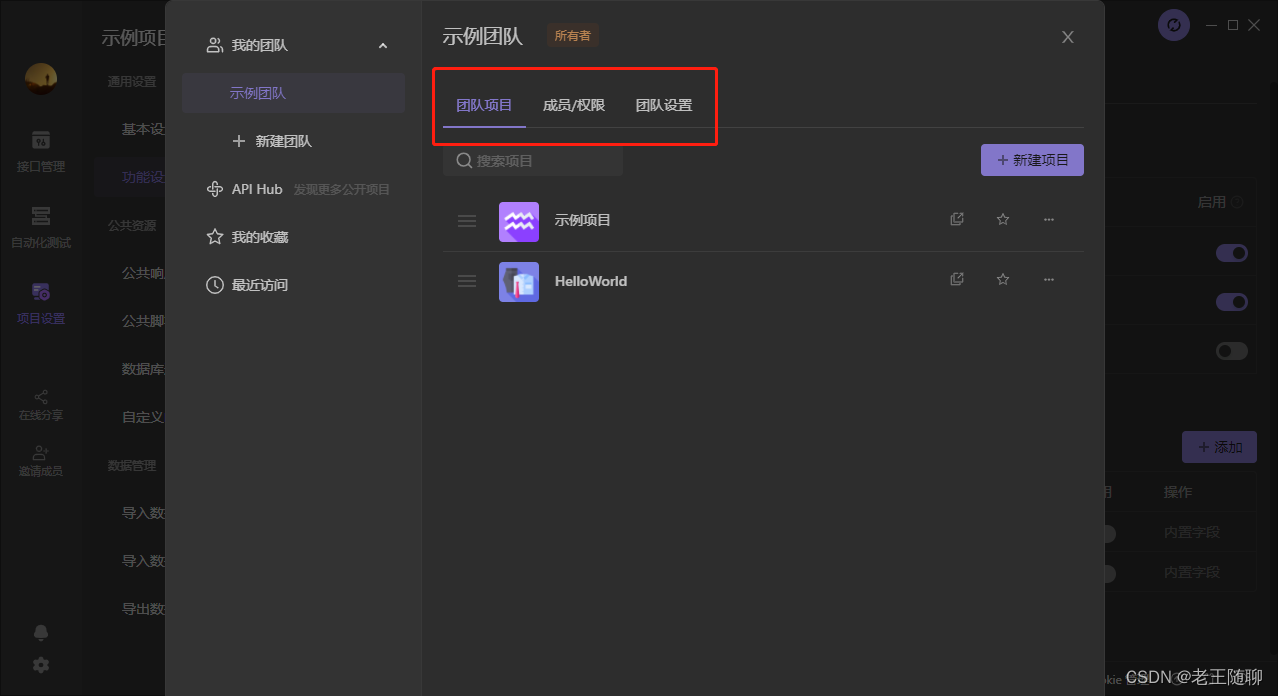

Apifox interface integrated management new artifact

程序猿赚的那点钱算个P啊!

随机推荐

寫一下跳錶

Is it safe to open an account online now? I want to know where I can open an account in Nanning now?

开户必须往账户里面赚钱吗,资金安全吗?

openGl超级宝典学习笔记 (1)第一个三角形「建议收藏」

Onespin | solve the problems of hardware Trojan horse and security trust in IC Design

Devil daddy A0 English zero foundation self-improvement Road

恶魔奶爸 C

Using enumeration to realize English to braille

Implementation of mahout Pearson correlation

Data sorting in string

Object-C programming tips timer "suggestions collection"

Helix QAC 2020.2 new static test tool maximizes the coverage of standard compliance

恶魔奶爸 指南帖——简易版

Le capital - investissement est - il légal en Chine? C'est sûr?

DataTable数据转换为实体

Awk processing JSON processing

GridView defines its own time for typesetting "suggestions collection"

guava多线程,futurecallback线程调用不平均

Addition, deletion, modification and query of sqlhelper

论文解读(ValidUtil)《Rethinking the Setting of Semi-supervised Learning on Graphs》