当前位置:网站首页>[Yu Yue education] basic reference materials of digital electronic technology of Xi'an University of Technology

[Yu Yue education] basic reference materials of digital electronic technology of Xi'an University of Technology

2022-07-06 02:40:00 【yuyueshool】

education

- Fundamentals of digital electronic technology - Chapter materials, examination materials - Xi'an University of Technology 【】

Chapter I homework 1—— New questions ( common 2 topic )

Chapter I homework 2—— Advanced questions ( common 2 topic )

The first 1 Chapter Number system and code system unit test

1、【 Single topic selection 】 A hexadecimal number can be used ( ) Bit binary number to represent .

A、1

B、2

C、4

D、16

Reference material 【 】

2、【 Single topic selection 】 The following statement is wrong ( ).

A、 Analog circuits are used to transmit 、 Handle 、 Process analog signals , To realize logical operation .

B、 Digital circuits are used for transmission 、 Handle 、 Processing digital signals , To realize logical propositions .

C、 The input signal of a digital circuit represents the condition of a logical proposition , The output signal represents the conclusion of the logical proposition .

D、 The value of logical variable is only “ really ” and “ false ” Two possible .

Reference material 【 】

3、【 Single topic selection 】 Can pass ( ) Method , Convert a non decimal number to a decimal number .

A、 Expand and add by weight

B、 Integer division , Reverse order of remainder

C、 Decimal division , Rounding order

D、 Group to position conversion , The order is the same

Reference material 【 】

4、【 Single topic selection 】n The maximum decimal number corresponding to bit binary number is ( ).

A、

B、

C、

D、

Reference material 【 】

5、【 Single topic selection 】(1010 1000. 0010 01)5421BCD= =

=

A、 75.24 111 0101.0010 01

B、98.24 1100 1011.0010 01

C、75.24 1100 1011.0010 01

D、98.24 111 0101.0010 01

Reference material 【 】

6、【 Multiple choice 】 In a 8 Bit storage unit , The largest unsigned integer that can be stored is ( ).

A、

B、

C、

D、

Reference material 【 】

7、【 Multiple choice 】 In the following code , Those belonging to the unauthorized value code are ( ).

A、8421BCD code

B、5421BCD code

C、 The remaining three yards

D、 Gray code

Reference material 【 】

8、【 Judgment questions 】 Used in digital circuits “1” and “0” They represent two states respectively , There is no difference between the two .( )

A、 correct

B、 error

Reference material 【 】

9、【 Judgment questions 】8421BCD Code is a kind of weighted code , It's also clear , The coding scheme is fixed .( )

A、 correct

B、 error

Reference material 【 】

10、【 Judgment questions 】 Write decimal numbers 5 Corresponding 8421 odd-parity code , Its check digit should be 1.( )

A、 correct

B、 error

Reference material 【 】

The first 2 Chapter operation 1—— New questions ( common 1 topic )

The first 2 Chapter operation 2—— Advanced questions ( common 1 topic )

The first 2 Chapter Basic logic operation and common compound logic unit test

1、【 Single topic selection 】 In the following logical expression , When the input A=B=1 when , Output F=1 Of ( ).

A、

B、

C、

D、

Reference material 【 】

2、【 Single topic selection 】 In the following logical expression , The right is ( ).

A、1·A = 1

B、1·A =A

C、1·A = 0

D、1·A = 1+A

Reference material 【 】

3、【 Single topic selection 】 The following logical expression is consistent with the following algorithm ( ).

A、C·C=

B、1+1=10

C、0<1

D、A+1=1

Reference material 【 】

4、【 Single topic selection 】 In the following statement , The wrong is ( ).

A、 If two functions have same truth table , Then the two logical functions must be equal .

B、 If two functions have different truth tables , Then the two logical functions must not be equal .

C、 If two functions have different logical function expressions , Then the two logical functions must not be equal .

D、 If two functions have the same logical function formula , Then the two logical functions must be equal .

Reference material 【 】

5、【 Single topic selection 】 Enter the following ( ) when ,“ And non ” The result of the operation is logic 0.

A、 All inputs are 0

B、 Any input is 0

C、 Only one input is 0

D、 All inputs are 1

Reference material 【 】

6、【 Single topic selection 】 In the following logic gate symbols , Realization “ Two input or not ” The function is ( ).

A、

B、

C、

D、

Reference material 【 】

7、【 Single topic selection 】 Of all the conditions that determine the outcome of an event , As long as one condition holds , The result happens , The logical relationship between this condition and the result is ( ).

A、 And

B、 or

C、 Not

D、 Exclusive or

Reference material 【 】

8、【 Single topic selection 】 In the following statement , The right is ( ).

A、2 Enter the XOR function and 2 Input homor functions are logically inverse to each other .

B、 XOR function and homor function are mutually inverse functions in logic .

C、 When the number of input variables is odd , XOR function and homor function are inverse functions of each other .

D、 When the number of input variables is even , XOR function and homor function have the same logical function .

Reference material 【 】

9、【 Single topic selection 】 Logical functions F= A⊕(A⊕B) , Its simplest form is ( ).

A、A

B、B

C、

D、AB

Reference material 【 】

10、【 Single topic selection 】 The logical expression of the same or is :( )

A、

B、

C、

D、

Reference material 【 】

The first 3 Chapter operation 1—— New questions ( common 3 topic )

The first 3 Chapter operation 2—— Advanced questions ( common 1 topic )

The first 3 Chapter Basic unit test of logic algebra

1、【 Single topic selection 】 The simplification formula used to simplify the adjacent items of logic is ( ).

A、 Law of absorption 1

B、 Law of absorption 2

C、 Law of absorption 3

D、 Law of redundancy

Reference material 【 】

2、【 Single topic selection 】A+BC =( )

A、A+B

B、A+C

C、(A+B)(A+C)

D、B+C

Reference material 【 】

3、【 Single topic selection 】 Logical functions

A、A+B

B、A+B+C

C、0

D、1

Reference material 【 】

4、【 Single topic selection 】

A、AD

B、ABD

C、

D、

Reference material 【 】

5、【 Single topic selection 】 Logical formula  Can be transformed into ( ).

Can be transformed into ( ).

A、

B、

C、

D、

Reference material 【 】

6、【 Judgment questions 】 Law of absorption 2 And the law of absorption 3 The starting point of the application of is to find a single factor term in the expression to be simplified .( )

A、 correct

B、 error

Reference material 【 】

7、【 Judgment questions 】 The derivation of the following logical expression is true .( ) •

•

A、 correct

B、 error

Reference material 【 】

8、【 Judgment questions 】“ Exclusive or ” and “ Same as or ” Is a sibling operation , And the operation priority is higher than “ And logic ”.( )

A、 correct

B、 error

Reference material 【 】

9、【 Judgment questions 】 Because logical expressions A+B+AB=A+B establish , therefore AB=0 establish .( )

A、 correct

B、 error

Reference material 【 】

10、【 Judgment questions 】 If the logical function is negated twice, it will revert to the original function , The dual form of a logical function is reduced to itself by dual transformation .( )

A、 correct

B、 error

Reference material 【 】

The first 4 Chapter operation 1—— New questions ( common 3 topic )

The first 4 Chapter operation 2—— Advanced questions ( common 2 topic )

The first 4 Chapter Logic gate circuit unit test

1、【 Single topic selection 】 Ordinary TTL In non gate circuit , The function of input stage diode is ( ).

A、 Make the power supply voltage more stable

B、 Prevent the input voltage from being too high

C、 Prevent the input voltage from being too low

D、 Form the input stage circuit

Reference material 【 】

2、【 Single topic selection 】 The known diode gate circuit is shown in the figure , The input high level is 3V, The input low level is 0.3V, The logical expression of the circuit is ().

A、

B、

C、

D、

Reference material 【 】

3、【 Single topic selection 】 In the following statement , The wrong is ( ).

A、TTL The typical values of logic gate input high level and output high level are 3.6V.

B、TTL Logic gate output low level , Call the logic gate in the open state , Also known as on state .

C、TTL Not the closing level of the door uOFF Refers to the maximum value of the low level allowed to be input at this time .

D、TTL Non door opening level uON Refers to the maximum value of the low level allowed to be input at this time .

Reference material 【 】

4、【 Single topic selection 】 As shown in the figure, the output signal of the circuit is ( )

A、 High level

B、 Low level

C、 High resistance state

D、 Not sure

Reference material 【 】

5、【 Single topic selection 】 Which of the following logic gate symbols represents a “ Highly efficient two input and non tristate gates at the control end ”.( )

A、

B、

C、

D、

Reference material 【 】

6、【 Single topic selection 】 The following circuits are TTL Gate circuit , Can achieve  The circuit of is ( ).

The circuit of is ( ).

A、

B、

C、

D、

Reference material 【 】

7、【 Multiple choice 】 Logical variables only 0、1 Two values ; In positive logic rules, use ( ) Corresponding to .

A、 High level 、 Low level

B、 Low level 、 High level

C、UH、UL

D、UL、UH

Reference material 【 】

8、【 Multiple choice 】 In order to complete the logic function correctly ,TTL The transistors used inside the integrated logic gate can work in ( ).

A、 Cut off zone

B、 Conduction amplification area

C、 Saturated conduction region

D、 Reverse breakdown region

Reference material 【 】

9、【 Multiple choice 】 The following circuit can realize “ Line and ” The functions are ( ).

A、 NAND gate

B、 Three state output gate

C、 Open collector gate

D、 Open drain gate

Reference material 【 】

10、【 Multiple choice 】 And TTL Compared with digital integrated circuits ,CMOS The advantage of digital integrated circuit is ( ).

A、 Micro power consumption

B、 high velocity

C、 High anti-interference ability

D、 Wide power range

Reference material 【 】

11、【 Judgment questions 】TTL When the logic gate works , If an input is suspended , Its working condition is equivalent to that the terminal is connected to the logic low level .( )

A、 correct

B、 error

Reference material 【 】

12、【 Judgment questions 】 The processing principle of redundant input of logic gate circuit is to ensure the correct logic function , Connect the redundant input to determine the level .( )

A、 correct

B、 error

Reference material 【 】

The first 5 Chapter operation 1—— New questions ( common 2 topic )

The first 5 Chapter operation 2—— Advanced questions ( common 2 topic )

The first 5 Chapter Representation of logic function and simplification of unit test (1)

1、【 Single topic selection 】 Logical functions  It is reduced to ( ).

It is reduced to ( ).

A、

B、

C、

D、

Reference material 【 】

2、【 Single topic selection 】 Logical functions  It is reduced to ( ).

It is reduced to ( ).

A、

B、

C、

D、

Reference material 【 】

3、【 Single topic selection 】 Logical functions  The simplest form of is ( ).

The simplest form of is ( ).

A、

B、

C、

D、

Reference material 【 】

4、【 Single topic selection 】 Logical functions  The simplest and or expression of is ( ).

The simplest and or expression of is ( ).

A、

B、

C、

D、

Reference material 【 】

5、【 Single topic selection 】 Logical functions  It is reduced to ( ).

It is reduced to ( ).

A、

B、

C、

D、

Reference material 【 】

6、【 Multiple choice 】 Logic function simplification formulas include ( ).

A、 Law of absorption 1

B、 Law of absorption 2

C、 Law of absorption 3

D、 Law of redundancy

Reference material 【 】

7、【 Judgment questions 】 The simplest expression of a logical function is unique .( )

A、 correct

B、 error

Reference material 【 】

The first 5 Chapter Representation of logic function and simplification of unit test (2)

1、【 Single topic selection 】 The Karnaugh circle on a Karnaugh map is shown in the figure , The simplification result is ( ).

A、

B、

C、

D、

Reference material 【 】

2、【 Single topic selection 】 In the following functions , Is the form of the least term expression ( ).

A、

B、

C、

D、

Reference material 【 】

3、【 Single topic selection 】 Simplify Chinese with Karnaugh map method of logical function , Four adjacent items can be merged into one , It can ( )

A、 elimination 1 Variables with different forms , Keep the same variables

B、 elimination 2 Variables with different forms , Keep the same variables

C、 elimination 3 Variables with different forms , Keep the same variables

D、 elimination 4 Variables with different forms , Keep the same variables

Reference material 【 】

4、【 Single topic selection 】 The reduction result of Karnaugh cycle on the following Karnaugh map is wrong ( ).

A、

B、

C、

D、

Reference material 【 】

5、【 Single topic selection 】 The Karnaugh map of a known logic function is shown in the figure , The logical expression is ( ).<img src="//img.inotgo.com/imagesLocal/202202/07/202202071738100598_94.jpg> A、

B、

C、

D、

Reference material 【 】

6、【 Single topic selection 】 Logical functions  The simplest and or of is ( ).

The simplest and or of is ( ).

A、

B、

C、

D、

Reference material 【 】

7、【 Judgment questions 】 The product of any two minimum terms of a logical function must be 1.( )

A、 correct

B、 error

Reference material 【 】

8、【 Judgment questions 】 The two smallest terms that are geometrically adjacent on a Karnaugh map must be logically adjacent to each other .( )

A、 correct

B、 error

Reference material 【 】

The first 6 Chapter operation 1—— New questions ( common 2 topic )

The first 6 Chapter operation 2—— Advanced questions ( common 3 topic )

The first 6 Chapter Combinational logic circuit unit test (1)

1、【 Single topic selection 】 In the analysis of combinational logic circuits , The resulting ( ), From this summary, we can get the specific logical function expression .

A、 Logical expression

B、 Truth table

C、 Logic circuit diagram

D、 Karnaugh map

Reference material 【 】

2、【 Single topic selection 】 Analyze the combinational logic circuit shown in the figure below , The correct output logic expression is ( ).

A、

B、

C、

D、

Reference material 【 】

3、【 Single topic selection 】 We know the truth table of the following logic function , The standard and or formula of its output is ( ).<img src="//img.inotgo.com/imagesLocal/202202/07/202202071738100598_17.jpg> A、

B、

C、

D、

Reference material 【 】

4、【 Single topic selection 】 Figure full adder symbol , When A = 0,B = 1,CI = 1 when ,S and CO Respectively ( ).

A、CO=0,S=0

B、CO=1,S=0

C、CO=0,S=1

D、CO=1,S=1

Reference material 【 】

5、【 Single topic selection 】 In the following statement , The wrong is ( ).

A、 Whether half adder or full adder , The output signal includes the carry of the high bit after adding the standard .

B、n Bit binary number addition process , Except for the addition of the lowest order, the addition of all other bits is full addition .

C、 The semi addition process can be regarded as a carry input of 0 Total addition of .

D、 When the multi position full adder works , The input carry signal of the low-order addition unit is the output carry signal of the high-order addition unit .

Reference material 【 】

6、【 Single topic selection 】 In the following statement , The wrong is ( ).

A、1 Bit binary number comparator , Finger can distinguish two 1 The circuit of the size relationship of bit binary numbers .

B、4 Bit binary number comparator , Finger can distinguish four 1 The circuit of the size relationship of bit binary numbers .

C、 The output result of the numerical comparator can be in a highly efficient way , It can also be expressed in a low efficiency way .

D、 Compare the two n Size of digits , It should be compared bit by bit from high to low , When someone has a size difference , There is no need to compare at a lower level .

Reference material 【 】

The first 6 Chapter Combinational logic circuit unit test (2)

1、【 Single topic selection 】4 Bit binary decoder has ( ) Output signal terminals .4 Bit binary decoder has ( ) Output signal terminals .

A、4

B、8

C、16

D、32

Reference material 【 】

2、【 Single topic selection 】 To expand, get 5-32 line decoder , need ( ) slice 3-8 line decoder .

A、1

B、2

C、3

D、4

Reference material 【 】

3、【 Single topic selection 】 If a binary encoder has 4 Bit output code , Then the encoder can at most ( ) Channel input signal coding .

A、4

B、8

C、16

D、32

Reference material 【 】

4、【 Single topic selection 】101 Encoder output of keyboard ( ) Bit binary code .

A、2

B、6

C、7

D、8

Reference material 【 】

5、【 Single topic selection 】 Application of binary decoder to achieve a 4 Input 、3 Output combinational logic circuit , At least use ( ) slice 3-8 line decoder 74LS138.

A、1

B、2

C、3

D、4

Reference material 【 】

6、【 Judgment questions 】 The encoded signals of the priority encoder are mutually exclusive , Multiple coded signals are not allowed to be valid at the same time .( )

A、 correct

B、 error

Reference material 【 】

7、【 Judgment questions 】 Light emitting diodes with different light colors can be made of a variety of semiconductor materials . When a reverse voltage is applied to the LED , Will emit clear visible light .( )

A、 correct

B、 error

Reference material 【 】

The first 6 Chapter Combinational logic circuit unit test (3)

1、【 Single topic selection 】 One 8 The data input of a data selector is ( ) individual .

A、1

B、2

C、8

D、4

Reference material 【 】

2、【 Single topic selection 】 One 16 The address input of a data selector is ( ) individual .

A、1

B、2

C、8

D、4

Reference material 【 】

3、【 Single topic selection 】 To achieve a 4 Input combinational logic function , Use ( ) Data selectors are best .

A、4 choose 1

B、8 choose 1

C、16 choose 1

D、32 choose 1

Reference material 【 】

4、【 Single topic selection 】 use 4 choose 1 Data selector implementation function  , Should make ( ).

, Should make ( ).

A、D0=D2=0,D1=D3=1

B、D0=D2=1,D1=D3=0

C、D0=D1=0,D2=D3=1

D、D0=D1=1,D2=D3=0

Reference material 【 】

5、【 Single topic selection 】 use 4 choose 1 Data selector implementation function  , Should make ( ).

, Should make ( ).

A、D0=0,D1=0,D2= A2,D3=A2

B、D0=1,D1=1, ,

,

C、D0=1,D1=0, ,D3=A2

,D3=A2

D、D0=0,D1=1,D2=1,D3= A2

Reference material 【 】

6、【 Single topic selection 】 In the following statement , The right is ( ).

A、 Compared with binary decoder , Data selector is more suitable for realizing multiple output logic function .

B、 To implement a four input logic function , Use 16 choose 1 Data selectors are best .

C、 To implement a three input logic function , Out of commission 4 choose 1 Data selector .

D、 To implement a four input logic function , You can use it first 4 choose 1 The data selector is extended to 8 choose 1 Data selector , Then apply to realize .

Reference material 【 】

7、【 Single topic selection 】 The cause of competition and adventure in combinational logic circuits is ( ).

A、 Logical relation error

B、 interference signal

C、 Circuit operation delay

D、 The power supply is unstable

Reference material 【 】

The first 7 Chapter operation 1—— New questions ( common 2 topic )

The first 7 Chapter operation 2—— Advanced questions ( common 2 topic )

The first 7 Chapter Trigger unit test (1)

1、【 Single topic selection 】 Sequential logic circuit consists of combinational logic devices and ( ) Co constitute .

A、 trigger

B、 Decoder

C、 Exclusive OR gate

D、 Data selector

Reference material 【 】

2、【 Single topic selection 】 It is divided according to whether the working time of the trigger in the circuit is unified , Sequential logic circuits can be divided into ( ) Two types of .

A、 Millie type and Moore type

B、 Synchronous sequential circuit and asynchronous sequential circuit

C、 Counters and registers

D、 Medium scale integrated devices and large scale integrated devices

Reference material 【 】

3、【 Single topic selection 】 Trigger is a ( ) Steady state circuit .

A、 nothing

B、 single

C、 double

D、 many

Reference material 【 】

4、【 Single topic selection 】 For the basic structure of NAND gates RS trigger , When the trigger state is set to 1 when ,( ).

A、S=0; R=0

B、S=0; R=1

C、S=1; R=0

D、S=1; R=1

Reference material 【 】

5、【 Single topic selection 】RS Input excitation of trigger “R” Refer to ( ).

A、 repeat

B、 Reset

C、 Set up 1

D、 Flip

Reference material 【 】

6、【 Single topic selection 】 An input excitation is highly effective RS trigger , Its characteristic equation is ( ).

A、

B、

C、

D、

Reference material 【 】

7、【 Judgment questions 】 A trigger has two possible output states , Or 1, Or 0.( )

A、 correct

B、 error

Reference material 【 】

The first 7 Chapter Trigger unit test (2)

1、【 Single topic selection 】 Among various trigger function types , The most complete functions 、 The most versatile trigger is ( ).

A、RS trigger

B、JK trigger

C、D trigger

D、T trigger

Reference material 【 】

2、【 Single topic selection 】 An input excitation is highly effective JK trigger , stay J=K=1 when , The clock pulse operating point appears , Then trigger ( ).

A、 To remain in the same state

B、 Set up 1

C、 Set up 0

D、 Flip

Reference material 【 】

3、【 Single topic selection 】 An input excitation is highly effective JK trigger , Its characteristic equation is ( ).

A、

B、

C、

D、

Reference material 【 】

4、【 Single topic selection 】 The logic circuit is shown in the figure , analysis C Waveform of , When the initial state is “0” when , Output Q yes “1” The moment is ( ).<img src="//img.inotgo.com/imagesLocal/202202/07/202202071738100598_114.jpg> A、t1

B、t2

C、t3

D、t4

Reference material 【 】

5、【 Single topic selection 】 The logic circuit is shown in the figure , It has ( ).

A、D Trigger function

B、T Trigger function

C、RS Trigger function

D、 Keep function

Reference material 【 】

6、【 Single topic selection 】 The logic circuit is shown in the figure , It has ( ).

A、D Function of trigger ;

B、 Function of shift register ;

C、T Function of trigger ;

D、SR Function of trigger .

Reference material 【 】

7、【 Judgment questions 】 Sync RS The input excitation signal of the trigger R、S Than the input clock signal CLK The signal priority of is high .

A、 correct

B、 error

Reference material 【 】

8、【 Judgment questions 】 And RS Triggers are similar to ,JK Triggers also do not allow two input excitations to be valid at the same time .( )

A、 correct

B、 error

Reference material 【 】

The first 8 Chapter operation 1—— New questions ( common 2 topic )

The first 8 Chapter operation 2—— Advanced questions ( common 3 topic )

The first 8 Chapter Sequential logic circuit unit test (1)

1、【 Single topic selection 】 The following devices do not belong to sequential logic circuits ( ).

A、 Encoder

B、 Counter

C、 trigger

D、 register

Reference material 【 】

2、【 Single topic selection 】 Sequential logic circuit must contain ( ).

A、 trigger

B、 Combinational logic device

C、 shift register

D、 Decoder

Reference material 【 】

3、【 Single topic selection 】 The difference between synchronous sequential logic circuit and asynchronous sequential logic circuit lies in asynchronous sequential logic circuit ( ).

A、 No triggers

B、 There is no unified clock control

C、 There is no steady state

D、 The output is related to the internal state

Reference material 【 】

4、【 Single topic selection 】 One by 3 When the synchronous sequential logic circuit composed of triggers works , All possible states are common ( ) individual .

A、3

B、6

C、8

D、16

Reference material 【 】

5、【 Judgment questions 】 A sequential logic circuit has self starting ability , It must have the ability of self correction ; It has no self-tuning ability , It is possible to have self starting ability .( )

A、 correct

B、 error

Reference material 【 】

6、【 Judgment questions 】 A hex counter with self starting ability can have invalid state , But there must be no invalid loop .

A、 correct

B、 error

Reference material 【 】

The first 8 Chapter Sequential logic circuit unit test (2)

1、【 Single topic selection 】M The characteristics of the state transition of the binary counter are : After setting the initial state , Every time ( ) A counting pulse , The counter returns to its initial state .

A、M-2

B、M-1

C、M

D、M+1

Reference material 【 】

2、【 Single topic selection 】 Press the state transition of the trigger and the clock CP The signal Classification of relationships , The counter can be divided ( ).

A、 Synchronous counter and asynchronous counter

B、 Addition counter and subtraction counter

C、 Binary counter and decimal counter

D、 Large modulus counter and small modulus counter

Reference material 【 】

3、【 Single topic selection 】 Divided by state migration order , Counters can be divided into addition counters 、 Subtraction counter and ( ).

A、 Binary counter

B、 Decimal counter

C、 Synchronous counter

D、 Reversible counter

Reference material 【 】

4、【 Single topic selection 】 To realize the hex addition counter , Internal use required ( ) Trigger .

A、1

B、2

C、3

D、4

Reference material 【 】

5、【 Single topic selection 】 Analyze the waveform of the counter shown in the figure , It is known that it is a ( ).

A、 Quinary counter

B、 Hex counter

C、 Hex counter

D、 Octal counter

Reference material 【 】

6、【 Single topic selection 】 To achieve a 7 Binary addition counter , Need to use ( ) slice 10 Binary addition counter .

A、1

B、2

C、3

D、4

Reference material 【 】

7、【 Single topic selection 】 One is known to contain 4 Synchronous addition counter of triggers , Its counting modulus cannot be ( ).

A、10

B、12

C、16

D、20

Reference material 【 】

8、【 Single topic selection 】 In the state diagram of the following sequential circuits , With self starting function ( )

A、

B、

C、

D、

Reference material 【 】

9、【 Judgment questions 】 When using large modulus counter to realize small modulus counter , The difference between the zero clearing method and the number setting method lies in the difference in the starting point of the working cycle of the design goal .

A、 correct

B、 error

Reference material 【 】

10、【 Judgment questions 】 Use 4 Bit binary synchronous addition counter 74LS161 Realization 256 Hexadecimal addition counter , It can only be extended synchronously , Cannot extend asynchronously .

A、 correct

B、 error

Reference material 【 】

The first 8 Chapter Sequential logic circuit unit test (3)

1、【 Single topic selection 】 To achieve the right 50 Bit binary number storage function , Circuit needs ( ) A trigger consists of .

A、25

B、50

C、100

D、500

Reference material 【 】

2、【 Single topic selection 】n Twisted ring counter composed of bit trigger , The number of invalid states is ( ) individual .

A、

B、

C、

D、

Reference material 【 】

3、【 Single topic selection 】n Ring counter composed of bit trigger , Its counting modulus is ( ).

A、

B、2n

C、2n-1

D、n

Reference material 【 】

4、【 Single topic selection 】 There is a left shift register , When pre placed 1011 after , Its serial input is fixed 0, Later on 4 A shift pulse CP Under action , The shift process of four bit data is ( ).

A、1011–0110–1100–1000–0000

B、1011–0101–0010–0001–0000

C、1011–1100–1101–1110–1111

D、1011–1010–1001–1000–0111

Reference material 【 】

The first 9 Chapter Pulse waveform generation and shaping unit test

1、【 Single topic selection 】 When describing a rectangular pulse , The so-called duty cycle refers to ( ).

A、 The ratio of pulse amplitude to pulse period

B、 The ratio of pulse rise time to pulse fall time

C、 The ratio of pulse width to pulse period

D、 The ratio of pulse width to pulse amplitude

Reference material 【 】

2、【 Single topic selection 】 Here's about 555 In the expression of timer , The wrong is ( )

A、555 Timer 3 The pin is the output signal end

B、555 Timer 4 The pin is a direct reset end in a highly effective way

C、555 Timer 6 Pin and 2 Pins are two input excitation terminals with different effective ways

D、555 Timer 5 The pin is the threshold control end

Reference material 【 】

3、【 Single topic selection 】555 When the timer works , Threshold control end 5 Pins should be used when not in use ( ).

A、 the

The capacitor is grounded

The capacitor is grounded

B、 Direct ground

C、 In the air

D、 Directly connect to the positive power supply

Reference material 【 】

4、【 Single topic selection 】 One of the differences between multivibrator and monostable trigger is ( ).

A、 The former has 2 A steady state , The latter only 1 A steady state

B、 The former has no steady state , The latter have 2 A steady state

C、 The former has no steady state , The latter only 1 A steady state

D、 Both have only 1 A steady state , But the steady state of the latter requires certain external signals to maintain

Reference material 【 】

5、【 Single topic selection 】 As shown by 555 The name of the timer composition circuit is ( )

A、 Schmidt trigger

B、 Multivibrator

C、 Bistable trigger

D、 Monostable trigger

Reference material 【 】

6、【 Judgment questions 】 Schmidt trigger has waveform shaping , The function of filtering interference .

A、 correct

B、 error

Reference material 【 】

7、【 Judgment questions 】 Multivibrator is a self-excited oscillation circuit , No input excitation signal .

A、 correct

B、 error

Reference material 【 】

边栏推荐

- Keyword static

- Universal crud interface

- 深度解析链动2+1模式,颠覆传统卖货思维?

- [Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 14

- What should we pay attention to when using the built-in tool to check the health status in gbase 8C database?

- Zero foundation self-study STM32 - Review 2 - encapsulating GPIO registers with structures

- Dachang image library

- Maturity of master data management (MDM)

- 球面透镜与柱面透镜

- [postgraduate entrance examination English] prepare for 2023, learn list5 words

猜你喜欢

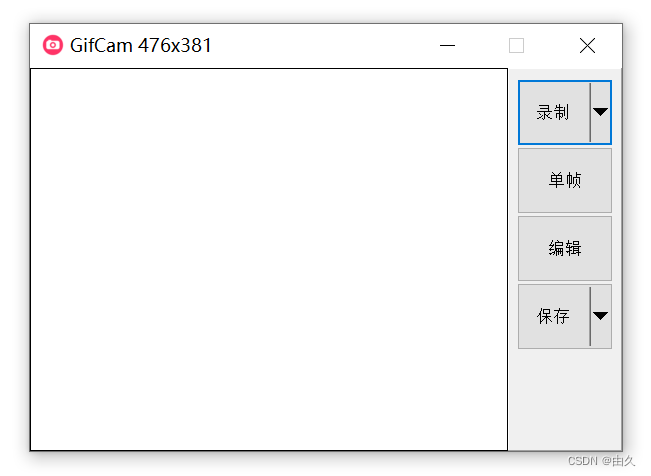

GifCam v7.0 极简GIF动画录制工具中文单文件版

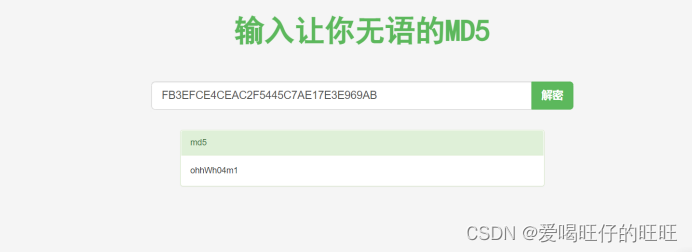

全国大学生信息安全赛创新实践赛初赛---misc(永恒的夜)

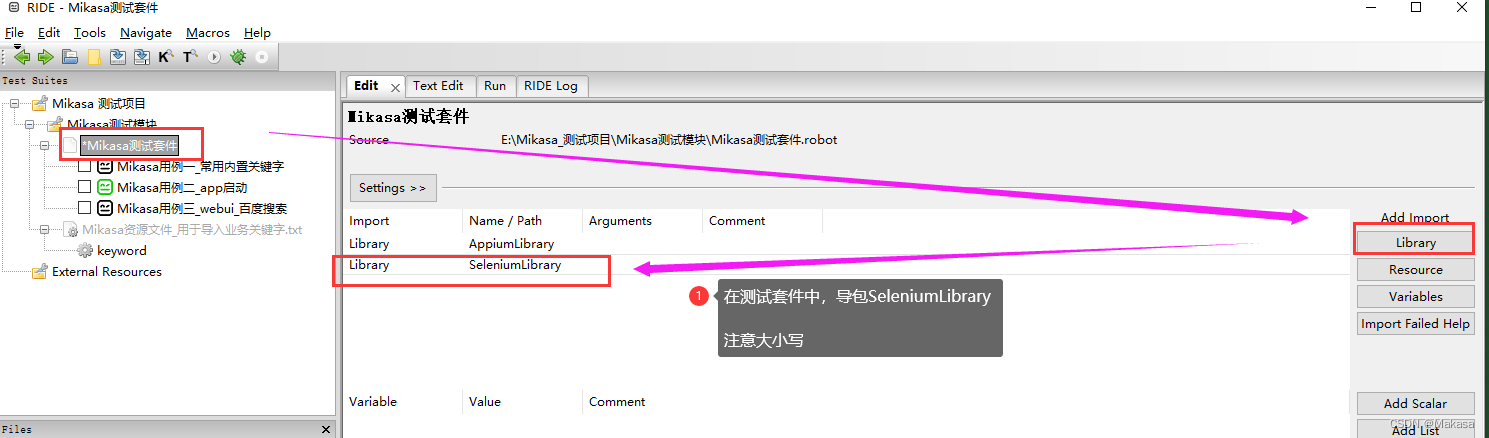

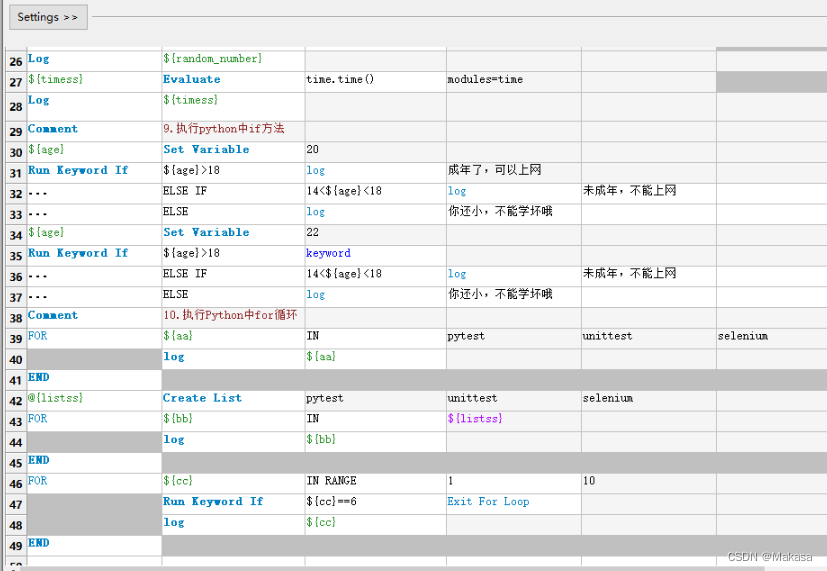

RobotFramework入门(三)WebUI自动化之百度搜索

Yyds dry inventory comparison of several database storage engines

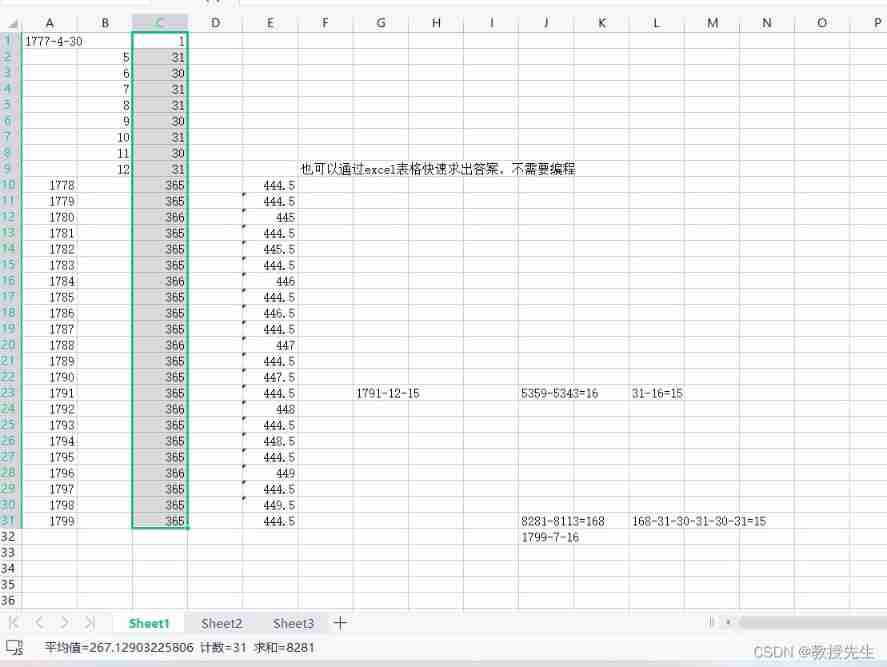

Blue Bridge Cup group B provincial preliminaries first question 2013 (Gauss Diary)

一个复制也能玩出花来

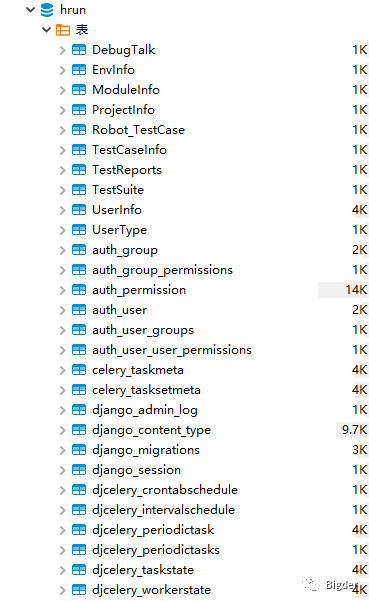

HttpRunnerManager安装(三)-Linux下配置myql数据库&初始化数据

Ue4- how to make a simple TPS role (II) - realize the basic movement of the role

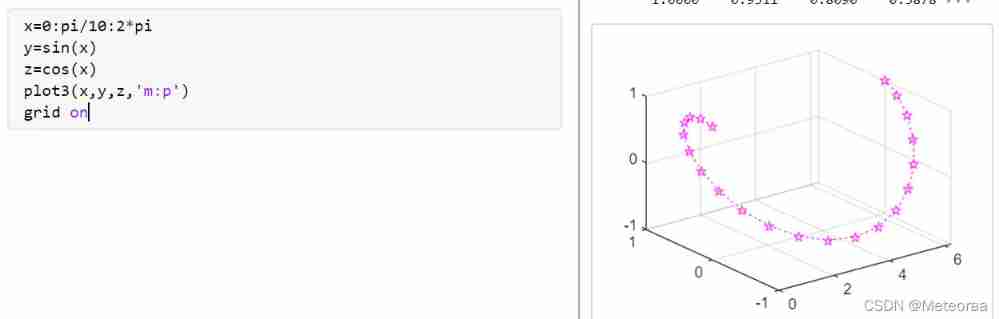

3D drawing ()

Introduction to robotframework (I) brief introduction and use

随机推荐

Pure QT version of Chinese chess: realize two-man, man-machine and network games

深度解析链动2+1模式,颠覆传统卖货思维?

Universal crud interface

Deeply analyze the chain 2+1 mode, and subvert the traditional thinking of selling goods?

Maturity of master data management (MDM)

Solution: attributeerror: 'STR' object has no attribute 'decode‘

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 6

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 12

3D drawing ()

构建库函数的雏形——参照野火的手册

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 13

Patch NTP server at the beginning of DDoS counterattack

UE4 - how to make a simple TPS role (I) - create a basic role

After changing the GCC version, make[1] appears in the compilation: cc: command not found

2345文件粉碎,文件强力删除工具无捆绑纯净提取版

零基础自学STM32-复习篇2——使用结构体封装GPIO寄存器

好用的 JS 脚本

我把驱动换成了5.1.35,但是还是一样的错误,我现在是能连成功,但是我每做一次sql操作都会报这个

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 14

Microsoft speech synthesis assistant v1.3 text to speech tool, real speech AI generator