当前位置:网站首页>谈fpga和asic的区别

谈fpga和asic的区别

2022-07-07 00:08:00 【IC观察者】

ASICer遇到FPGAer,驴唇不对马嘴。

ASIC还是FPGA,这是个问题。

很多人都觉得同样都是写Verilog的,对于前端设计来说,FPGA和ASIC没什么区别,其实不然,从某种程度上来说,我觉得这就是两个行业。

复位不同

因为Xlinx的器件原因,Xilinx推荐高电平复位,在ASIC通常都是低电平复位。没听说过做芯片高电平复位的。

工具流差别大

FPGA开发大多是在Windows环境下开发,一个编辑器,一个Vivado可以走到底,下载bit流到开发板。一个人全流程。

ASIC开发基本都在Linux环境下开发,编译用VCS、debug用Veridi,清lint/CDC/RDC用Splayglass,收覆盖率imc,综合用DC,形式验证formality,后端做PR,DFT一直到GDSII的系列工具。需要一个完整团队,才能做出一颗芯片。

代码质量要求差别

FPGA开发,代码验证完,可以直接应Vivado自带的综合PR下板子验证。基本就没问题。

ASIC代码验证完,需要清除lint。因为很多写法是不可综合的。清完lint,进入综合,但fomal不一定能过,代码和综合后的网表对不上。综合、fomal不过,代码写得再牛逼,再快,验证的再好,也得改,重写。

ASIC的代码可以换成FPGA IP,直接放FPGA上验证,但FPGA的代码想要直接流片,还是有一段很长的路要走。

FPGA验证也因为规模小的原因,很少听说用UVM的。而且FPGA工程师一般是自己设计自己验,然后自己下板调试,trace。一人全流程。FPGA工程师基本做FPGA产品。如果有人把芯片验证认为是测试,正是无知的体现。

ASIC验证方法学UVM已经统一。验证流程也十分完善,testpoint、testcase、testplan,regression,随机,覆盖率,后仿。到系统级别的验证更是设计到软硬件交互验证,加速器验证等,最后才到了上FPGA原型验证。而FPGA基本就是调接口,测软件,基本上很少会发现RTL的bug。

都叫综合/PR,但本质不同

FPGA内部的构造大致来说,LUT实现组合逻辑,D触发器实现时序逻辑,再加上一些BRAM,硬核资源,就可以实现任意电路。所以FPGA的综合就是把RTL映射到这些资源上。

ASIC综合是将RTL映射到标准单元库上,mem。有些RTL,语法是支持,但是就是综合不了。LUT就是个大mux,瞎写的代码LUT能映射,但DC不一定过。

FPGA综合和ASIC综合完全不是一个东西。

FPGA在ASIC中的角色

FPGA在ASIC开发流程中的作用,只是用做原型验证。前面复杂的开发流程,与FPGA自成体系的开发流程相比完全不是一个量级。

你用做芯片的方法去做FPGA那是降维打击,用FPGA的方法做芯片,那叫本末倒置。

但做芯片流程复杂,放到做FPGA产品上,会造成资源浪费,杀鸡焉用牛刀。

玩法不一样

FPGA玩的是什么,是灵活性高,需求不明确,量不大,或者需求老变化,FPGA正是派上用场。

ASIC玩的就是要量产,量越大越好。需求明确,市场定位明确,未来几年内都可以不断出货。

功耗

FPGA产品设计很少关注功耗,都是插电使用的板卡。

ASIC低功耗设计又是一套设计方法学,从RTL设计,到power gating,power domain的设计,upf编写。低功耗的验证。同样的电路,FPGA的功耗也会大。

面积

如果一个产品,只是小批量出货,用FPGA实现会减少成本。但如果到了百万级别的产品量还用FPGA,那钱不都让Xilinx赚了。代码规模大,用FPGA实现困难,成本高昂。同样的电路,FPGA的面积会比ASIC大很多

通才和专才

FPGA规模小,而且是直接面向产品,FPGA工程师可以出全栈工程师,软硬件全流程覆盖。直接面向产品更有意思。

ASIC设计流程众多,岗位细分,每个人更多的只能覆盖到自己的那一部分工作。做算法IP设计的,可能不用关注中端实现过程,甚至不知道自己正在做的这个IP会用到哪个产品上。做IP会出专才,专注于协议或算法。而SOC设计又是另一套方法学体系。

FPGA其实和软件类似

想一想,类似于做软件开发,代码开发验证完成出版本,然后上开发板去测。出现问题,回来再继续改代码。产品上市了,发现了一个bug,远程OTA打个补丁,升级一下。

ASIC总不能流片一下,试一下,几千万就叫你试一下?产品到客户手里了,发现bug了,那是非常严重,召回。这一批次都废掉。

可能就是因为这样的原因,做芯片必须步步小心。流片失败,对于很多公司来说,就是倒闭灾难。

最后

以上,种种因素,造成了FPGA和ASIC整套研发流程体系不同,所以我认为严格来说,做FPGA和做ASIC就是两个行业。

更多内容可以关注(芯片记语)公众号。

原文:https://mp.weixin.qq.com/s/QgmhX4DRSXW4yly9TJysPQ

边栏推荐

- async / await

- Tablayout modification of customized tab title does not take effect

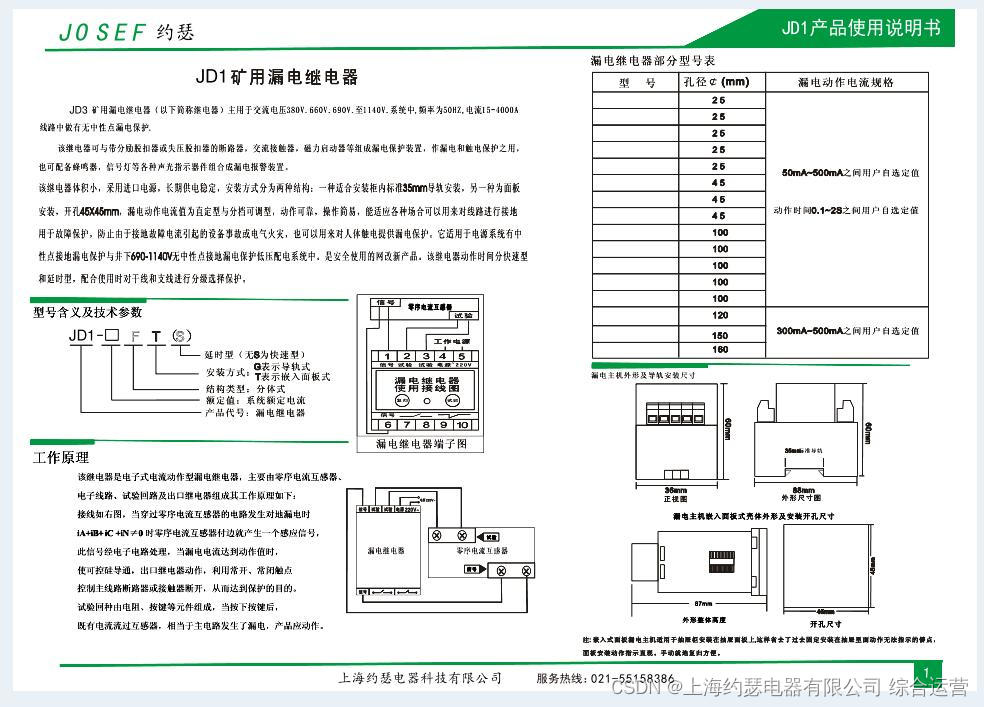

- Dj-zbs2 leakage relay

- Pinduoduo product details interface, pinduoduo product basic information, pinduoduo product attribute interface

- Design, configuration and points for attention of network arbitrary source multicast (ASM) simulation using OPNET

- An example of multi module collaboration based on NCF

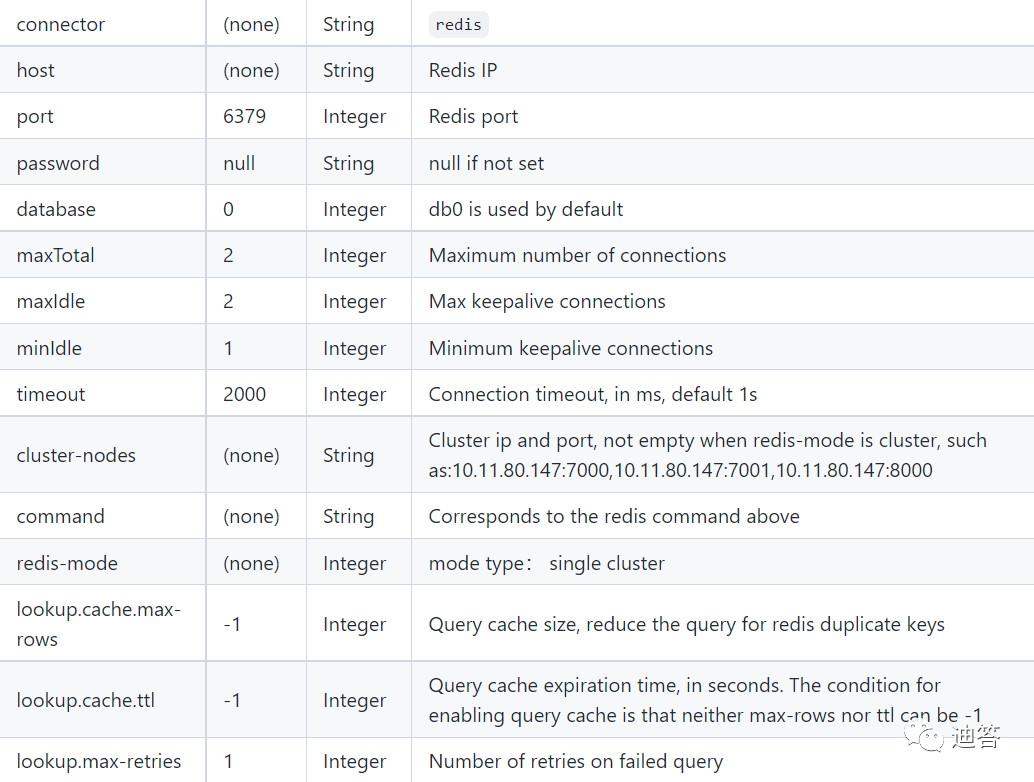

- Flink SQL realizes reading and writing redis and dynamically generates hset key

- [reading of the paper] a multi branch hybrid transformer network for channel terminal cell segmentation

- 如何提高网站权重

- K6el-100 leakage relay

猜你喜欢

I didn't know it until I graduated -- the principle of HowNet duplication check and examples of weight reduction

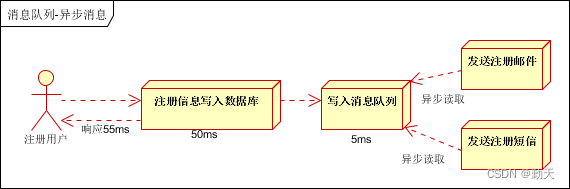

What is message queuing?

How Alibaba cloud's DPCA architecture works | popular science diagram

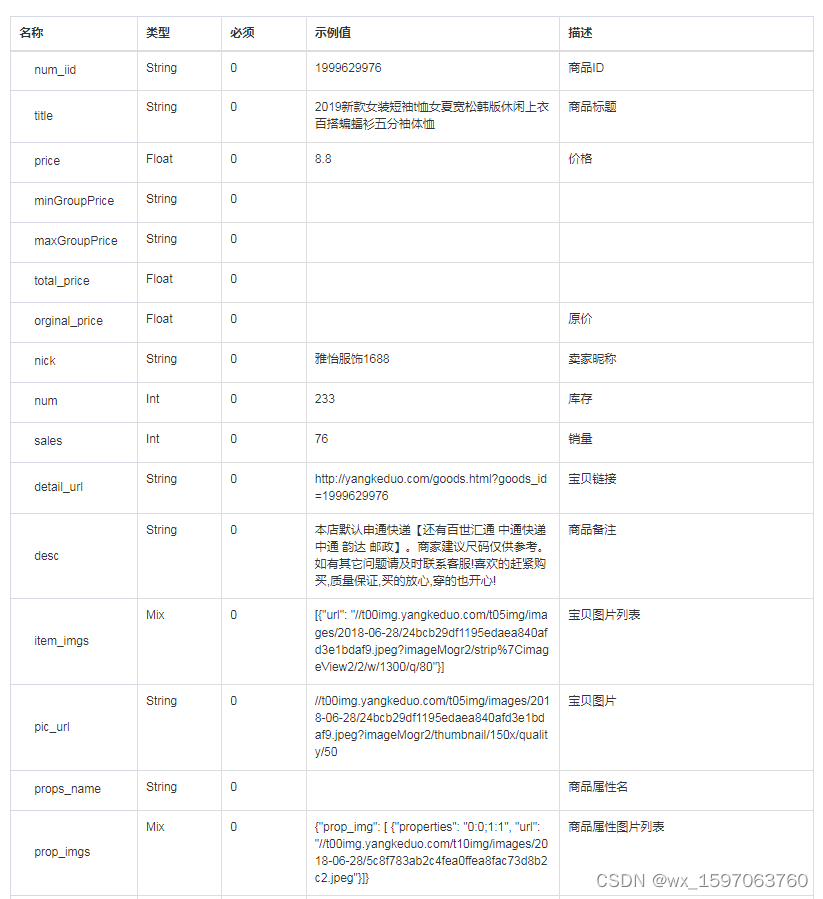

拼多多商品详情接口、拼多多商品基本信息、拼多多商品属性接口

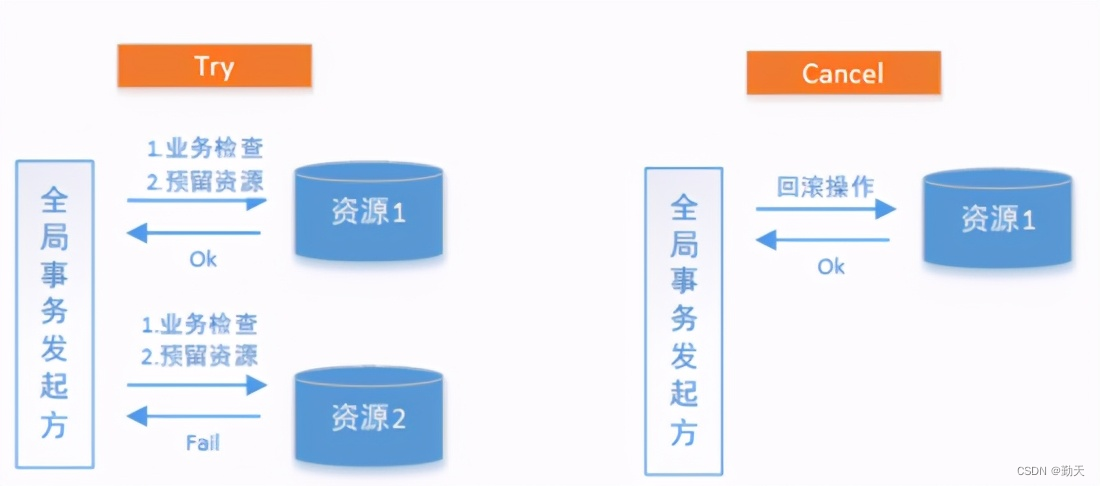

分布式事务解决方案之TCC

Leakage relay jd1-100

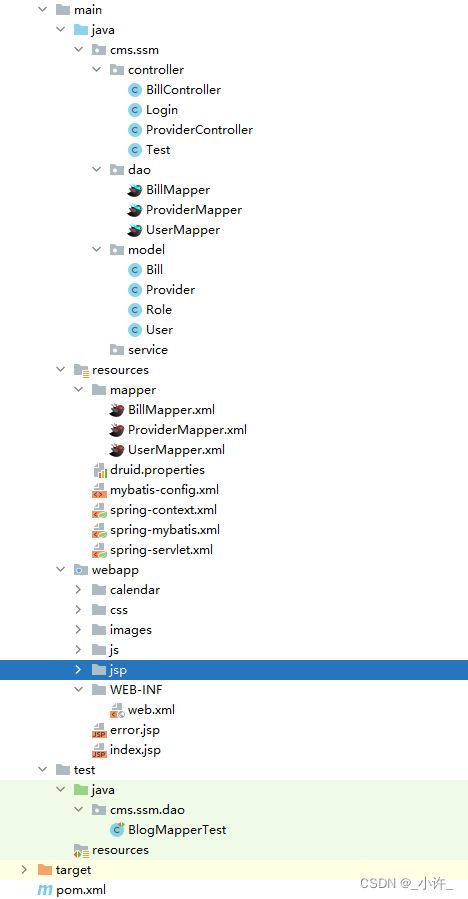

Simple case of SSM framework

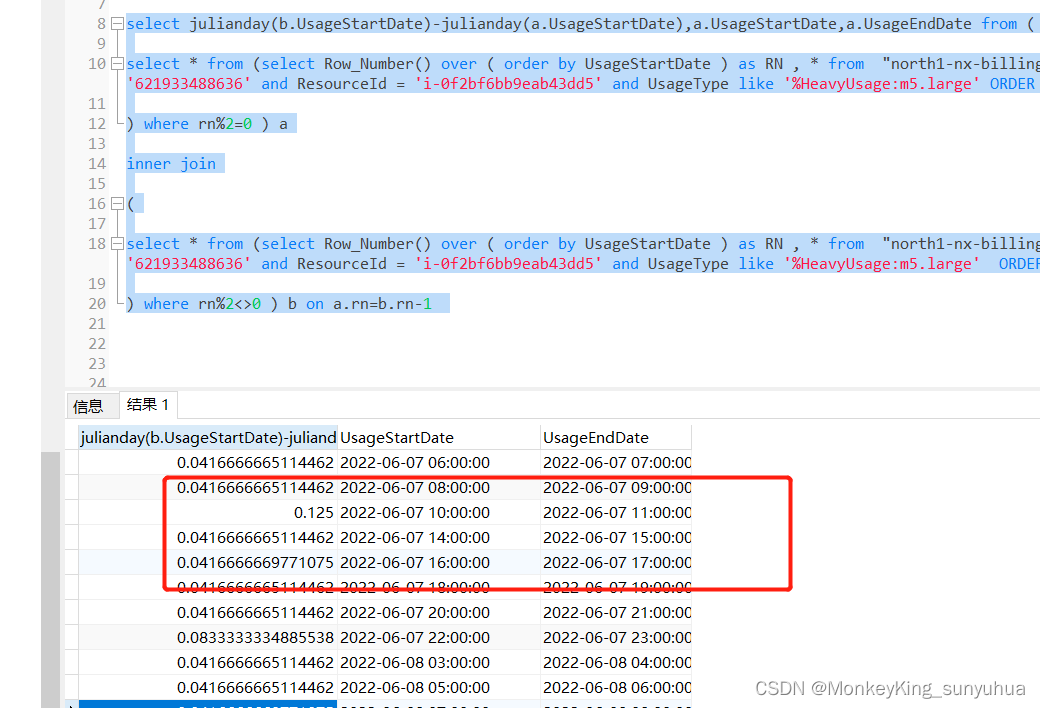

sql查询:将下一行减去上一行,并做相应的计算

Flink SQL 实现读写redis,并动态生成Hset key

Flink SQL realizes reading and writing redis and dynamically generates hset key

随机推荐

Sidecar mode

C#可空类型

What is dependency injection (DI)

2pc of distributed transaction solution

EMMC打印cqhci: timeout for tag 10提示分析与解决

论文阅读【MM21 Pre-training for Video Understanding Challenge:Video Captioning with Pretraining Techniqu】

毕业之后才知道的——知网查重原理以及降重举例

上海字节面试问题及薪资福利

Unity keeps the camera behind and above the player

nVisual网络可视化

JVM the truth you need to know

分布式事务介绍

Simple case of SSM framework

pytorch_ 01 automatic derivation mechanism

App clear data source code tracking

[paper reading] semi supervised left atrium segmentation with mutual consistency training

"Multimodal" concept

论文阅读【Semantic Tag Augmented XlanV Model for Video Captioning】

Mybaits multi table query (joint query, nested query)

Three level menu data implementation, nested three-level menu data