当前位置:网站首页>Résumé de la structure du modèle synthétisable

Résumé de la structure du modèle synthétisable

2022-07-06 07:08:00 【Alors, le plat.】

Un.、Structure du modèle synthétisable

Si le programme n'est utilisé que pour la simulation,Alors presque tous les énoncés de syntaxe et de programmation peuvent être utilisés.Mais si le programme est utilisé pour l'implémentation matérielle,Nous devons donc garantir l'exhaustivité des procédures,C'est - à - dire que le programme écrit peut être synthétisé Conversion à la structure de circuit correspondante.IncomparableHDLLes déclarations sont ignorées ou mal déclarées lorsqu'elles sont synthétisées à l'aide d'outils composites.En tant que concepteur,Il faut comprendre la structure des modèles intégrables.

Bien que différents outils de synthèseVerilog HDLLa structure syntaxique est prise en charge différemment,Mais...Verilog HDLCertaines structures typiques sont explicitement soutenues ou non par tous les outils intégrés.

(1)Un noeud supporté par tous les outils intégrés Structure:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter.

(2)Structure non prise en charge par tous les outils intégrés:time,defparam,$finish,fork,join,initial,delays,UDP,wait.

(3) Certains outils supportent des structures que d'autres ne supportent pas :casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while.

Donc,, Pour écrire un modèle intégré , Les structures soutenues par tous les outils intégrés devraient être décrites dans la mesure du possible. , Afin d'assurer l'exactitude de la conception et de raccourcir la période de conception .

2.、 Principes pour l'établissement de modèles intégrables

Pour garantirVerilog HDL Exhaustivité des énoncés d'affectation , Les points suivants doivent être pris en considération lors de la modélisation :

(1) N'utilisez pas l'instruction d'initialisation .

(2) N'utilisez pas de description avec retard .

(3) N'utilisez pas une instruction de boucle avec un nombre indéterminé de boucles ,Par exemple:forever、whileAttendez..

(4) N'utilisez pas de primitifs personnalisés par l'utilisateur (UDPÉlément).

(5) Essayez de concevoir le circuit de façon synchrone .

(6) Sauf si c'est la conception du chemin critique , En général, la méthode d'appel des éléments de porte n'est pas utilisée pour décrire la conception. , Il est recommandé d'utiliser des énoncés de comportement pour compléter la conception .

(7)Avecalways Description du bloc de processus logique combinatoire , Tous les signaux d'entrée doivent être énumérés dans la liste des signaux sensibles. .

(8) Tous les registres internes doivent pouvoir être réinitialisés ,En serviceFPGA Lors de la réalisation de la conception , Dans la mesure du possible, l'extrémité de Réinitialisation globale du dispositif doit être utilisée comme Réinitialisation globale du système. .

(9) Description et modélisation de la logique temporelle , L'affectation non bloquante doit être utilisée autant que possible . Description et modélisation de la logique combinatoire , Vous pouvez assigner une valeur avec un blocage , Vous pouvez également assigner des valeurs non bloquantes . Mais dans le même bloc de processus , Il est préférable de ne pas utiliser à la fois l'assignation de blocage et l'assignation de non - blocage .

(10) Pas plus d'un always Assigner une valeur à la même variable dans le bloc de processus . Vous ne pouvez pas utiliser les deux assignations de blocage pour le même objet d'affectation , Encore une fois, l'affectation non bloquante .

(11) Si vous n'avez pas l'intention de déduire la variable dans le loquet ,Il faut doncifDéclaration oucase Les variables sont explicitement assignées dans toutes les branches conditionnelles de l'instruction .

(12) Évitez de mélanger les déclencheurs déclenchés par le bord ascendant et le bord descendant .

(13) L'assignation d'une même variable ne peut pas être contrôlée par plusieurs horloges , Ne peut pas non plus être soumis à deux conditions d'horloge différentes ( Ou un autre bord d'horloge )Contrôle.

(14)Évitez decase Utilisé dans l'entrée de branche de l'instruction xValeur ouzValeur.

Trois、Blocage et non - blocage

Il est recommandé d'utiliser des assignations non bloquantes lors de la modélisation logique séquentielle . Parce que pour une affectation bloquante , L'ordre des énoncés d'affectation a une influence directe sur le résultat final de la synthèse. , Un peu de négligence de la part du concepteur peut entraîner une combinaison de résultats et de livres de conception Les significations sont très différentes . Et si une affectation non bloquante est utilisée , L'ordre dans lequel les énoncés d'affectation sont disposés peut être ignoré , Il suffit de décrire clairement la connexion . Comme le modèle ci - dessous :

always @ (posedge clkA) //Label AwA

… = DataOut; //LireDataOutValeur de

always @ (posedge clkA) //Label AwB

DataOut <= …; // Utiliser une affectation non bloquante

Si vous changez le modèle ci - dessus en affectation de blocage “DataOut = …”, Simuler ceux - ci dans l'ordre d'écriture du programme alwaysDéclarations,InclkA Au bord ascendant ,alwaysDéclarationsAwAJe l'ai lu.DataOutValeur actuelle de,Et puisalwaysDéclarations AwBEncore.DataOutAssigner une nouvelle valeur. Si ces deux - là sont inversés alwaysOrdre des déclarations( Ou l'émulateur choisit de reprogrammer les deux alwaysOrdre d'exécution des déclarations),Alors exécutez d'abord alwaysDéclarationsAwB, Provoque l'attribution de nouvelles valeurs à DataOut,Par la suitealwaysDéclarationsAwA C'est ce qu'on lit après la mise à jour DataOutValeur. Ça semble dû à always Quand toutes les déclarations peuvent être exécutées ,VersDataOut L'affectation a eu lieu et s'est terminée en zéro temps . Donc, selon lequel exécuter en premier alwaysDéclarations,AwALire dansDataOut La valeur peut être sa valeur originale , Ou sa nouvelle valeur .

L'utilisation d'assignations non bloquantes élimine la dépendance de ce comportement de simulation ,À ce moment - là,,LireDataOut Se produit à l'heure actuelle , Et à la fin du cycle de simulation actuel ( C'est - à - dire que toutes les variables ont été lues ) Pour ajouter une nouvelle valeur ÀDataOut. De cette façon, le comportement du modèle ci - dessus n'est plus soumis à always L'effet de l'ordre d'exécution des déclarations .Donc,,Dans unalways Une variable est assignée à l'intérieur d'une instruction dans laquelle always Lire en dehors de l'instruction Variables, L'instruction d'assignation doit alors être une assignation non bloquante .

边栏推荐

- leetcode6109. 知道秘密的人数(中等,周赛)

- BUU的MISC(不定时更新)

- Lesson 12 study notes 2022.02.11

- Oracle database 11gr2 uses TDE transparent data encryption to report an error ora28353. If you run to close the wallet, you will report an error ora28365. If you run to open the wallet, you will repor

- [server data recovery] case of offline data recovery of two hard disks of IBM server RAID5

- 树莓派串口登录与SSH登录方法

- Call, apply, bind rewrite, easy to understand with comments

- CDN acceleration and cracking anti-theft chain function

- leetcode704. 二分查找(查找某个元素,简单,不同写法)

- 升级版手机检测微信工具小程序源码-支持多种流量主模式

猜你喜欢

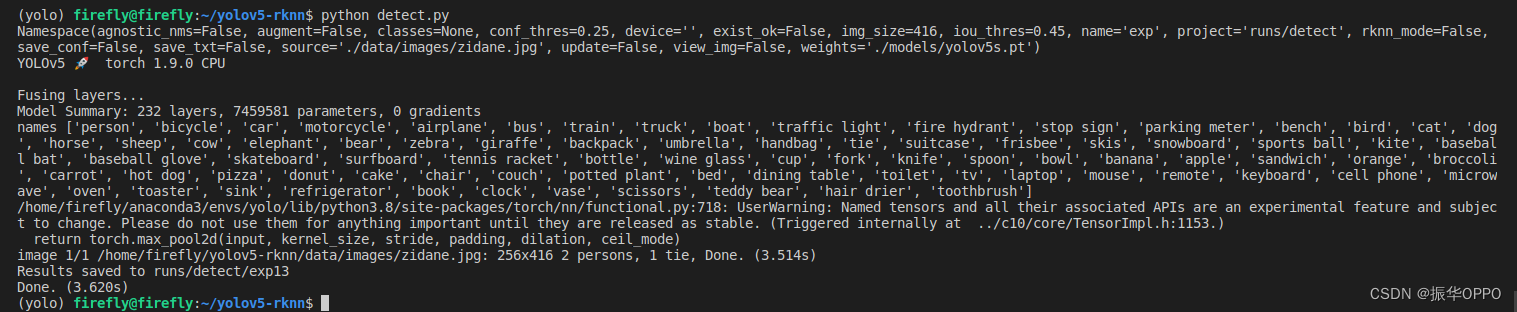

Attributeerror: can 't get attribute' sppf 'on < module' models. Common 'from' / home / yolov5 / Models / comm

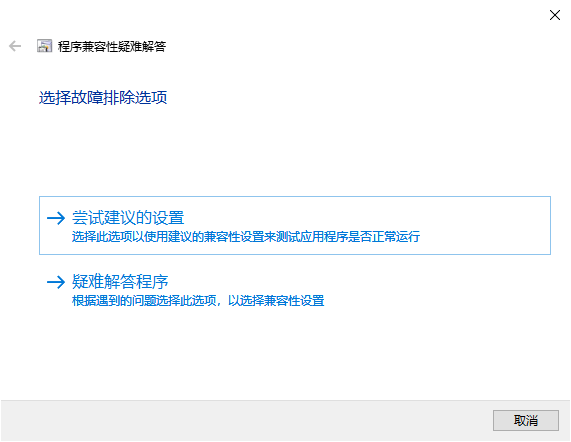

win10 64位装三菱PLC软件出现oleaut32.dll拒绝访问

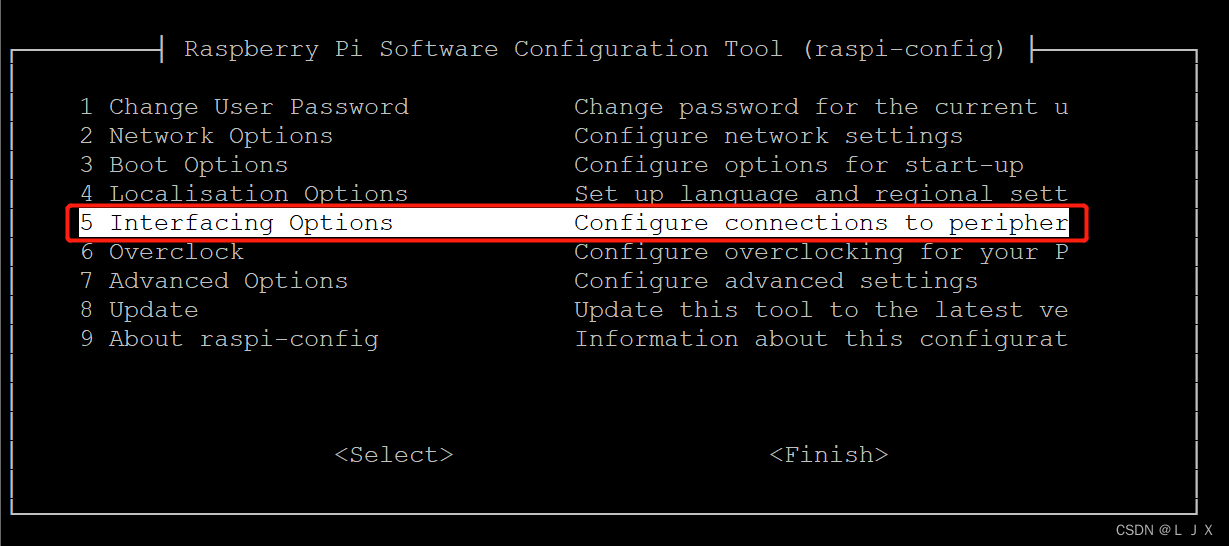

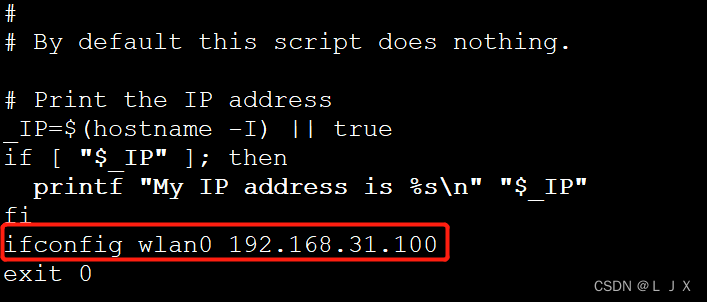

树莓派串口登录与SSH登录方法

Misc of BUU (update from time to time)

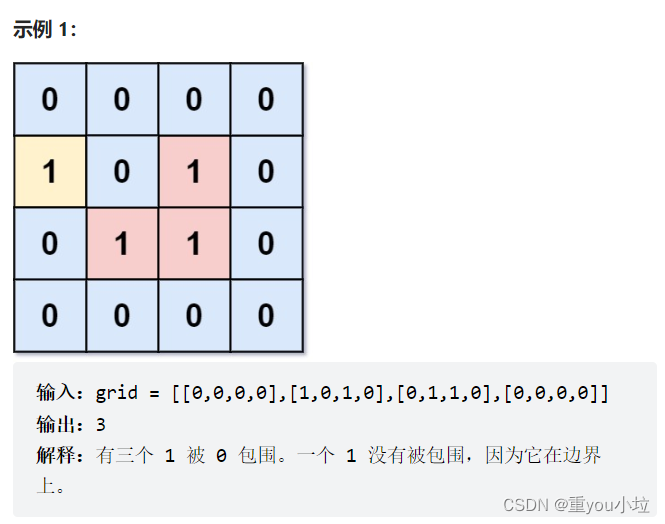

leetcode1020. 飞地的数量(中等)

Setting and using richview trvstyle template style

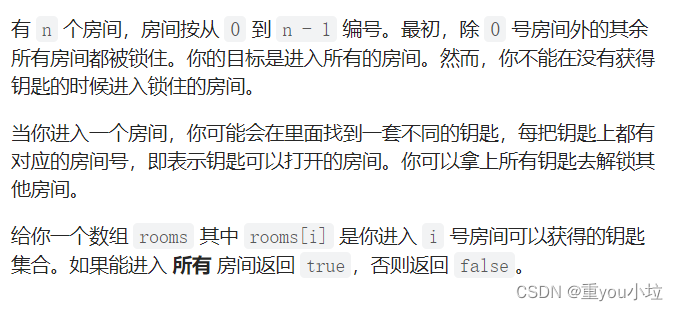

leetcode841. Keys and rooms (medium)

Configure raspberry pie access network

Cookie技术&Session技术&ServletContext对象

Blue Bridge Cup zero Foundation National Championship - day 20

随机推荐

网络安全基础介绍

supervisor 使用文档

C language_ Double create, pre insert, post insert, traverse, delete

JDBC学习笔记

指尖上的 NFT|在 G2 上评价 Ambire,有机会获得限量版收藏品

Short video, more and more boring?

BIO模型实现多人聊天

SEO学习的最好方式:搜索引擎

Uni app practical project

Introduction to ros2 installation and basic knowledge

Cookie Technology & session Technology & ServletContext object

Database basics exercise part 2

Hydra common commands

leetcode59. 螺旋矩阵 II(中等)

Bio model realizes multi person chat

Proteus -- Serial Communication parity flag mode

Leetcode59. spiral matrix II (medium)

idea控制台彩色日志

NFT on fingertips | evaluate ambire on G2, and have the opportunity to obtain limited edition collections

What does UDP attack mean? UDP attack prevention measures