当前位置:网站首页>Verilog tutorial (11) initial block in Verilog

Verilog tutorial (11) initial block in Verilog

2022-07-04 23:59:00 【mb611f1478c9b26】

List of articles

- Preface

- Text

- Grammar format

- initial What is the block used for ?

- initial When the block begins and when it ends ?

- How many... Are allowed in a module initial block ?

Preface

In a simulation, a set of Verilog sentence . These statements are placed in a block . stay Verilog There are two main types of blocks in –initial Block and always block .

Text

Grammar format

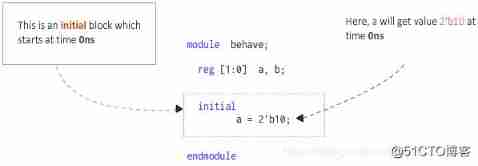

initial Block can be understood as an initialization block , stay initial The starting position of the statement in 0 The moment begins to execute , After that, if there is a delay , The next statement is executed after the delay .

The syntax is as follows :

initial

[single statement]

initial begin

[multiple statements]

end

- 1.

- 2.

- 3.

- 4.

- 5.

- 6.

If initial There are multiple statements in , Then place the begin …end Between .

initial What is the block used for ?

The initial block is not integrable , So it can't be converted into a hardware schematic with digital elements . Therefore, in addition to being used in simulation , It doesn't help much . These blocks are mainly used to initialize variables and design ports with specific values .

Be careful : In chip logic design ,initial Blocks really can only be used for behavioral simulation , But in FPGA In design , Simple use initial The initialization of variables can be integrated .

for example :

reg a, b, c;

initial begin

a = 0;

b = 0;

c = 0;

end

- 1.

- 2.

- 3.

- 4.

- 5.

- 6.

- 7.

But we initialize more at the moment of variable definition , This is the recommended usage .

for example :

reg a = 0;

- 1.

Or use a reset signal to initialize , But this will increase the burden of generic cabling , You can consciously reduce , Unless you have to .

for example :

- 1.

- 2.

- 3.

- 4.

- 5.

- 6.

- 7.

- 8.

initial When the block begins and when it ends ?

At the beginning of the simulation , In time 0 Unit starts an initial block . Throughout the simulation process , This block of code is executed only once . once initial All statements in the block are executed ,initial The execution of the block ends .

If initial There's just one sentence in the block , So the beginning is the end , The statement is executed to end this initial block , Such as :

The code shown in the figure below has an extra statement , It gives the signal b Assigned some values , But this only happens when the previous statement is executed 10 After units of time . It means a First assigned to a given value , And then in 10 After units of time ,b Assigned to 0.

How many... Are allowed in a module initial block ?

There can be multiple ( Arbitrarily )initial block .

Multiple initial Blocks are executed simultaneously , It's all from the moment 0 Start execution .

The code shown in the figure below has three initial blocks , All the initial blocks start and run in parallel at the same time . However , According to the statement and delay in each initial block , The time required to complete the block may vary .

$finish It's a Verilog System tasks , It tells the emulator to terminate the current simulation .

If the last block has 30 Time unit delay , As shown in the figure below , The simulation will be in 30 Time units end , So it killed all the others that were active at the time initial block .

initial begin

#30 $finish;

end

- 1.

- 2.

- 3.

Reference material

- WeChat official account : FPGA LAB

边栏推荐

- Financial markets, asset management and investment funds

- Enterprise application business scenarios, function addition and modification of C source code

- 微服务(Microservice)那点事儿

- C语言中sizeof操作符的坑

- ECCV 2022 | 腾讯优图提出DisCo:拯救小模型在自监督学习中的效果

- Remember to build wheels repeatedly at one time (the setting instructions of obsidian plug-in are translated into Chinese)

- 企业里Win10 开启BitLocker锁定磁盘,如何备份系统,当系统出现问题又如何恢复,快速恢复又兼顾系统安全(远程设备篇)

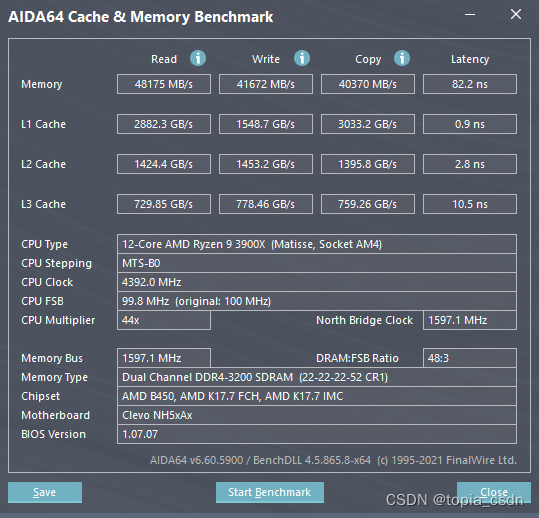

- Blue sky nh55 series notebook memory reading and writing speed is extremely slow, solution process record

- [path planning] RRT adds dynamic model for trajectory planning

- It's too convenient. You can complete the code release and approval by nailing it!

猜你喜欢

圖解網絡:什麼是網關負載均衡協議GLBP?

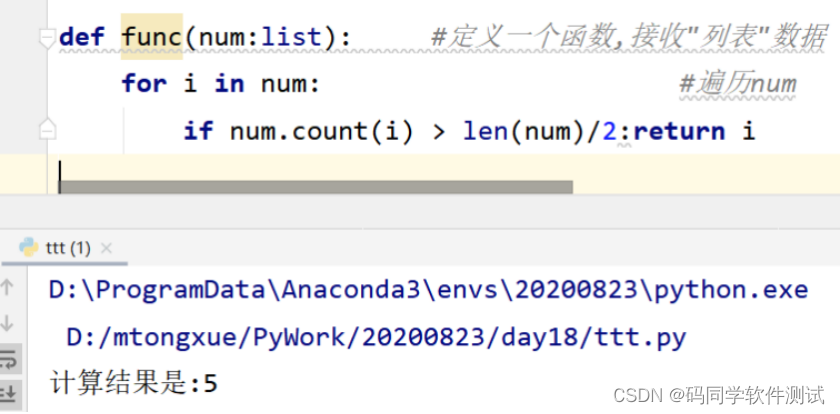

Tester's algorithm interview question - find mode

巩固表达式C# 案例简单变量运算

电力运维云平台:开启电力系统“无人值班、少人值守”新模式

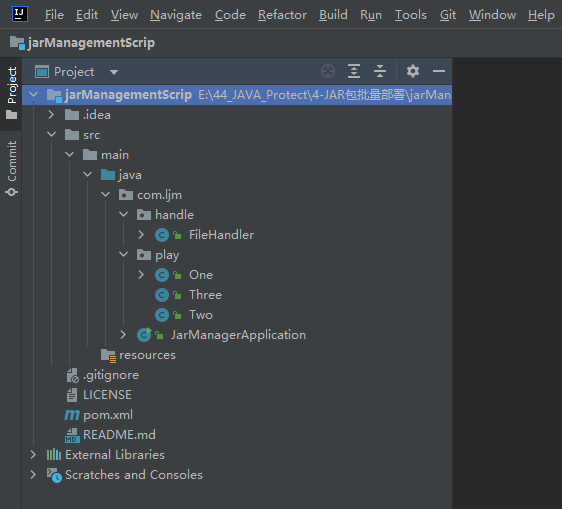

Jar批量管理小工具

What is the difference between port mapping and port forwarding

Blue sky nh55 series notebook memory reading and writing speed is extremely slow, solution process record

![[JS] - [sort related] - Notes](/img/b7/af467c7a169b73c3c4936072aef8b9.png)

[JS] - [sort related] - Notes

端口映射和端口转发区别是什么

45 year old professor, she threw two super unicorns

随机推荐

[IELTS reading] Wang Xiwei reading P3 (heading)

Expand your kubecl function

PMP certificate renewal process

Cross domain request

If you open an account of Huatai Securities by stock speculation, is it safe to open an account online?

C language to quickly solve the reverse linked list

雅思考试流程、需要具体注意些什么、怎么复习?

It's too convenient. You can complete the code release and approval by nailing it!

公司要上监控,Zabbix 和 Prometheus 怎么选?这么选准没错!

[paper reading] cavemix: a simple data augmentation method for brain vision segmentation

【监控】zabbix

C语言中sizeof操作符的坑

机器人强化学习——Learning Synergies between Pushing and Grasping with Self-supervised DRL (2018)

[monitoring] ZABBIX

MP advanced operation: time operation, SQL, querywapper, lambdaquerywapper (condition constructor) quick filter enumeration class

端口映射和端口转发区别是什么

挖财学院开户安全的吗?开户怎么开?

Advanced template

The caching feature of docker image and dockerfile

Application of fire fighting system based on 3D GIS platform