当前位置:网站首页>IC popular science article: those things about Eco

IC popular science article: those things about Eco

2022-07-05 20:30:00 【luoganttcc】

Many children's shoes should have been heard of ECO The term , Today we will talk about this .

I remember , I just worked for a short time , My elder martial brother of two years told me : Not repaired ECO Your life is incomplete . It didn't take long for my life to be complete , And he repaired more in half a year than in three years ECO. Yes, of course , There is a suspicion of boasting here , I'm not shy . As an engineer , You may have seen the agreement , Write algorithm , Verified , Run through the simulation , Rolled over FPGA. But if you put all bug all kill In the cradle , Have a good trip and enjoy yourself tapeout 了 , It's a little too smooth , What is missing in life .

Just like Wang Sicong might think what would happen if I didn't have so much money ( He really thinks so ?), As an engineer , You might think , If in the final stage , Find out bug What do I do ?

This is it. ECO What to do : Revise your later bug, Make up for your sins .

Here we are. , We need a brief introduction IC The design of the flow:

First of all, boss + The cattle have a meeting in the small black room , Discuss the general structure , Settle spec, Then front-end engineers write code . After writing the code, start to do verification simulation . When the simulation and verification are almost the same , Almost no longer can catch anything new bug 了 , Will enter RTL freeze Stage .

RTL freeze That is to say , From this day onwards , No one can modify RTL 了 .

RTL freeze It's a watershed . stay freeze Before , Your simulation is also good , Look at the code ,FPGA Verification is good , Anything found bug, Can be modified RTL Direct correction . however freeze after , By freeze Of RTL Will be integrated ,STA, Then send it to the back-end staff , do floor plan, Power supply integration , Clock synthesis , Layout and wiring, etc . These back-end processes are extremely time-consuming , And usually irreversible , That is to say , You let me do it again , The result cannot be guaranteed .

So here comes the question , If say , One day I found a bug, I asked the boss to revise RTL, At this time, back-end colleagues flow The synthesis has been completed ,floor plan And layout , It's the wiring stage . You can't say I put RTL Changed , Then synthesize it again , Let the back-end colleagues start from floor plan Start ? Be careful that a knife flies .

If bad luck , Tomorrow tapeout 了 , Are you going to change RTL, There is no time for you to do the whole back-end again flow?

No matter how bad your luck is , already tapeout 了 , The craft factory has just started its production line , Finished the lithography of the first mask , You tell them : stop ! I have another bug! From you to RTL To do ?

Of course, you can't start from RTL Start , I can't afford to waste time . It's hard for the backend to do convergence, and it can't afford to waste .

Fortunately, , You can use all the above ECO Get it done . from freeze To tapeout Between ECO It's called pre MASK Of ECO;tapeout after , Transistors that have finished processing chips , But I haven't done anything during transistor connection ECO be called post MASK Of ECO.

So-called ECO, Simply put, it means direct modification netlist.

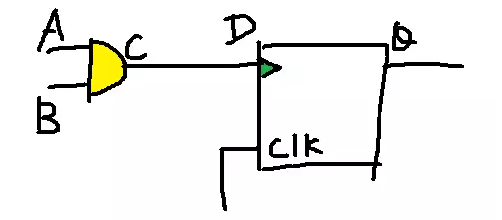

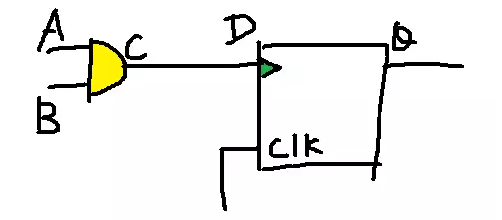

A simple example :

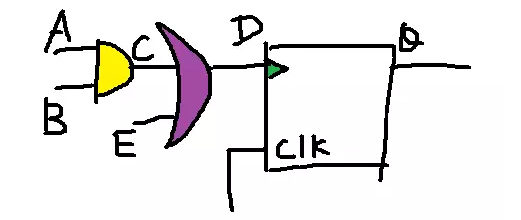

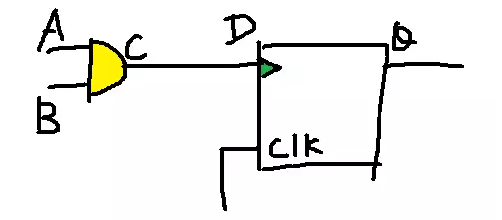

The following figure is a small part of the circuit diagram after synthesis :

It's written in RTL Namely : D = A & B;

If say , I found that this code has bug, I need to change it to : D = (A & B) | E;

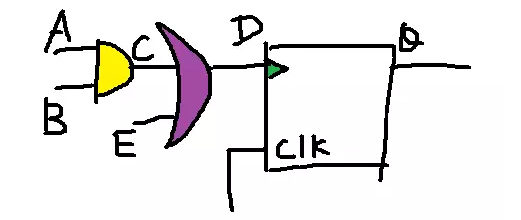

What shall I do? ? What you need to do is netlist Add an OR gate , Then put the... In the figure above C End and E End as input of or gate . The new circuit diagram is as follows :

How to realize this transformation ?

Back end tools have special CMD Support , You can use this CMD Write a script , The general content is as follows :

addcell AND;

connect C to AND.A1 port;

connect E to AND.A2 port;

connect AND.Z port to D;

Of course , This is just a sign , Actually CMD The form is not like this , But the mind is the same .

The above method only applies to pre MASK Of ECO, In this ECO Stage , You can add all kinds of cell. This fixes bug, There is no need to re integrate , It avoids the destruction of the achievements of each stage of the back end . Such as integrated power network , Clock tree , And the layout plan has not been destroyed . If you modify RTL, Then we must do synthesis again , And then from floor plan Start ......

here we are post MASK Stage ,ECO It becomes more difficult . Because at this time , The chip has tapeout, The craft factory has begun to process the base layer (base layer , That is, the transistor layer ), So at this point , There is no way to add cell, Like and door , Not gate , Registers, etc . But because of this time , Interconnection of chips (wire layer ) It has not been processed , therefore , You can change the interconnection of transistors .

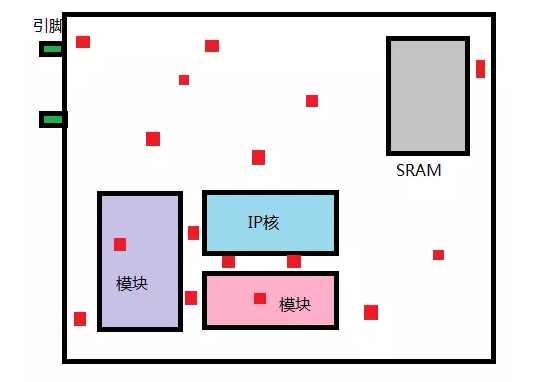

But you are not without cell It can be used , The actual chip is tapeout When , Will be in chip Sprinkle a lot of extra cell(redundant cell), these cell Scattered all over the place , To give post MASK ECO Make . As shown in the figure below , Red dots are scattered and redundant cell, They could be MUX, NAND gate , Or not ,buffer, Registers, etc :

It is also the part mentioned before ECO, stay post MASK Stage , If you can in these redundant cell Find an or door inside , And then C and E Change your connection , Connect to this or door , Then connect the output of or gate to the output of register D End , You can solve this bug. If bad luck , Cannot find or door , Maybe you have to think of another way , For example, find a NOR gate and a non gate , Then connect them in series to make an OR gate .

Yes, of course , At this stage , Because all cell The location and type of have been fixed , So the length of the connection cannot be changed ,cell The size is not up to you , It's likely that although you've finished repairing it bug, But with STA check Will find timing Unable to meet . But there is no way , I can only live as a dead horse doctor , Beg this path yes false path perhaps multicycle Well .

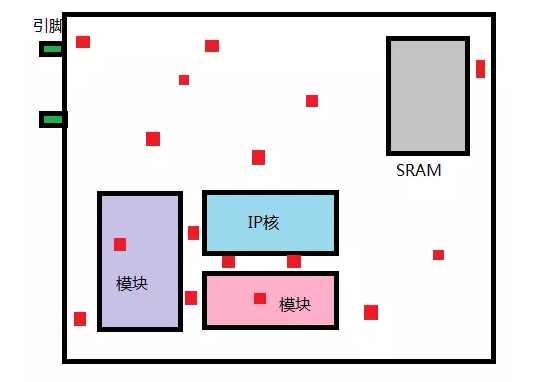

Finish repairing ECO, How to determine whether it has been repaired correctly ? This involves formal verification .

Front end personnel , finish writing sth. ECO CMD after , utilize ECO The command modifies the old netlist, Get new netlist, And then put this netlist And the modified RTL comparing , Make sure the two functions are the same , It is called formal verification . Here's the picture :

Formal verification has special EDA Tools to do , It can be used to compare two RTL Whether the function is the same , It can also be compared RTL And the integrated netlist Whether the function is the same , You can also compare two netlist Whether the function is the same . We won't go into details here .

What we need to understand is , Front end engineers need to modify netlist, We need to modify RTL, Then compare the two , Make sure the function is consistent . In this way, we can guarantee ECO The command completes the function you want .

Welcome to my WeChat official account. : Semi guidance society .

边栏推荐

- . Net distributed transaction and landing solution

- Scala基础【HelloWorld代码解析,变量和标识符】

- Some problems encountered in cocos2d-x project summary

- [C language] three implementations of quick sorting and optimization details

- 【数字IC验证快速入门】9、Verilog RTL设计必会的有限状态机(FSM)

- 【愚公系列】2022年7月 Go教学课程 004-Go代码注释

- sun. misc. Base64encoder error reporting solution [easy to understand]

- 银河证券在网上开户安全吗?

- 全国爱眼教育大会,2022第四届北京国际青少年眼健康产业展会

- Rainbow 5.7.1 supports docking with multiple public clouds and clusters for abnormal alarms

猜你喜欢

![[quick start of Digital IC Verification] 1. Talk about Digital IC Verification, understand the contents of the column, and clarify the learning objectives](/img/90/88a1f79a07016738d2688548e21949.png)

[quick start of Digital IC Verification] 1. Talk about Digital IC Verification, understand the contents of the column, and clarify the learning objectives

IC科普文:ECO的那些事儿

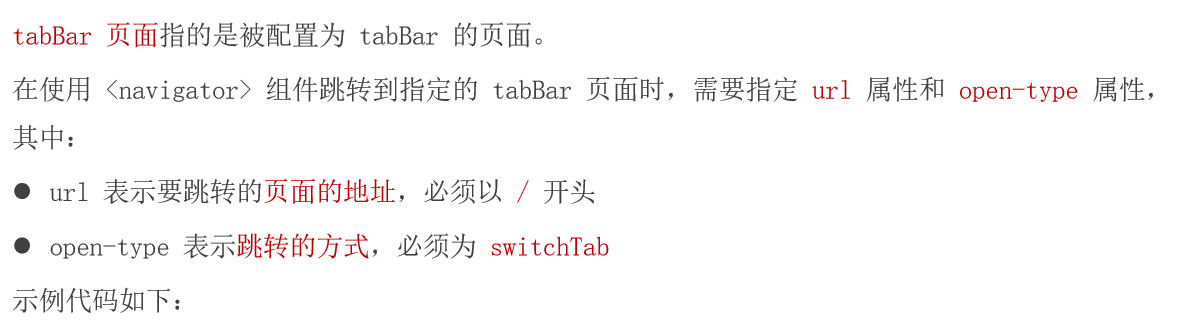

小程序页面导航

![[quick start of Digital IC Verification] 3. Introduction to the whole process of Digital IC Design](/img/92/7af0db21b3d7892bdc5dce50ca332e.png)

[quick start of Digital IC Verification] 3. Introduction to the whole process of Digital IC Design

14、Transformer--VIT TNT BETR

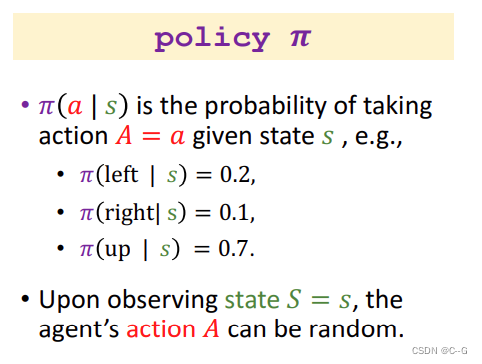

1. Strengthen learning basic knowledge points

无卷积骨干网络:金字塔Transformer,提升目标检测/分割等任务精度(附源代码)...

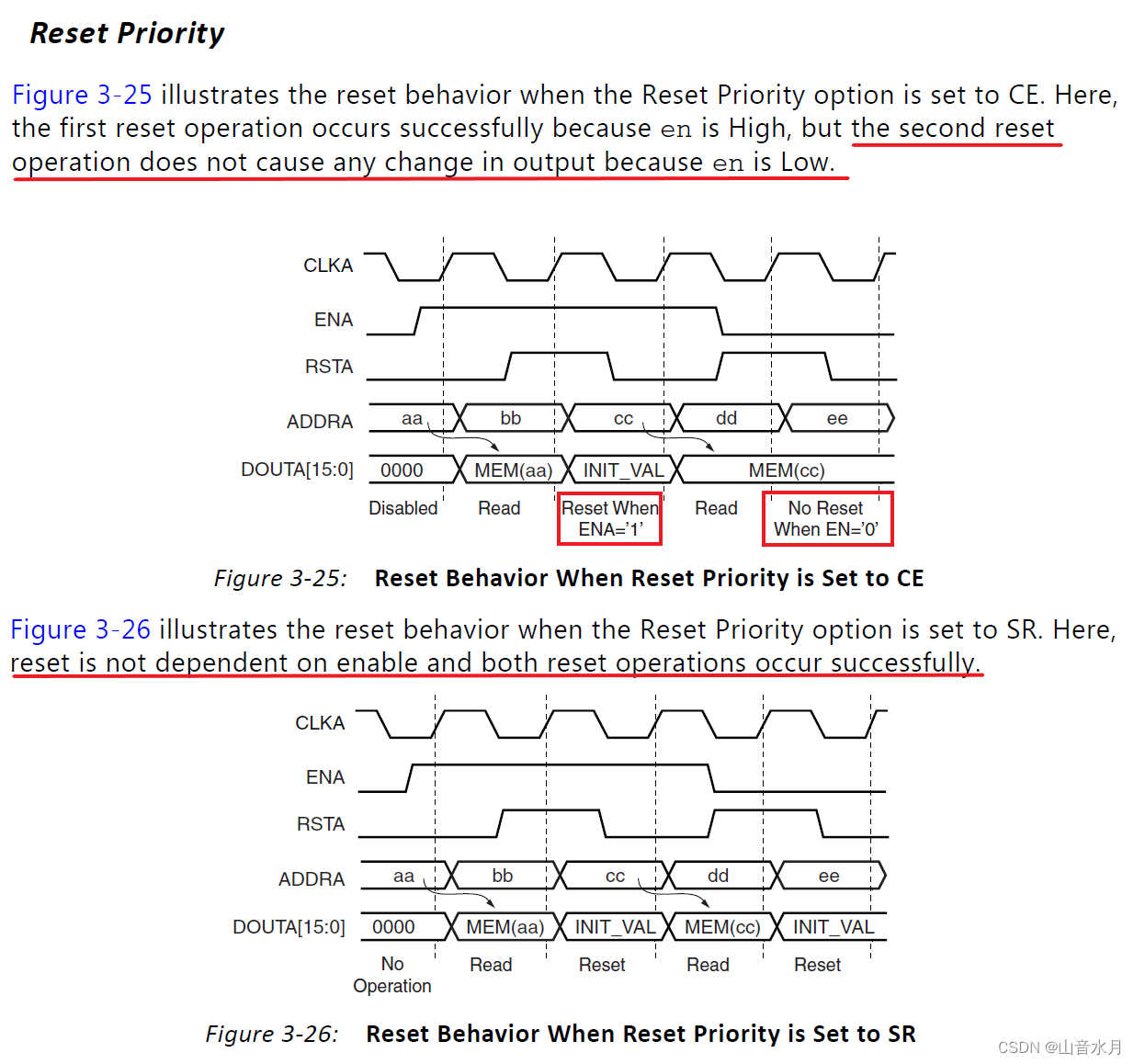

About the priority of Bram IP reset

Unity编辑器扩展 UI控件篇

Leetcode skimming: binary tree 17 (construct binary tree from middle order and post order traversal sequence)

随机推荐

Leetcode (695) - the largest area of an island

Introduction to dead letter queue (two consumers, one producer)

Schema和Model

解决php无法将string转换为json的办法

Propping of resources

A solution to PHP's inability to convert strings into JSON

Leetcode skimming: binary tree 16 (path sum)

如何形成规范的接口文档

全国爱眼教育大会,2022第四届北京国际青少年眼健康产业展会

ICTCLAS word Lucene 4.9 binding

. Net distributed transaction and landing solution

1: Citation;

USACO3.4 “破锣摇滚”乐队 Raucous Rockers - DP

【愚公系列】2022年7月 Go教学课程 004-Go代码注释

Informatics Olympiad 1337: [example 3-2] word search tree | Luogu p5755 [noi2000] word search tree

[record of question brushing] 1 Sum of two numbers

小程序项目结构

mongodb/文档操作

1、强化学习基础知识点

Leetcode (347) - top k high frequency elements