当前位置:网站首页>【FPGA教程案例9】基于vivado核的时钟管理器设计与实现

【FPGA教程案例9】基于vivado核的时钟管理器设计与实现

2022-07-05 00:49:00 【fpga和matlab】

---------------------------------------------------------------------------------------

1.软件版本

vivado2019.2

2.本算法理论知识

在上一课程,我们学习了基于计数器的时钟分频器,但是其实现的分频数是由限制的,而在FPGA设计过程中,往往需要一些特殊频率的时钟。采用基于计数器的分频器无法实现,此时需要通过vivado提供的时钟IP核来实现。在vivado的时钟IP核的配置,IP核名称为Clocking Wizard,直接在IP Catalog中搜索即可。

下面,我们通过Clocking Wizard实现几种不同频率的输出。

3.系统设计实现

在vivado中,新建如下IP核

边栏推荐

- 107. SAP UI5 OverflowToolbar 容器控件以及 resize 事件处理的一些细节介绍

- Ap8022 switching power supply small household appliances ACDC chip offline switching power supply IC

- URL和URI

- College degree, what about 33 year old Baoma? I still sell and test, and my monthly income is 13K+

- POAP:NFT的采用入口?

- P4408 [NOI2003] 逃学的小孩(树的直径)

- What you learned in the eleventh week

- [error reporting] "typeerror: cannot read properties of undefined (reading 'split')“

- 创新引领方向 华为智慧生活全场景新品齐发

- MySQL uses the explain tool to view the execution plan

猜你喜欢

Parsing of XML

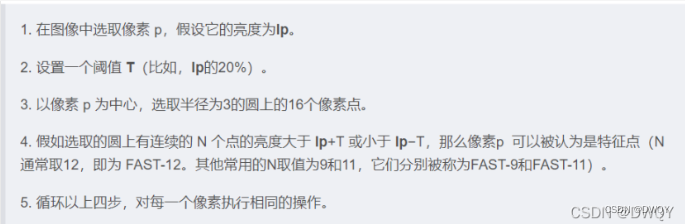

ORB(Oriented FAST and Rotated BRIEF)

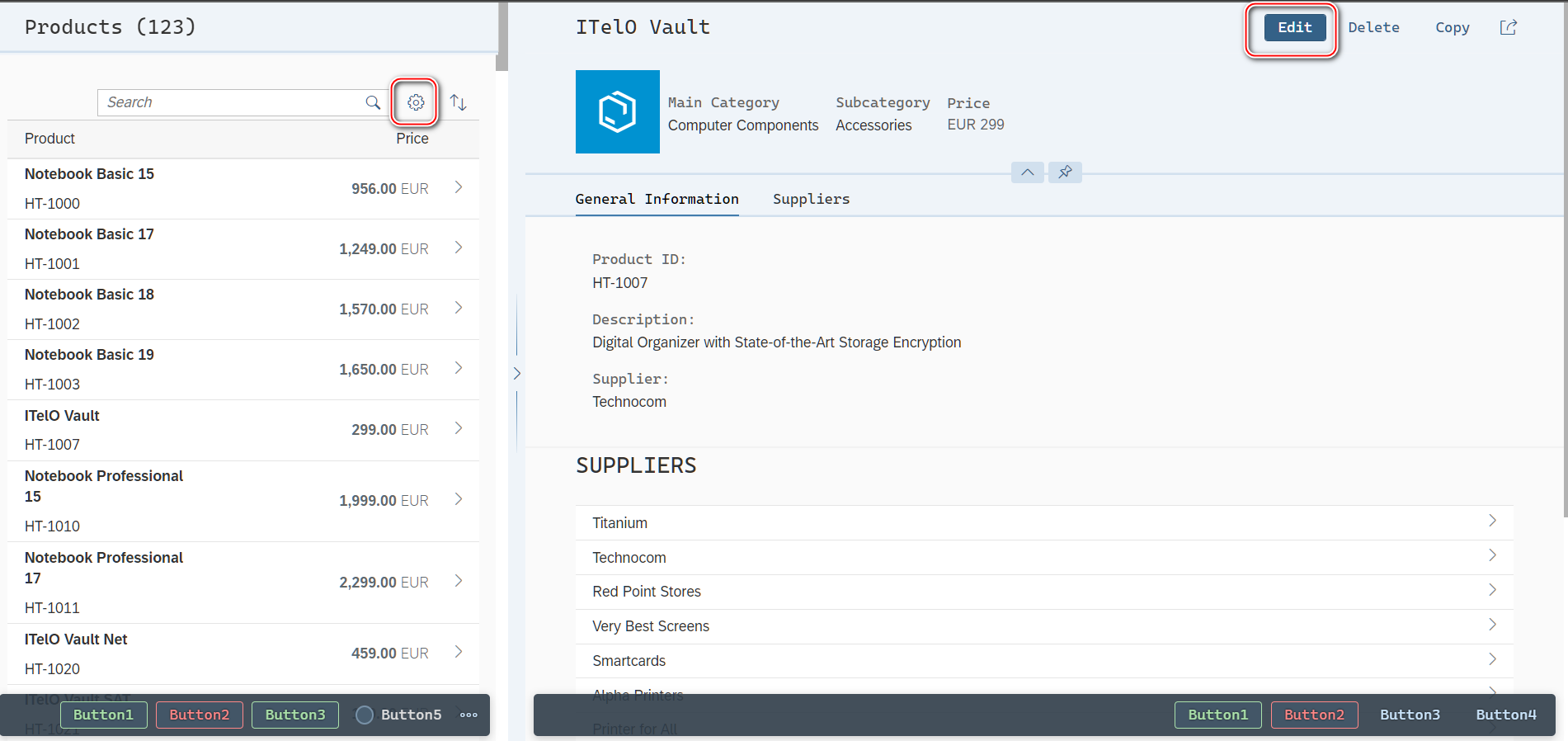

SAP ui5 application development tutorial 107 - trial version of SAP ui5 overflow toolbar container control introduction

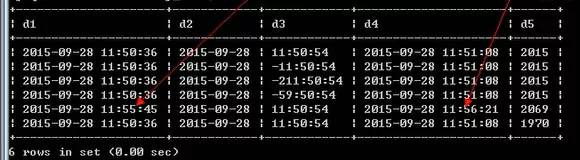

Date time type and format in MySQL

Fs8b711s14 electric wine bottle opener MCU IC scheme development special integrated IC

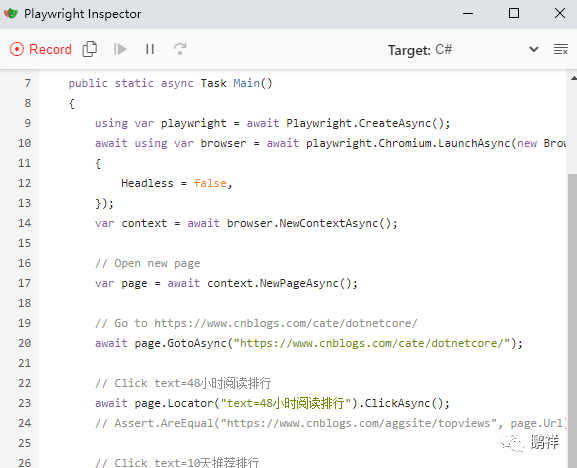

Playwright recording

Identifiers and keywords

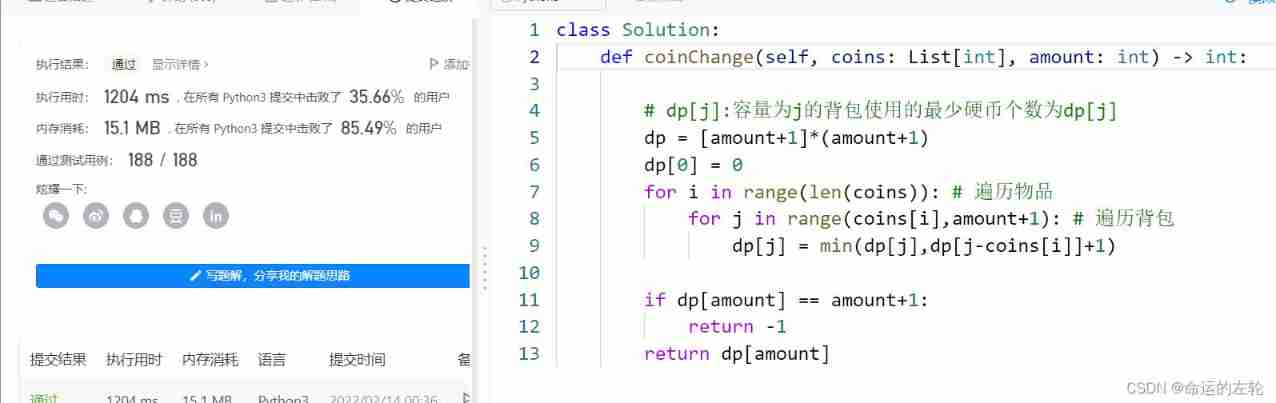

Leetcode70 (Advanced), 322

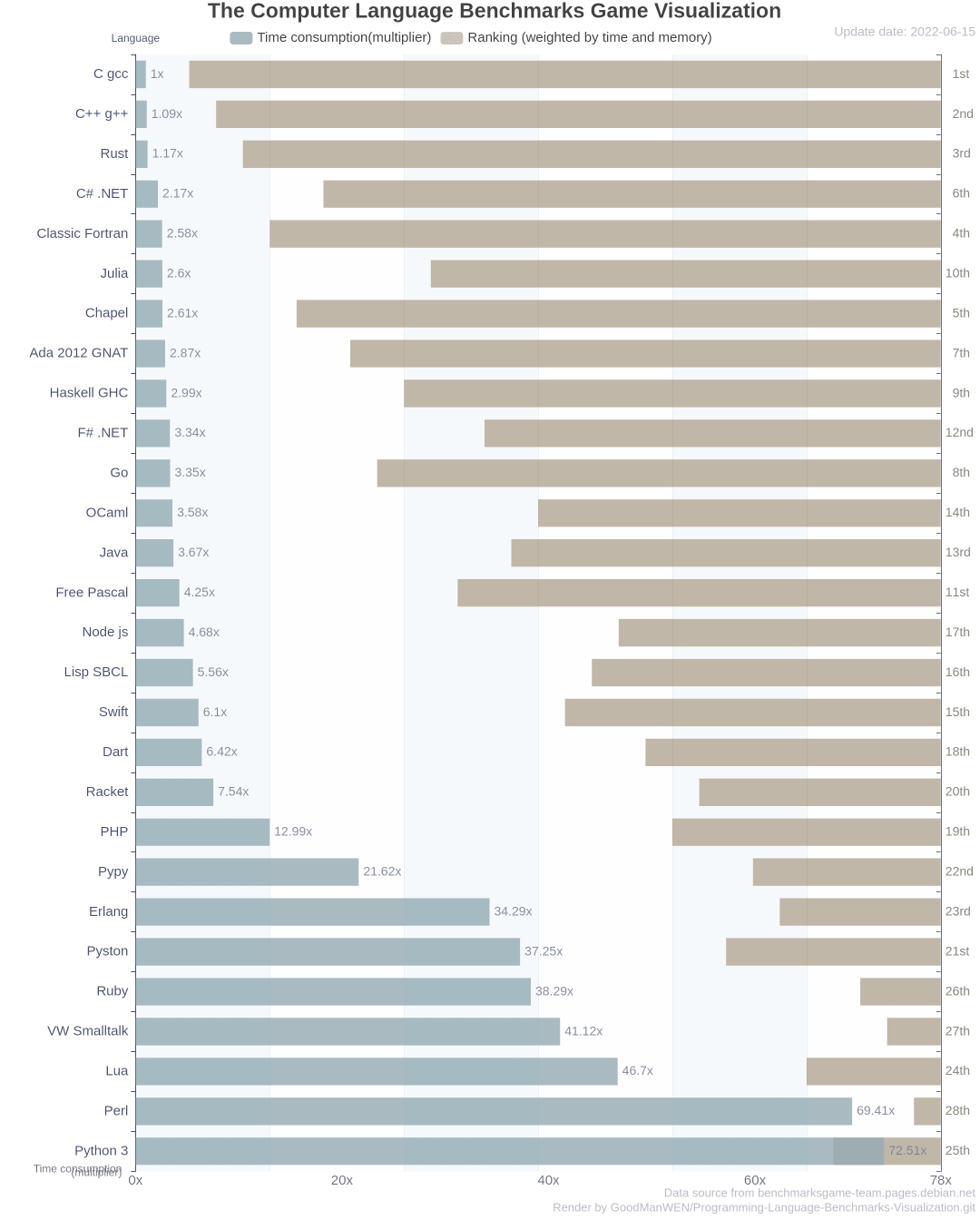

各大主流编程语言性能PK,结果出乎意料

What did I pay for it transfer to testing post from confusion to firmness?

随机推荐

Kibana index, mapping, document operation

MongoDB系列之学习笔记教程汇总

"Upside down salary", "equal replacement of graduates" these phenomena show that the testing industry has

GDB常用命令

Basic concept and usage of redis

Two numbers replace each other

Parsing of XML

User login function: simple but difficult

2022.07.03(LC_6108_解密消息)

Liangzai's first program life and annual summary in 2022

POAP:NFT的采用入口?

dotnet-exec 0.6.0 released

npm install报错 强制安装

2022.07.03 (LC 6109 number of people who know secrets)

[selenium automation] common notes

Binary conversion problem

2022.07.03 (lc_6111_counts the number of ways to place houses)

SAP ui5 application development tutorial 107 - trial version of SAP ui5 overflow toolbar container control introduction

Summary of the function and usage of const, volatile and restrict

4. Scala writes HelloWorld in idea, in-depth analysis of accompanying objects, and association of source packages