当前位置:网站首页>Design a clock frequency division circuit that can be switched arbitrarily

Design a clock frequency division circuit that can be switched arbitrarily

2022-07-05 08:04:00 【Chestnut flavor_ pupil】

IC The examination questions of the school recruitment pen : Design an arbitrary switch 1-8 The clock frequency division , Regardless of odd and even frequency division , The duty cycle of the clock is 50%.

One 、 Odd frequency division

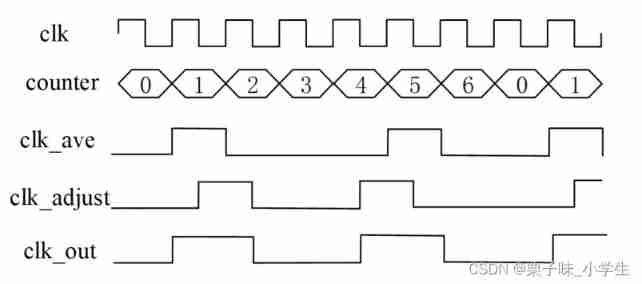

for example 7 frequency division , If the duty cycle is not required 50%, It's very simple to produce 3 individual cycle High level of ,4 individual cycle Low level of . If the required duty cycle is 50%, You need to make the following adjustments :

- The high level is divided by the rising edge of the source clock 3 individual cycle、 The low level is 4 individual cycle Of 7 Frequency division clock :clkp.

- Using the falling edge of the source clock to divide the frequency, the high level is 3 individual cycle、 The low level is 4 individual cycle Of 7 Frequency division clock :clkn.

- Two 7 The phase difference of the frequency division clock is half a clock cycle , take 2 Clock “ Or operation ”, The duty cycle is 50% Of 7 Frequency division clock .

Empathy N frequency division :

- When the rising edge of the source clock arrives , If the count value reaches (N-1)/2,clkp<=1; If the count value reaches (N-1),clkp<=0. produce 7 Frequency division clock clkp( The duty cycle is not 50%).

- When the falling edge of the source clock arrives ,clkn <= clkp, Generate relative clkp A clock that delays half a clock cycle clkn.

- take 2 Clock “ Or operation ”, The duty cycle is 50% Of 7 Frequency division clock div_clk.

Two 、 Even frequency division

Even frequency division can easily achieve a duty cycle of 50% Of N Frequency division clock :

- For frequency division coefficient N Cycle count , Reach the middle value of frequency division coefficient N/2 Turn the clock , It can ensure that the duty cycle of the clock after frequency division is 50%.

- The intermediate value of the frequency division coefficient can also be N/2 Cycle count .

3、 ... and 、 Half integer frequency division

Use the logic of the double edge of the clock , You can divide the clock by half an integer . But no matter how you adjust , The duty cycle of half integer frequency division cannot be 50%. There are many methods of half integer frequency division , Here is only a method similar to odd frequency division to adjust the duty cycle .

- For example, to 3.5 When multiplying and dividing , The counter cycles to 7, Respectively produced by 4 And 3 Composed of source clock cycles 2 A frequency division clock , namely clk_ave.

- For this 2 Adjust the frequency division clock with uneven cycles . One cycle count , The falling edge of the source clock is generated by 4 And 3 Composed of source clock cycles 2 A frequency division clock , namely clk_adj. Compared with the first generation 2 A clock with uneven cycles , This time 2 One clock phase, one delay and half source clock cycle , One half of the source clock cycle in advance .

- Carry out the clock generated twice " Or operation ", Then we can get periodic uniform 3.5 Multiple division clock , namely div_clk. The schematic diagram of frequency division waveform is as follows .

Four 、 Complete code

1. divf.v

module divf#(

parameter DIV_NUM = 5,//=============1-8 frequency division

parameter state = 0//================0: Odd number 1: even numbers 2: Semi integer

)

(

input clk,

input rstn,

output div_clk

);

reg [2:0] count;

reg clkp,clkn;// Odd numbers use

reg div_temp;// Even numbers use

reg clk_ave,clk_adj;// Semi integers use

[email protected](posedge clk or negedge rstn) begin

if(!rstn)

count <= 0;

else if(count == DIV_NUM -1)

count <= 0;

else

count <= count + 1;

end

case(state)

0:begin//========================= Odd frequency division

assign div_clk = clkp & clkn;

[email protected](posedge clk or negedge rstn) begin

if(!rstn)

clkp <= 0;

else if(count == DIV_NUM >> 1)

clkp <= 0;

else if(count == DIV_NUM - 1)

clkp <= 1;

end

[email protected](negedge clk or negedge rstn) begin

if(!rstn)

clkn <= 0;

else clkn <= clkp;

end

end

1: begin//========================== Even frequency division

assign div_clk = div_temp;

[email protected](posedge clk or negedge rstn) begin

if(!rstn)

div_temp <= 0;

else if((count == DIV_NUM/2-1) || (count == DIV_NUM -1))

div_temp <= ~div_temp;

end

end

2: begin//========================= Half integer frequency division

assign div_clk = clk_ave | clk_adj;

[email protected](posedge clk or negedge rstn) begin

if(!rstn)

clk_ave <= 0;

else if((count == 0) || (count == DIV_NUM/2 + 1))

clk_ave <= 1;

else

clk_ave <= 0;

end

[email protected](negedge clk or negedge rstn) begin

if(!rstn)

clk_adj <= 0;

else if((count == 1) || (count == DIV_NUM/2 + 1))

clk_adj <= 1;

else

clk_adj <= 0;

end

end

endcase

endmodule

2. divf_tb.v

`timescale 1ns/1ns

module divf_tb();

reg clk,rstn;

wire div_clk;

divf #(

.DIV_NUM(7),

.state(2)

)

U1(

.clk(clk),

.rstn(rstn),

.div_clk(div_clk)

);

initial begin

clk = 1'b0;

rstn = 1'b0;

#1 rstn =1'b1;

#50 $stop;

end

always #1

clk = ~clk;

endmodule

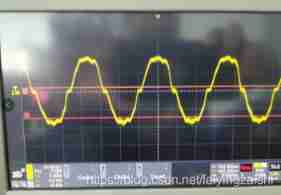

5、 ... and 、 Simulation waveform

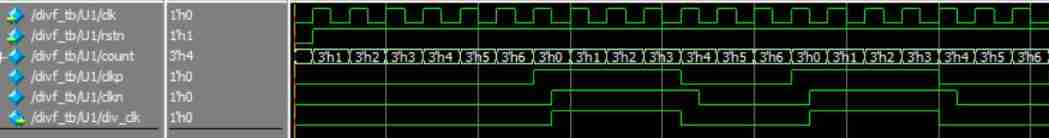

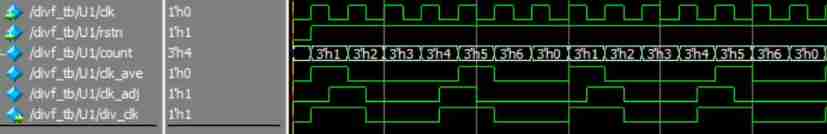

1. Odd frequency division :7 frequency division ,50%(DIV_NUM=7,state=0)

2. Even frequency division :8 frequency division ,50%(DIV_NUM=8,state=1)

3. Half integer frequency division :3.5 frequency division (DIV_NUM=7,state=2)

边栏推荐

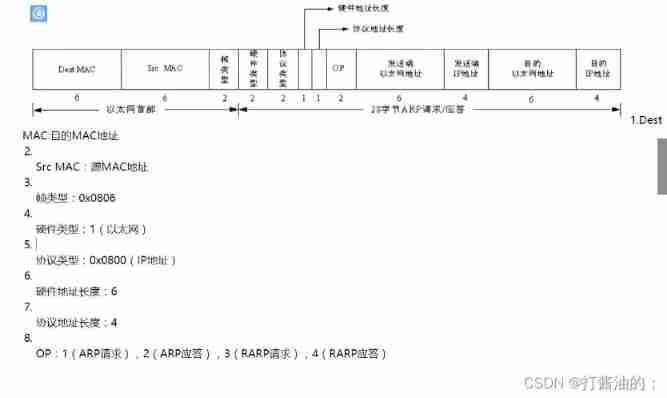

- Network communication model -- Network OSI tcp/ip layering

- Scm-05 basis of independent keyboard

- Global and Chinese markets of nano biosensors 2022-2028: Research Report on technology, participants, trends, market size and share

- Extended application of single chip microcomputer-06 independent key

- solver. Learning notes of prototxt file parameters

- Detailed explanation of pragma usage

- Basic embedded concepts

- 软件设计师:03-数据库系统

- About yolov3, conduct map test directly

- 生产中影响滑环质量的因素

猜你喜欢

随机推荐

Shape template matching based on Halcon learning [VII] reuse_ model. Hdev routine

Global and Chinese market for blood typing 2022-2028: Research Report on technology, participants, trends, market size and share

Hardware 3 -- function of voltage follower

C # joint configuration with Halcon

Carrier period, electrical speed, carrier period variation

Define in and define out

Improve lighting C program

Measurement fitting based on Halcon learning [II] meaure_ pin. Hdev routine

Basic embedded concepts

Development tools -- gcc compiler usage

Nb-iot technical summary

L'étude a révélé que le système de service à la clientèle du commerce électronique transfrontalier a ces cinq fonctions!

C WinForm [help interface - send email] - practice five

C language enhancement -- pointer

Ads learning record (lna_atf54143)

[trio basic tutorial 18 from introduction to proficiency] trio motion controller UDP fast exchange data communication

Sql Server的存儲過程詳解

LED display equipment records of the opening ceremony of the Beijing Winter Olympics

Global and Chinese market of urban rail connectors 2022-2028: Research Report on technology, participants, trends, market size and share

[trio basic tutorial 16 from introduction to proficiency] UDP communication test supplement