当前位置:网站首页>On the difference between FPGA and ASIC

On the difference between FPGA and ASIC

2022-07-07 05:48:00 【IC observer】

ASICer encounter FPGAer, The ass's lips are not to the horse's mouth .

ASIC still FPGA, This is a problem .

Many people feel that they are also writing Verilog Of , For front-end design ,FPGA and ASIC No difference , It's not , In a way , I think these are two industries .

Reset is different

because Xlinx Device reasons ,Xilinx High level reset is recommended , stay ASIC Usually it is low-level reset . I haven't heard of doing chip high-level reset .

Tool flow varies greatly

FPGA Most of the development is in Windows Development in environment , An editor , One Vivado You can go to the end , download bit Flow to the development board . One person's whole process .

ASIC Development is basically Linux Development in environment , For compilation VCS、debug use Veridi, clear lint/CDC/RDC use Splayglass, Collection coverage imc, Comprehensive use DC, Formal verification formality, Back end PR,DFT Until GDSII A series of tools . Need a complete team , To make a chip .

Code quality requirements differ

FPGA Development , Code verification finished , You can respond directly Vivado Self contained synthesis PR Lower the board to verify . Basically no problem .

ASIC Code verification finished , It needs to be removed lint. Because many writing methods are not comprehensive . Clear up lint, Enter comprehensive , but fomal Not necessarily , The code doesn't match the integrated netlist . comprehensive 、fomal however , No matter how well the code is written , Faster , No matter how well it is verified , You have to change it, too , rewrite .

ASIC The code of can be changed into FPGA IP, Direct release FPGA Verify on , but FPGA Your code wants to be streamed directly , There is still a long way to go .

FPGA Verification is also due to small scale , Rarely heard of using UVM Of . and FPGA Engineers usually design and test by themselves , Then debug yourself ,trace. One person, the whole process .FPGA Engineers basically do FPGA product . If someone regards chip verification as testing , It is the embodiment of ignorance .

ASIC Validation methodology UVM It's unified . The verification process is also very perfect ,testpoint、testcase、testplan,regression, Random , coverage , Post imitation . The verification at the system level is more about the design of software and hardware interactive verification , Accelerator verification, etc , Finally, I arrived at the top FPGA Prototype verification . and FPGA Basically, the interface is adjusted , Test software , Basically, I seldom find RTL Of bug.

They are called comprehensive /PR, But the essence is different

FPGA The internal structure is generally ,LUT Implement combinational logic ,D Trigger realizes sequential logic , Add some more BRAM, Hard core resources , Any circuit can be realized . therefore FPGA The synthesis of is to put RTL Map to these resources .

ASIC To sum up, we will RTL Map to the standard cell library ,mem. There are some RTL, Syntax is to support , But it just can't be integrated .LUT It's a big one mux, Nonsense code LUT Energy mapping , but DC Not necessarily .

FPGA Synthesis and ASIC Synthesis is not a thing at all .

FPGA stay ASIC The role of

FPGA stay ASIC Role in the development process , Just for prototype verification . The previous complex development process , And FPGA Compared with the self-contained development process, it is not an order of magnitude .

You use the method of making chips to do FPGA That's a dimensionality reduction blow , use FPGA How to make chips , That's putting the cart before the horse .

But the process of making chips is complicated , Put it to do FPGA Products , Waste of resources , How to kill a chicken .

Play differently

FPGA What are you playing , Yes, high flexibility , Unclear needs , Not much , Or the demand changes ,FPGA It comes in handy .

ASIC Play is to mass produce , The larger the quantity, the better . Needs are clear , Clear market positioning , It can be shipped continuously in the next few years .

Power waste

FPGA Product design pays little attention to power consumption , They are all boards used for plugging in electricity .

ASIC Low power design is also a set of design methodology , from RTL Design , To power gating,power domain The design of the ,upf To write . Low power consumption verification . The same circuit ,FPGA Power consumption will also be large .

area

If a product , Only small batch shipments , use FPGA Implementation will reduce costs . But if the product volume reaches the level of one million, it still needs FPGA, Don't let all the money Xilinx Make a . The code is large , use FPGA Difficult to achieve , The high cost of . The same circuit ,FPGA The area will be larger than ASIC Much larger

Generalists and professionals

FPGA Small scale , And it is directly oriented to products ,FPGA Engineers can produce the whole stack of engineers , The whole process of software and hardware covers . It's more interesting to directly face the product .

ASIC There are many design processes , Job breakdown , Everyone can only cover their own part of the work . Do algorithms IP The design of the , You may not need to pay attention to the middle-end implementation process , I don't even know what I'm doing IP Which product will be used . do IP Will produce experts , Focus on protocols or algorithms . and SOC Design is another methodology system .

FPGA In fact, it is similar to software

Think about it , Similar to doing software development , Code development verification completes the release , Then go to the development board to test . Problems arise , Come back and continue to change the code . The product is on the market , Found a bug, long-range OTA Make a patch , Upgrade .

ASIC You can't make a movie , Have a try , I'll ask you to try for tens of millions ? The products are in the hands of customers , Find out bug 了 , That's very serious , Recall . This batch is discarded .

Maybe that's why , You must be careful when making chips . Streaming failed , For many companies , Bankruptcy disaster .

Last

above , Various factors , It's caused FPGA and ASIC The whole R & D process system is different , So I think strictly speaking , do FPGA And do ASIC It's two industries .

You can pay more attention to ( Chip notation ) official account .

original text :https://mp.weixin.qq.com/s/QgmhX4DRSXW4yly9TJysPQ

边栏推荐

猜你喜欢

如何提高网站权重

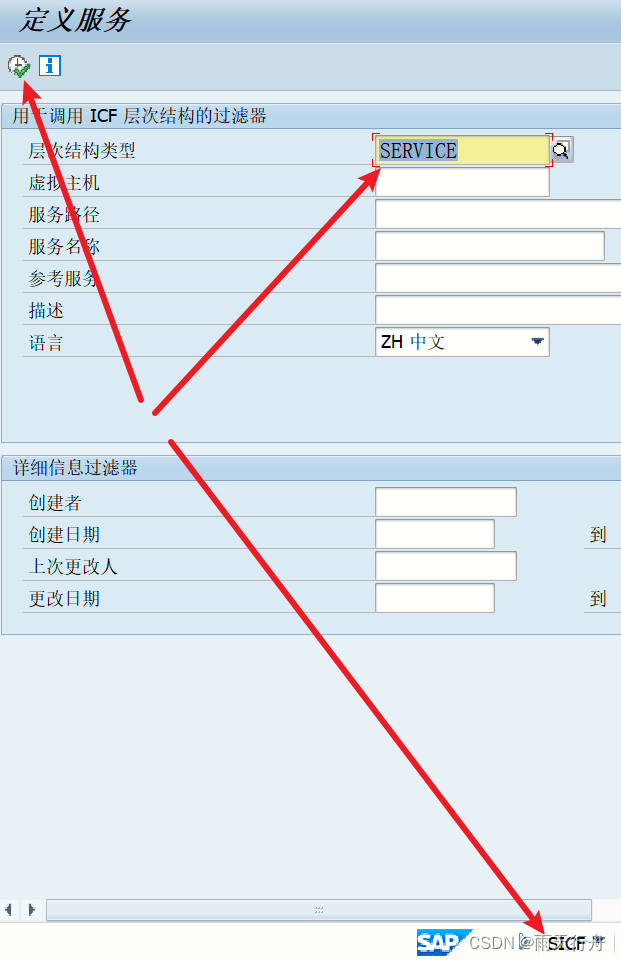

404 not found service cannot be reached in SAP WebService test

软件测试面试技巧

The year of the tiger is coming. Come and make a wish. I heard that the wish will come true

往图片添加椒盐噪声或高斯噪声

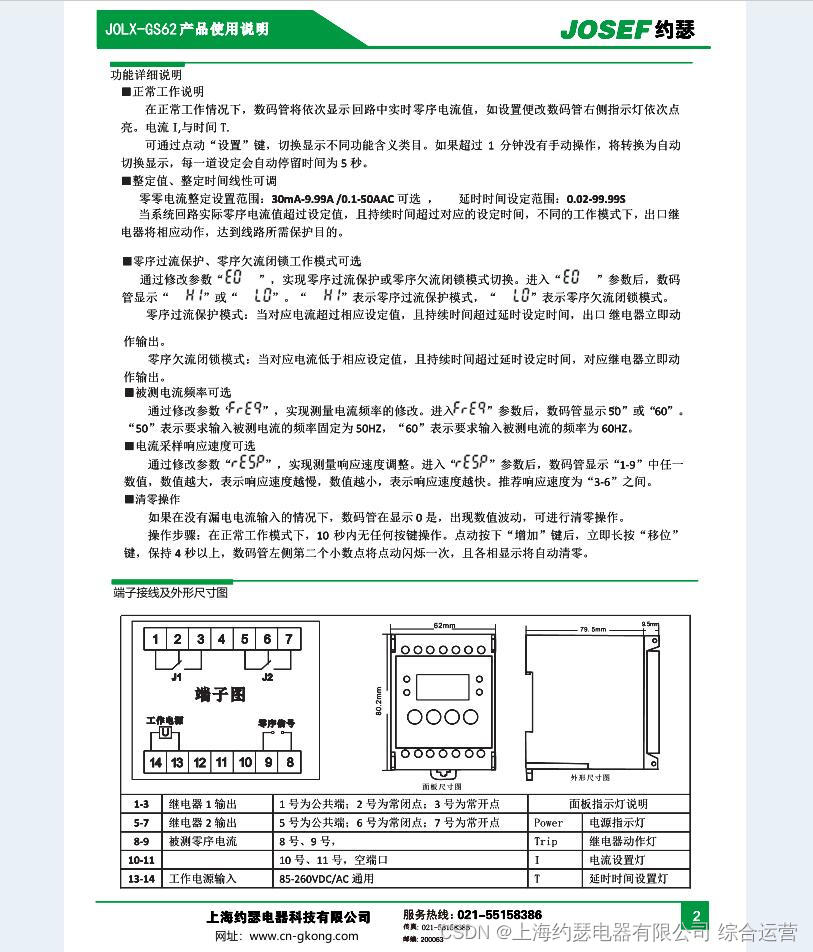

Zero sequence aperture of leakage relay jolx-gs62 Φ one hundred

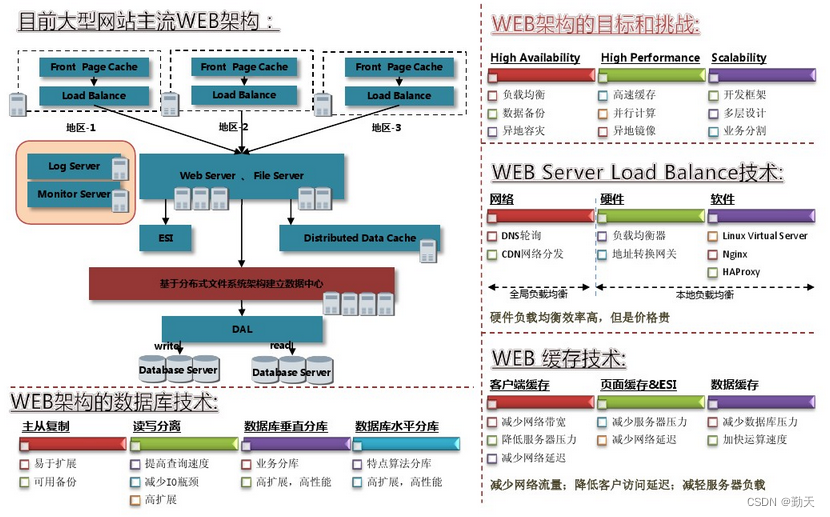

WEB架构设计过程

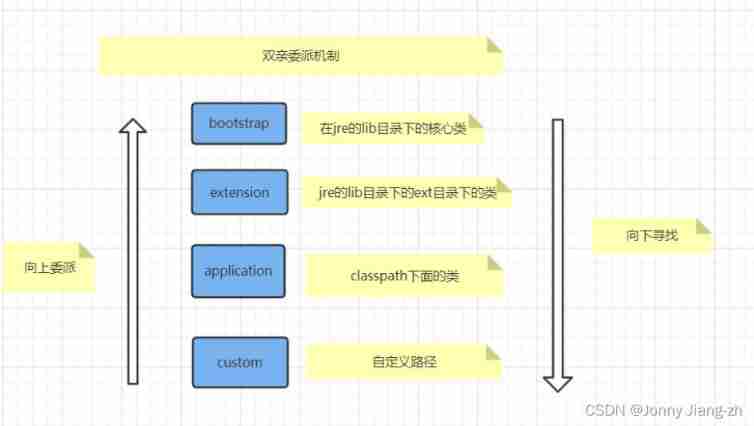

JVM the truth you need to know

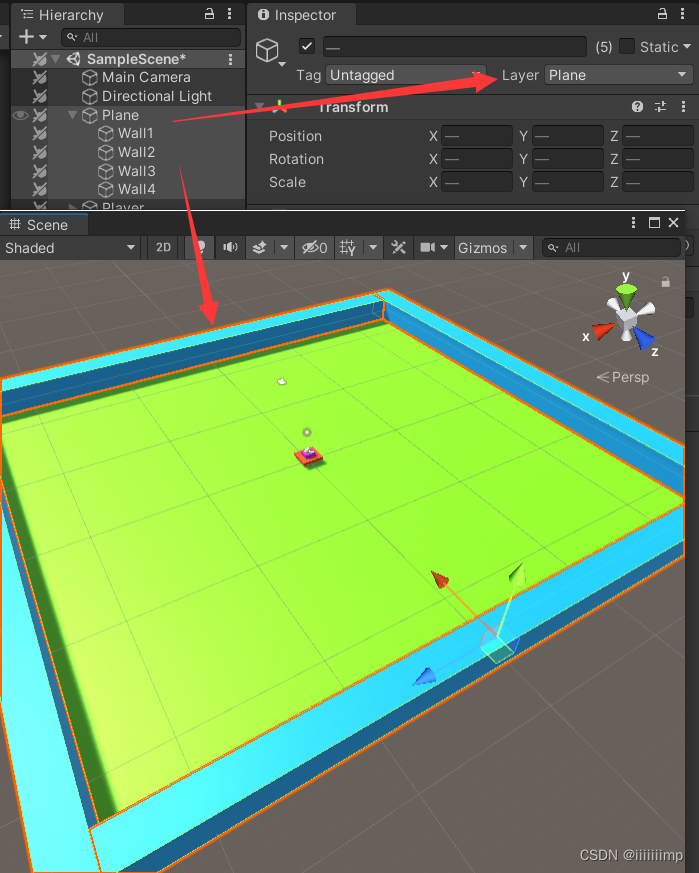

Unity keeps the camera behind and above the player

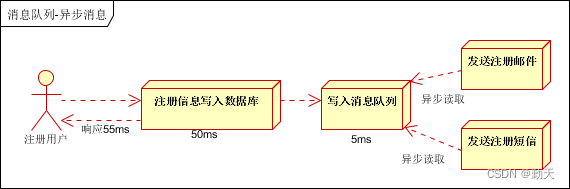

What is message queuing?

随机推荐

Reading the paper [sensor enlarged egocentric video captioning with dynamic modal attention]

分布式事务介绍

5. 数据访问 - EntityFramework集成

Getting started with DES encryption

Codeforces Round #416 (Div. 2) D. Vladik and Favorite Game

Message queue: how to handle repeated messages?

sql优化常用技巧及理解

Explication contextuelle du langage Go

Things about data storage 2

Forkjoin is the most comprehensive and detailed explanation (from principle design to use diagram)

C#可空类型

Nodejs get client IP

Digital innovation driven guide

得物客服一站式工作台卡顿优化之路

Paper reading [open book video captioning with retrieve copy generate network]

[论文阅读] Semi-supervised Left Atrium Segmentation with Mutual Consistency Training

Get the way to optimize the one-stop worktable of customer service

盘点国内有哪些EDA公司?

Go language context explanation

Différenciation et introduction des services groupés, distribués et microservices