当前位置:网站首页>u-boot in u-boot, dm-pre-reloc

u-boot in u-boot, dm-pre-reloc

2022-08-05 04:50:00 【IT Mr. Zhang】

关于u-boot中的u-boot,dm-pre-reloc

Devices that need to be bound before redirection need to be added to the device tree.This property must be declared in a child node of the root node.For example, the following node/amba/slcr/clkcThis property needs to be declared in all nodes,否则如果ambaNode does not declare this property,而slcrNodes that declare this property won't work either.

/* * Xilinx Zynq 7000 DTSI * Describes the hardware common to all Zynq 7000-based boards. * * Copyright (C) 2011 - 2015 Xilinx * * SPDX-License-Identifier: GPL-2.0+ */

/ {

#address-cells = <1>;

#size-cells = <1>;

compatible = "xlnx,zynq-7000";

cpus {

#address-cells = <1>;

#size-cells = <0>;

cpu0: [email protected]0 {

compatible = "arm,cortex-a9";

device_type = "cpu";

reg = <0>;

clocks = <&clkc 3>;

clock-latency = <1000>;

cpu0-supply = <®ulator_vccpint>;

operating-points = <

/* kHz uV */

666667 1000000

333334 1000000

>;

};

cpu1: [email protected]1 {

compatible = "arm,cortex-a9";

device_type = "cpu";

reg = <1>;

clocks = <&clkc 3>;

};

};

[email protected] {

compatible = "arm,cortex-a9-pmu";

interrupts = <0 5 4>, <0 6 4>;

interrupt-parent = <&intc>;

reg = < 0xf8891000 0x1000 0xf8893000 0x1000 >;

};

regulator_vccpint: fixedregulator {

compatible = "regulator-fixed";

regulator-name = "VCCPINT";

regulator-min-microvolt = <1000000>;

regulator-max-microvolt = <1000000>;

regulator-boot-on;

regulator-always-on;

};

amba: amba {

u-boot,dm-pre-reloc;

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <1>;

interrupt-parent = <&intc>;

ranges;

adc: [email protected] {

compatible = "xlnx,zynq-xadc-1.00.a";

reg = <0xf8007100 0x20>;

interrupts = <0 7 4>;

interrupt-parent = <&intc>;

clocks = <&clkc 12>;

};

can0: [email protected] {

compatible = "xlnx,zynq-can-1.0";

status = "disabled";

clocks = <&clkc 19>, <&clkc 36>;

clock-names = "can_clk", "pclk";

reg = <0xe0008000 0x1000>;

interrupts = <0 28 4>;

interrupt-parent = <&intc>;

tx-fifo-depth = <0x40>;

rx-fifo-depth = <0x40>;

};

can1: [email protected] {

compatible = "xlnx,zynq-can-1.0";

status = "disabled";

clocks = <&clkc 20>, <&clkc 37>;

clock-names = "can_clk", "pclk";

reg = <0xe0009000 0x1000>;

interrupts = <0 51 4>;

interrupt-parent = <&intc>;

tx-fifo-depth = <0x40>;

rx-fifo-depth = <0x40>;

};

gpio0: [email protected] {

compatible = "xlnx,zynq-gpio-1.0";

#gpio-cells = <2>;

#interrupt-cells = <2>;

clocks = <&clkc 42>;

gpio-controller;

interrupt-controller;

interrupt-parent = <&intc>;

interrupts = <0 20 4>;

reg = <0xe000a000 0x1000>;

};

i2c0: [email protected] {

compatible = "cdns,i2c-r1p10";

status = "disabled";

clocks = <&clkc 38>;

interrupt-parent = <&intc>;

interrupts = <0 25 4>;

reg = <0xe0004000 0x1000>;

#address-cells = <1>;

#size-cells = <0>;

};

i2c1: [email protected] {

compatible = "cdns,i2c-r1p10";

status = "disabled";

clocks = <&clkc 39>;

interrupt-parent = <&intc>;

interrupts = <0 48 4>;

reg = <0xe0005000 0x1000>;

#address-cells = <1>;

#size-cells = <0>;

};

intc: interrupt-[email protected] {

compatible = "arm,cortex-a9-gic";

#interrupt-cells = <3>;

interrupt-controller;

reg = <0xF8F01000 0x1000>,

<0xF8F00100 0x100>;

};

L2: cache-[email protected] {

compatible = "arm,pl310-cache";

reg = <0xF8F02000 0x1000>;

interrupts = <0 2 4>;

arm,data-latency = <3 2 2>;

arm,tag-latency = <2 2 2>;

cache-unified;

cache-level = <2>;

};

mc: memory-[email protected] {

compatible = "xlnx,zynq-ddrc-a05";

reg = <0xf8006000 0x1000>;

};

uart0: [email protected] {

compatible = "xlnx,xuartps", "cdns,uart-r1p8";

status = "disabled";

clocks = <&clkc 23>, <&clkc 40>;

clock-names = "uart_clk", "pclk";

reg = <0xE0000000 0x1000>;

interrupts = <0 27 4>;

};

uart1: [email protected] {

compatible = "xlnx,xuartps", "cdns,uart-r1p8";

status = "disabled";

clocks = <&clkc 24>, <&clkc 41>;

clock-names = "uart_clk", "pclk";

reg = <0xE0001000 0x1000>;

interrupts = <0 50 4>;

};

spi0: [email protected] {

compatible = "xlnx,zynq-spi-r1p6";

reg = <0xe0006000 0x1000>;

status = "disabled";

interrupt-parent = <&intc>;

interrupts = <0 26 4>;

clocks = <&clkc 25>, <&clkc 34>;

clock-names = "ref_clk", "pclk";

#address-cells = <1>;

#size-cells = <0>;

};

spi1: [email protected] {

compatible = "xlnx,zynq-spi-r1p6";

reg = <0xe0007000 0x1000>;

status = "disabled";

interrupt-parent = <&intc>;

interrupts = <0 49 4>;

clocks = <&clkc 26>, <&clkc 35>;

clock-names = "ref_clk", "pclk";

#address-cells = <1>;

#size-cells = <0>;

};

qspi: [email protected] {

clock-names = "ref_clk", "pclk";

clocks = <&clkc 10>, <&clkc 43>;

compatible = "xlnx,zynq-qspi-1.0";

status = "disabled";

interrupt-parent = <&intc>;

interrupts = <0 19 4>;

reg = <0xe000d000 0x1000>;

#address-cells = <1>;

#size-cells = <0>;

};

gem0: [email protected] {

compatible = "cdns,zynq-gem", "cdns,gem";

reg = <0xe000b000 0x1000>;

status = "disabled";

interrupts = <0 22 4>;

clocks = <&clkc 30>, <&clkc 30>, <&clkc 13>;

clock-names = "pclk", "hclk", "tx_clk";

#address-cells = <1>;

#size-cells = <0>;

};

gem1: [email protected] {

compatible = "cdns,zynq-gem", "cdns,gem";

reg = <0xe000c000 0x1000>;

status = "disabled";

interrupts = <0 45 4>;

clocks = <&clkc 31>, <&clkc 31>, <&clkc 14>;

clock-names = "pclk", "hclk", "tx_clk";

#address-cells = <1>;

#size-cells = <0>;

};

sdhci0: [email protected] {

compatible = "arasan,sdhci-8.9a";

status = "disabled";

clock-names = "clk_xin", "clk_ahb";

clocks = <&clkc 21>, <&clkc 32>;

interrupt-parent = <&intc>;

interrupts = <0 24 4>;

reg = <0xe0100000 0x1000>;

};

sdhci1: [email protected] {

compatible = "arasan,sdhci-8.9a";

status = "disabled";

clock-names = "clk_xin", "clk_ahb";

clocks = <&clkc 22>, <&clkc 33>;

interrupt-parent = <&intc>;

interrupts = <0 47 4>;

reg = <0xe0101000 0x1000>;

};

slcr: [email protected] {

u-boot,dm-pre-reloc;

#address-cells = <1>;

#size-cells = <1>;

compatible = "xlnx,zynq-slcr", "syscon", "simple-mfd";

reg = <0xF8000000 0x1000>;

ranges;

clkc: [email protected]100 {

u-boot,dm-pre-reloc;

#clock-cells = <1>;

compatible = "xlnx,ps7-clkc";

fclk-enable = <0>;

clock-output-names = "armpll", "ddrpll", "iopll", "cpu_6or4x",

"cpu_3or2x", "cpu_2x", "cpu_1x", "ddr2x", "ddr3x",

"dci", "lqspi", "smc", "pcap", "gem0", "gem1",

"fclk0", "fclk1", "fclk2", "fclk3", "can0", "can1",

"sdio0", "sdio1", "uart0", "uart1", "spi0", "spi1",

"dma", "usb0_aper", "usb1_aper", "gem0_aper",

"gem1_aper", "sdio0_aper", "sdio1_aper",

"spi0_aper", "spi1_aper", "can0_aper", "can1_aper",

"i2c0_aper", "i2c1_aper", "uart0_aper", "uart1_aper",

"gpio_aper", "lqspi_aper", "smc_aper", "swdt",

"dbg_trc", "dbg_apb";

reg = <0x100 0x100>;

};

rstc: [email protected]200 {

compatible = "xlnx,zynq-reset";

reg = <0x200 0x48>;

#reset-cells = <1>;

syscon = <&slcr>;

};

pinctrl0: [email protected]700 {

compatible = "xlnx,pinctrl-zynq";

reg = <0x700 0x200>;

syscon = <&slcr>;

};

};

dmac_s: [email protected] {

compatible = "arm,pl330", "arm,primecell";

reg = <0xf8003000 0x1000>;

interrupt-parent = <&intc>;

interrupt-names = "abort", "dma0", "dma1", "dma2", "dma3",

"dma4", "dma5", "dma6", "dma7";

interrupts = <0 13 4>,

<0 14 4>, <0 15 4>,

<0 16 4>, <0 17 4>,

<0 40 4>, <0 41 4>,

<0 42 4>, <0 43 4>;

#dma-cells = <1>;

#dma-channels = <8>;

#dma-requests = <4>;

clocks = <&clkc 27>;

clock-names = "apb_pclk";

};

devcfg: [email protected] {

compatible = "xlnx,zynq-devcfg-1.0";

interrupt-parent = <&intc>;

interrupts = <0 8 4>;

reg = <0xf8007000 0x100>;

clocks = <&clkc 12>, <&clkc 15>, <&clkc 16>, <&clkc 17>, <&clkc 18>;

clock-names = "ref_clk", "fclk0", "fclk1", "fclk2", "fclk3";

syscon = <&slcr>;

};

global_timer: [email protected] {

compatible = "arm,cortex-a9-global-timer";

reg = <0xf8f00200 0x20>;

interrupts = <1 11 0x301>;

interrupt-parent = <&intc>;

clocks = <&clkc 4>;

};

ttc0: [email protected] {

interrupt-parent = <&intc>;

interrupts = <0 10 4>, <0 11 4>, <0 12 4>;

compatible = "cdns,ttc";

clocks = <&clkc 6>;

reg = <0xF8001000 0x1000>;

};

ttc1: [email protected] {

interrupt-parent = <&intc>;

interrupts = <0 37 4>, <0 38 4>, <0 39 4>;

compatible = "cdns,ttc";

clocks = <&clkc 6>;

reg = <0xF8002000 0x1000>;

};

scutimer: [email protected] {

interrupt-parent = <&intc>;

interrupts = <1 13 0x301>;

compatible = "arm,cortex-a9-twd-timer";

reg = <0xf8f00600 0x20>;

clocks = <&clkc 4>;

};

usb0: [email protected] {

compatible = "xlnx,zynq-usb-2.20a", "chipidea,usb2";

status = "disabled";

clocks = <&clkc 28>;

interrupt-parent = <&intc>;

interrupts = <0 21 4>;

reg = <0xe0002000 0x1000>;

phy_type = "ulpi";

};

usb1: [email protected] {

compatible = "xlnx,zynq-usb-2.20a", "chipidea,usb2";

status = "disabled";

clocks = <&clkc 29>;

interrupt-parent = <&intc>;

interrupts = <0 44 4>;

reg = <0xe0003000 0x1000>;

phy_type = "ulpi";

};

watchdog0: [email protected] {

clocks = <&clkc 45>;

compatible = "cdns,wdt-r1p2";

interrupt-parent = <&intc>;

interrupts = <0 9 1>;

reg = <0xf8005000 0x1000>;

timeout-sec = <10>;

};

};

};

边栏推荐

- [BSidesCF 2019]Kookie

- [BJDCTF2020] EasySearch

- 【informix】解决启动报错大全,以及解决办法

- 【转】什么是etcd

- What is the function of industrial-grade remote wireless transmission device?

- [BSidesCF 2019] Kookie

- C language - vernacular to understand the original code, inverse code and complement code

- uboot开启调试打印信息

- [Nine Lectures on Backpacks - 01 Backpack Problems]

- [8.1] Code Source - [The Second Largest Number Sum] [Stone Game III] [Balanced Binary Tree]

猜你喜欢

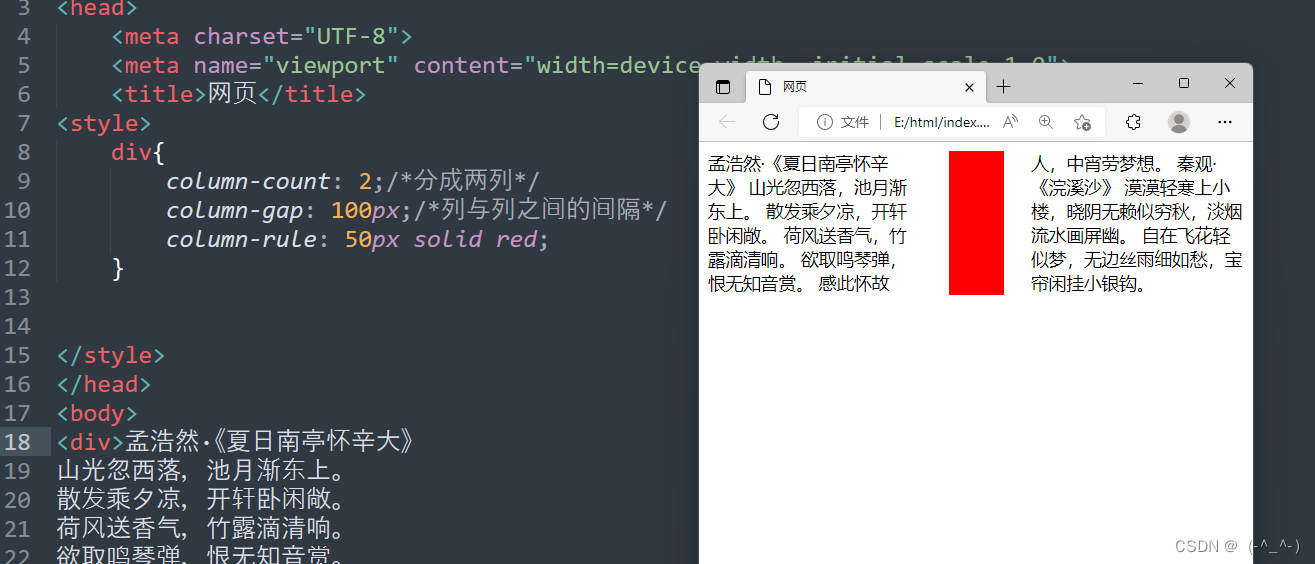

Visibility of multi-column attribute column elements: display, visibility, opacity, vertical alignment: vertical-align, z-index The larger it is, the more it will be displayed on the upper layer

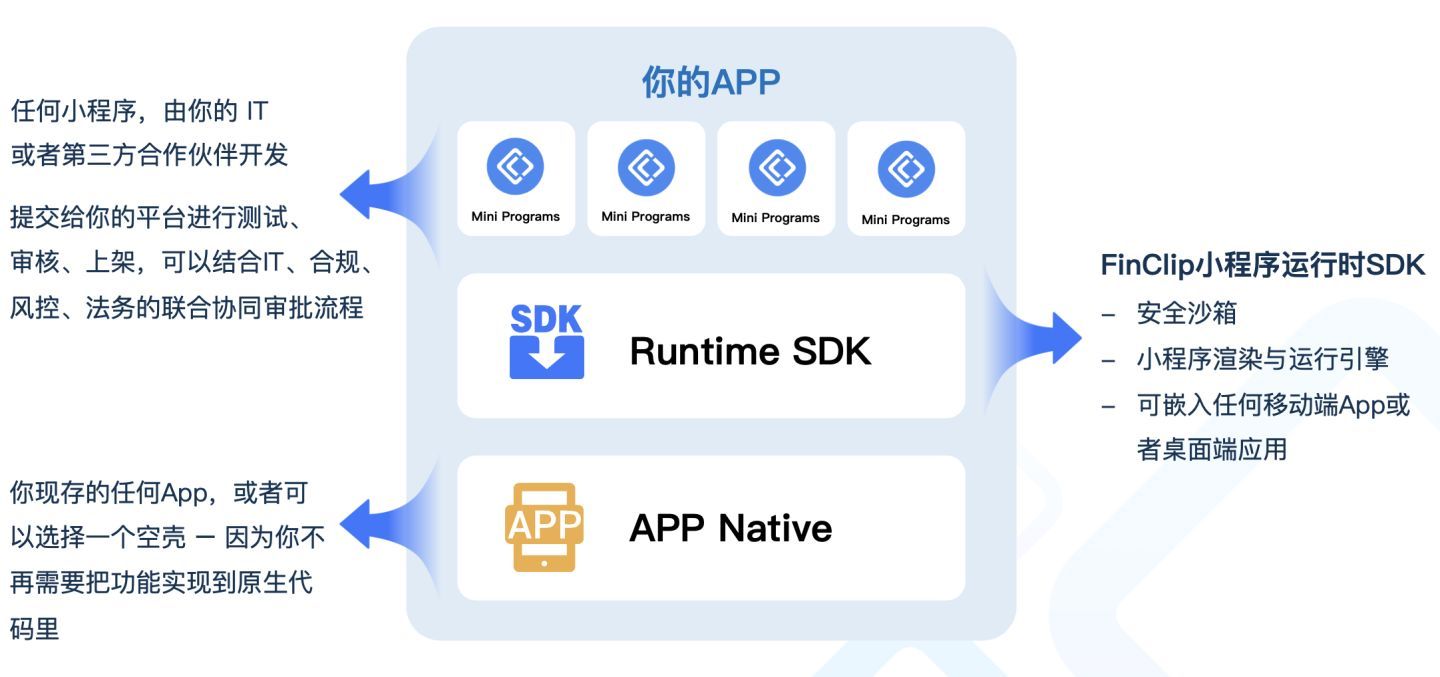

App快速开发建设心得:小程序+自定义插件的重要性

flink读取mongodb数据源

![[8.1] Code Source - [The Second Largest Number Sum] [Stone Game III] [Balanced Binary Tree]](/img/f3/0d92e22a424206241f4e1640f1bf6b.png)

[8.1] Code Source - [The Second Largest Number Sum] [Stone Game III] [Balanced Binary Tree]

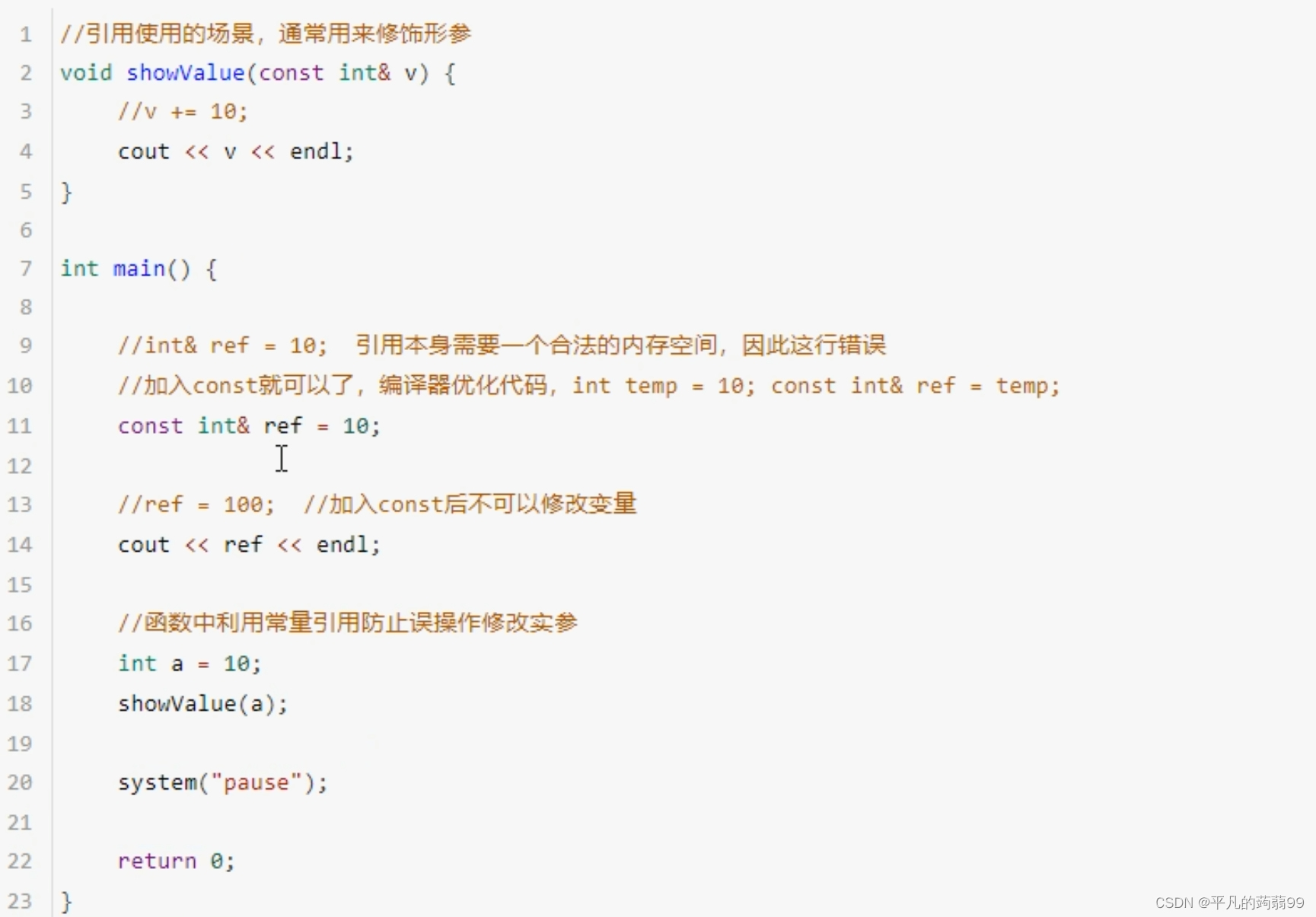

C++ core programming

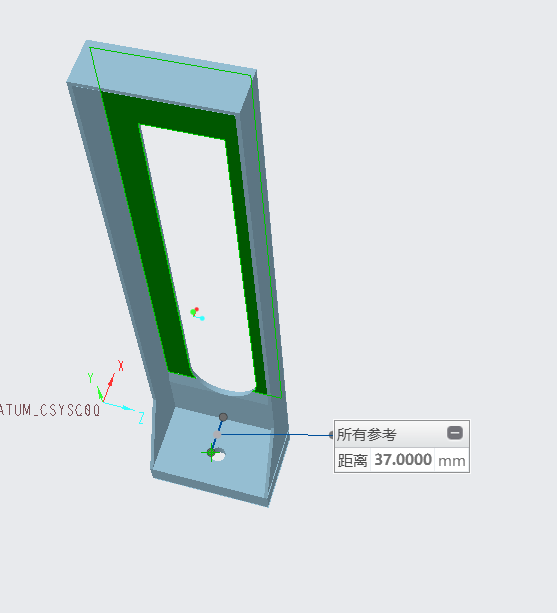

how to measure distance from point to face in creo

概率论的学习和整理8: 几何分布和超几何分布

![[BJDCTF2020]EasySearch](/img/60/464de3bcdda876171b9f61ad31bff1.png)

[BJDCTF2020]EasySearch

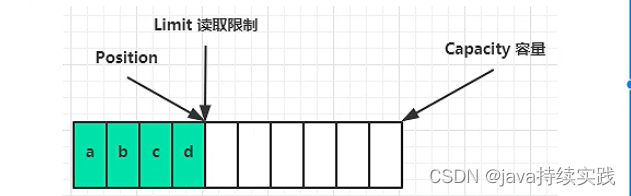

bytebuffer internal structure

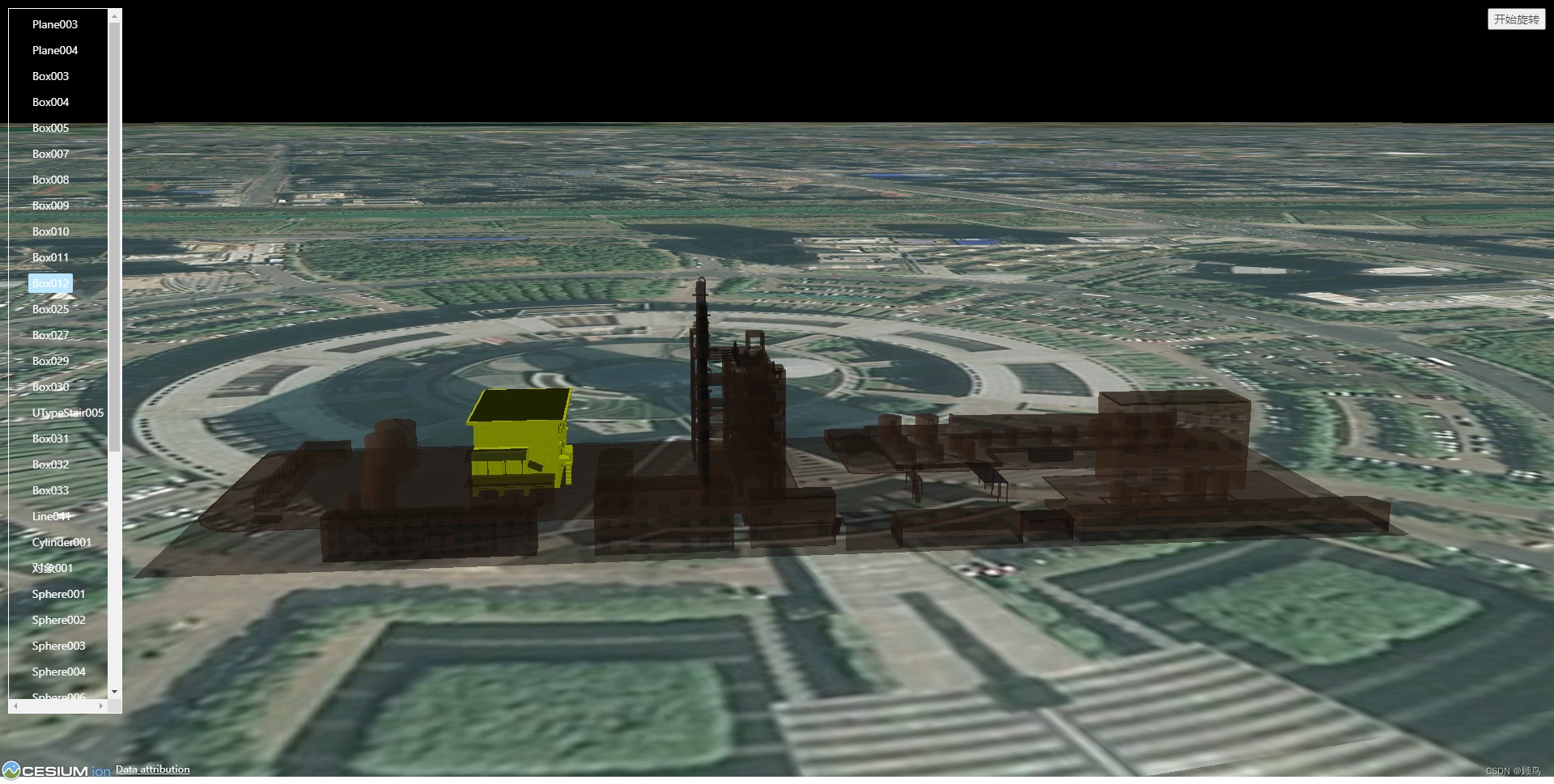

【cesium】元素高亮显示

随机推荐

About the installation of sklearn library

The log causes these pits in the thread block, you have to guard against

bytebuffer 内部结构

dedecms报错The each() function is deprecated

[informix] Resolving startup errors and solutions

[BJDCTF2020] EasySearch

u-boot调试定位手段

How to deal with DNS hijacking?

动力小帆船制作方法简单,电动小帆船制作方法

数字孪生技术在电力系统中的应用现状

Error creating bean with name ‘configDataContextRefresher‘ defined in class path resource

1007 Climb Stairs (贪心 | C思维)

[SWPU2019]Web1

The first performance test practice, there are "100 million" a little nervous

flink读取mongodb数据源

Why did you start preparing for the soft exam just after the PMP exam?

Flutter学习5-集成-打包-发布

特征预处理

Learning and finishing of probability theory 8: Geometric and hypergeometric distributions

C#关于set()和get()方法的理解及使用