当前位置:网站首页>FPGA基础篇目录

FPGA基础篇目录

2022-07-07 21:50:00 【晓晓暮雨潇潇】

疫情突如其来,打乱了原本波澜不惊的生活节奏。胡子头发自由生长,万千思绪信马由缰。饥一顿饿一顿一天还有一顿,坐一会躺一会一天又是一天。三个月日复一日,岁月一声不吭偷走了春天,羽绒也换成了半袖。解封数日,工作生活无缝衔接至另一种形式的按部就班,加了二十多天的班,终于把进度推进至老板可以接受的进度。整理了一下心情,把之前发的几篇FPGA的文章全部撤回了,准备重新写写FPGA。本文作为FPGA基础篇系列的第一篇文章,将筹划一下我将要写哪些东西,另外为这些FPGA基础篇相关的内容创建一个目录,方便自己也方便他人。最后被封三个月感慨颇多,写了一些话与镜子里的灵魂、与大家共勉。

目录

以一个字母代表一个系列,数字代表序列号。希望只有进阶的一天,没有完结的一天。

A——模电数电及FPGA内部结构等理论知识

B——verilog、VHDL、system verilog硬件描述语言相关知识

C——vivado、qiartus II、subline4、vscode、modelsim等开发工具

D——SPI、UART、IIC、USB2.0等常见低速接口

E——千兆网口、USB3.0、LVDS、Serdes等高速接口

F——LED、TFT、CMOS、SD卡、EEPROM、SDRAM、DDR3等常见硬件应用

G——xilinx常用IP核

内容

FPGA开发需要学习和了解的内容有很多。熟悉数字电路、模拟电路了解FPGA内部结构;熟悉verilog、VHDL硬件描述语言并掌握一些经典的示例;熟悉vivado、Quartus II等FPGA开发环境,subline4、vs code等文本编辑器,modelsim、matlab等仿真工具;学习时序约束的原理与如何让时序收敛的方法;学习常见的低速通信接口如UART、SPI、IIC等,学习常见的高速接口如USB3.0,千兆网口,DDR3等。最近几年又兴起的以Xilinx ZYNQ和ZYNQ Ultrasacle+系列为代表的异构处理芯片,集成了ARM与FPGA在一颗芯片上,与他相关的又涉及他的工具,开发流程等内容。计划在本基础篇中写工具、语言、基础理论知识、内部结构知识、xilinx的官方资料解读、常见通信接口、高速通信接口等内容。后续推出进阶篇,讲述相对复杂的时序约束,工具使用的进阶,以及基于基础篇通信接口测试的实用的小项目。关于ZYNQ则专门一个专栏讲述从基础到进阶的过程。2022年底之前,计划把FPGA基础篇精心打造,Qt篇把以前写好的几个想法发一下。关于FPGA更多是以xilinx的芯片为例,以vivado开发环境为例,以verilog语言为例,读者应该是能够点亮一个led的水平。从始至终将会提供经过验证的项目源码,更新的速度大约是一周一篇。

共勉

不会因为上天眷顾的缘分小鹿乱撞了,就像不会因为悄无声息的别离怅然失措。用命中注定的态度安慰事与愿违的努力,用事在人为的执着追求不期而遇的惊喜。只有这样才能在熙熙攘攘人来人往中收获一份恬淡,也只有这样才能不辜负现实泥潭中的灵魂摆渡。这是多年前经历刻骨铭心的断舍离后得到的感悟,如今想来,这样的平和适用于生活中的方方面面。与浩瀚苍穹相比不过是沧海之一粟,与时间永恒相比不过转瞬即逝,认清自己的渺小,才能唤起内心深处对世间万物的敬畏,这是重要的。

社会从某种意义上讲,就像一个生态系统,泥鳅黄鳝,苍蝇蚊子都得有,仿佛是维系动态平衡必要的存在。而之于个人,生活所触及的角落连接起来就是社会的缩影,就像明媚的阳光,不论洒在哪里都有光明与黑暗同在,只有懂得存在即合理,才能不去幻想只有光明的理想世界,才能不想着去逃离夹杂着黑暗的现实世界。很感慨用了生命中二十三年才晓得天下无乐土,付出了惨痛代价,好在现在,我常激励自己,然则天下无乐土,终不可有所为邪?

边栏推荐

- 解决:信息中插入avi格式的视频时,提示“unsupported video format”

- 数字藏品加速出圈,MarsNFT助力多元化文旅经济!

- What is ADC sampling rate (Hz) and how to calculate it

- Innovation today | five key elements for enterprises to promote innovation

- ArcGIS:矢量要素相同字段属性融合的两种方法

- 今日创见|企业促进创新的5大关键要素

- 【微服务|SCG】gateway整合sentinel

- 数据库每日一题---第22天:最后一次登录

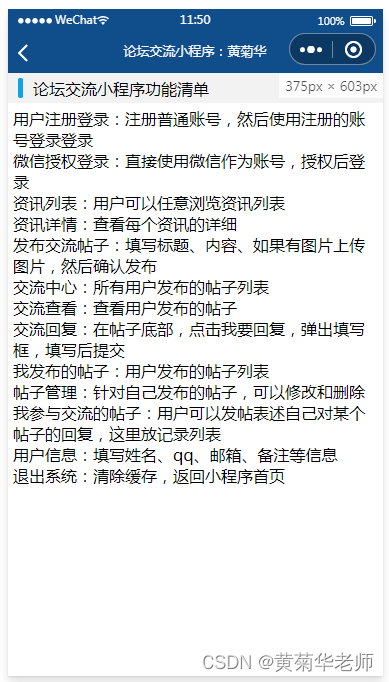

- 微信论坛交流小程序系统毕业设计毕设(6)开题答辩PPT

- 【刷题记录】3. 无重复字符的最长子串

猜你喜欢

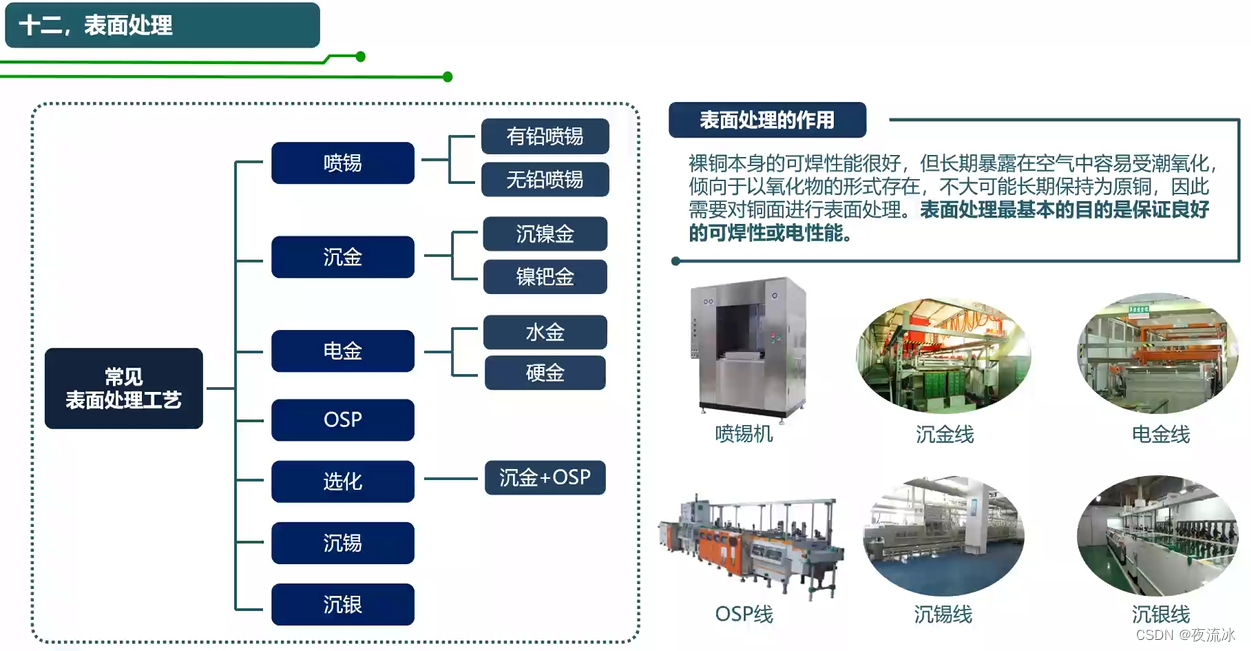

Knowledge drop - PCB manufacturing process flow

Microbial health network, how to restore microbial communities

微信论坛交流小程序系统毕业设计毕设(2)小程序功能

Microbial Health Network, How to restore Microbial Communities

Unity与WebGL的相爱相杀

Sword finger offer 28 Symmetric binary tree

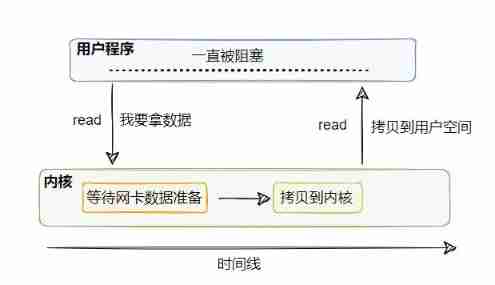

Transparent i/o model from beginning to end

微信论坛交流小程序系统毕业设计毕设(3)后台功能

线上面试,该如何更好的表现自己?这样做,提高50%通过率~

I wish you all the best and the year of the tiger

随机推荐

U盘拷贝东西时,报错卷错误,请运行chkdsk

2021-01-11

Network security sqlmap and DVWA explosion

Grid

Knowledge drop - PCB manufacturing process flow

网络安全-beef

嵌入式音频开发中的两种曲线

为什么市场需要低代码?

网络安全-联合查询注入

Online interview, how to better express yourself? In this way, the passing rate will be increased by 50%~

Network security - joint query injection

The author of LinkedList said he didn't use LinkedList himself

[untitled] reprint melting ice - track icedid server with a few simple steps

Transparent i/o model from beginning to end

Txt file virus

网络安全-对操作系统进行信息查询

数字藏品加速出圈,MarsNFT助力多元化文旅经济!

今日创见|企业促进创新的5大关键要素

Redhat下安装fedora

Unity dynamically merges mesh textures